图像感测设备

1.相关申请的交叉引用

2.本技术要求于2020年5月4日提交的韩国专利申请号10

‑

2020

‑

0053400的优先权,其公开内容通过引用以其整体并入本文。

技术领域

3.本文中描述的一个或多个实施例涉及一种图像感测设备。

背景技术:

4.图像感测设备可以基于对光起反应的半导体特性来捕获图像。图像感测设备可以大致分类为电荷耦合器件(ccd)图像感测设备和互补金属氧化物半导体(cmos)图像感测设备。因为cmos图像感测设备可以允许将模拟和数字控制电路两者直接实施在单个集成电路(ic)上,所以它们被广泛使用。

技术实现要素:

5.本公开的各种实施例涉及一种使下降的源电源的影响最小化的图像感测设备。

6.根据一个实施例,一种图像感测设备可以包括:第一在前比较器,适合于基于第一像素信号和斜坡信号生成第一在前比较信号;第一在后比较器,适合于在第一比较前提下将第一在前比较信号与第一参考信号进行比较,并且适合于生成与比较结果对应的第一在后比较信号;第二在前比较器,适合于基于第二像素信号和斜坡信号生成第二在前比较信号;以及第二在后比较器,适合于在不同于第一比较前提的第二比较前提下,将第二在前比较信号与第二参考信号进行比较,并且适合于生成与比较结果对应的第二在后比较信号。

7.第一比较前提可以包括用于将被输入有第一在前比较信号的输入端子初始化为第一电压电平的条件,并且第二比较前提可以包括用于将被输入有第二在前比较信号的输入端子初始化为第二电压电平的条件,第二电压电平不同于第一电压电平。

8.第一比较前提可以包括用于将第一参考信号的电压电平调节为第一电压电平的条件,并且第二比较前提可以包括用于将第二参考信号的电压电平调节为第二电压电平的条件,第二电压电平不同于第一电压电平。

9.第一在前比较器和第二在前比较器可以在相同的比较前提下操作。

10.根据一个实施例,一种图像感测设备可以包括:第一在前比较器,在初始化时间期间被初始化,并且适合于在行时间期间基于第一像素信号和斜坡信号生成第一在前比较信号;第一在后比较器,适合于在初始化时间期间,将第一输入端子初始化为第一电压电平并且将第一子输入端子初始化为默认电压电平,并且适合于在行时间期间,基于通过第一输入端子而输入的第一在前比较信号和通过第一子输入端子而输入的第一参考信号,来生成第一在后比较信号;第二在前比较器,在初始化时间期间被初始化,并且适合于在行时间期间基于第二像素信号和斜坡信号生成第二在前比较信号;以及第二在后比较器,适合于在初始化时间期间,将第二输入端子初始化为不同于第一电压电平的第二电压电平并且将第

二子输入端子初始化为默认电压电平,并且适合于在行时间期间,基于通过第二输入端子而输入的第二在前比较信号和通过第二子输入端子而输入的第二参考信号,来生成第二在后比较信号。

11.图像感测设备还可以包括:第一采样电路,耦合到第一在后比较器,并且适合于采样第一参考信号;以及第二采样电路,耦合到第二在后比较器,并且适合于采样第二参考信号。

12.第一在后比较器可以基于第一控制码信号通过自生成,来生成和调节第一参考信号,并且第二在后比较器可以基于第二控制码信号通过自生成,来生成和调节第二参考信号。

13.根据一个实施例,一种图像感测设备可以包括:第一在前比较器,在初始化时间期间被初始化,并且适合于在行时间期间基于第一像素信号和斜坡信号生成第一在前比较信号;第一在后比较器,适合于在初始化时间期间将第一参考信号的电压电平调节为第一电压电平,并且适合于在行时间期间基于第一在前比较信号和第一参考信号生成第一在后比较信号;第二在前比较器,在初始化时间期间被初始化,并且适合于在行时间期间基于第二像素信号和斜坡信号生成第二在前比较信号;以及第二在后比较器,适合于在初始化时间期间,将第二参考信号的电压电平调节为不同于第一电压电平的第二电压电平,并且适合于在行时间期间基于第二在前比较信号和第二参考信号生成第二在后比较信号。

14.图像感测设备还可以包括:第一采样电路,耦合到第一在后比较器,并且适合于采样第一参考信号;以及第二采样电路,耦合到第二在后比较器,并且适合于采样第二参考信号。

15.第一在后比较器可以基于第一控制码信号通过自生成,来生成和调节第一参考信号,并且第二在后比较器可以基于第二控制码信号通过自生成,来生成和调节第二参考信号。

附图说明

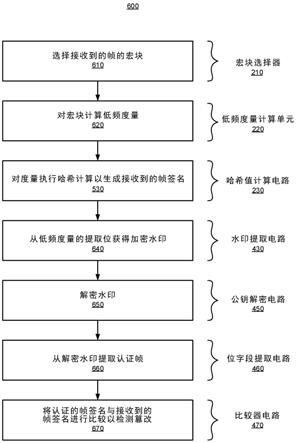

16.图1示出了图像感测设备的一个实施例。

17.图2示出了信号转换器的一个实施例。

18.图3示出了第一信号转换器中的第一比较电路的一个实施例。

19.图4示出了第一在后比较器的一个实施例。

20.图5示出了第二信号转换器中的第一比较电路的一个实施例。

21.图6示出了第一在后比较器的一个实施例。

22.图7示出了第三信号转换器中的第一比较电路的一个实施例。

23.图8示出了第一在后比较器的一个实施例。

24.图9示出了存储器的一个实施例。

25.图10示出了第一组的第一控制电路的一个实施例。

26.图11示出了第二组的第一控制电路的一个实施例。

27.图12示出了第三组的第一控制电路的一个实施例。

28.图13示出了用于图像感测设备的时序图的一个实施例。

29.图14和图15示出了用于图像感测设备的附加时序图。

具体实施方式

30.下面参考附图描述各种实施例,以便详细描述本公开,使得本公开所属领域的普通技术人员可以容易地实现本公开的技术精神。

31.将理解,当元件被称为“连接到”或“耦合到”另一元件时,该元件可以直接连接到或耦合到另一元件,或者利用插入在它们之间的一个或多个元件,电连接到或耦合到另一元件。另外,还将理解,当在本说明书中被使用时,术语“包括”和“包含”指定所述元件的存在,并且不排除一个或多个其他元件的存在或添加。在贯穿说明书的描述中,以单数形式描述一些组件,但是本公开不限于此,并且将理解,可以以复数形成组件。

32.图1是示出根据一个实施例的图像感测设备100的框图。

33.参考图1,图像感测设备100可以包括行控制器110、像素阵列120、斜坡信号生成器130、信号转换器140、全局计数器150和存储器160。

34.行控制器110可以生成用于控制每一行的像素阵列120的多个行控制信号ctrls。例如,行控制器110可以生成用于在第一行时间期间控制被布置在像素阵列120的第一行中的像素的第一行控制信号,并且可以生成用于在第二行时间期间控制被布置在像素阵列120的第二行中的像素的第二行控制信号。

35.像素阵列120可以包括以行和列布置的多个像素px。像素阵列120可以在行控制器110的控制下将每一行的多个像素信号vps输出到信号转换器140。例如,像素阵列120可以在第一行时间期间从被布置在第一行中的像素生成多个像素信号vps,并且可以在第二行时间期间从被布置在第二行中的像素生成多个像素信号vps。多个像素信号vps可以被称为多个第一像素信号vp1s、多个第二像素信号vp2s和多个第三像素信号vp3s。为了便于描述,将多个像素信号vps描述为被划分为三组,但是在另一实施例中,可以被划分为不同数目的组。

36.斜坡信号生成器130可以基于斜坡控制信号rp生成斜坡信号vr,斜坡信号vr具有针对每个行时间的设置模式。

37.信号转换器140可以基于多个第一像素信号vp1s、多个第二像素信号vp2s、多个第三像素信号vp3s、斜坡信号vr、以及第一至第三控制码信号cc1s、cc2s和cc3s,来生成多个比较信号vxs。多个比较信号vxs可以被称为多个在后比较信号vxs,或者多个比较信号vxs可以被称为多个第一在后比较信号vx1s、多个第二在后比较信号vx2s和多个第三在后比较信号vx3s。

38.例如,信号转换器140可以包括第一信号转换器a1、第二信号转换器a2和第三信号转换器a3。第一信号转换器a1可以基于多个第一像素信号vp1s、斜坡信号vr和第一控制码信号cc1s来生成多个第一在后比较信号vx1s。第二信号转换器a2可以基于多个第二像素信号vp2s、斜坡信号vr和第二控制码信号cc2s来生成多个第二在后比较信号vx2s。第三信号转换器a3可以基于多个第三像素信号vp3s、斜坡信号vr和第三控制码信号cc3s来生成多个第三在后比较信号vx3s。

39.全局计数器150可以生成针对每个行时间的一个或多个计数信号cnts。

40.存储器160可以基于针对每个行时间的多个第一在后比较信号vx1s、多个第二在后比较信号vx2s和多个第三在后比较信号vx3s,存储针对每一列的计数信号cnts,并且可以针对每个行时间生成多个数字信号douts。多个数字信号douts可以被称为多个第一数字

信号dout1s、多个第二数字信号dout2s和多个第三数字信号dout3s。

41.例如,存储器160可以包括第一存储器b1、第二存储器b2和第三存储器b3。第一存储器b1可以基于多个第一在后比较信号vx1s中的每个来存储计数信号cnts,并且可以输出所存储的计数信号作为多个第一数字信号dout1s。第二存储器b2可以基于多个第二在后比较信号vx2s中的每个来存储计数信号cnts,并且可以输出所存储的计数信号作为多个第二数字信号dout2s。第三存储器b3可以基于多个第三在后比较信号vx3s中的每个来存储计数信号cnts,并且可以输出所存储的计数信号作为多个第三数字信号dout3s。

42.图2是示出信号转换器140的一个实施例的框图,该信号转换器140可以包括第一信号转换器a1、第二信号转换器a2和第三信号转换器a3。

43.第一信号转换器a1可以基于多个第一像素信号vp1s、斜坡信号vr和第一控制码信号cc1s来生成多个第一在后比较信号vx1s。例如,第一信号转换器a1可以包括多个比较电路a11至a1n。多个比较电路a11至a1n可以共同接收斜坡信号vr和第一控制码信号cc1s,可以接收多个第一像素信号vp1s之中的对应像素信号,并且可以分别生成多个第一在后比较信号vx1s。

44.例如,多个比较电路a11至a1n之中的第一比较电路a11可以基于多个第一像素信号vp1s之中的第一像素信号vp11、第一控制码信号cc1s和斜坡信号vr,来生成第一在后比较信号vx1s中的第一在后比较信号vout11。多个比较电路a11至a1n之中的第n比较电路a1n可以基于多个第一像素信号vp1s之中的第n像素信号vp1n、第一控制码信号cc1s和斜坡信号vr,来生成第一在后比较信号vx1s中的第n在后比较信号vout1n。

45.第二信号转换器a2可以基于多个第二像素信号vp2s、斜坡信号vr和第二控制码信号cc2s来生成多个第二在后比较信号vx2s。例如,第二信号转换器a2可以包括多个比较电路a21至a2n。多个比较电路a21至a2n可以共同接收斜坡信号vr和第二控制码信号cc2s,可以接收多个第二像素信号vp2s之中的对应像素信号,并且可以分别生成多个第二在后比较信号vx2s。

46.例如,多个比较电路a21至a2n之中的第一比较电路a21可以基于多个第二像素信号vp2s之中的第一像素信号vp21、第二控制码信号cc2s和斜坡信号vr,来生成多个第二在后比较信号vx2s之中的第一在后比较信号vout21。多个比较电路a21至a2n之中的第n比较电路a2n可以基于多个第二像素信号vp2s之中的第n像素信号vp2n、第二控制码信号cc2s和斜坡信号vr,来生成多个第二在后比较信号vx2s之中的第n在后比较信号vout2n。

47.第三信号转换器a3可以基于多个第三像素信号vp3s、斜坡信号vr和第三控制码信号cc3s来生成多个第三在后比较信号vx3s。例如,第三信号转换器a3可以包括多个比较电路a31至a3n。多个比较电路a31至a3n可以共同接收斜坡信号vr和第三控制码信号cc3s,可以接收多个第三像素信号vp3s之中的对应像素信号,并且可以分别生成多个第三在后比较信号vx3s。

48.例如,多个比较电路a31至a3n之中的第一比较电路a31可以基于多个第三像素信号vp3s之中的第一像素信号vp31、第三控制码信号cc3s和斜坡信号vr,来生成多个第三在后比较信号vx3s之中的第一在后比较信号vout31。多个比较电路a31至a3n之中的第n比较电路a3n可以基于多个第三像素信号vp3s之中的第n像素信号vp3n、第三控制码信号cc3s和斜坡信号vr,来生成多个第三在后比较信号vx3s之中的第n在后比较信号vout3n。

49.第一比较电路a11可以代表第一信号转换器a1中的比较电路a11至a1n的结构,第一比较电路a21可以代表第二信号转换器a2中的比较电路a21至a2n的结构,并且第一比较电路a31可以代表第三信号转换器a3中的比较电路a31至a3n的结构。

50.图3是示出第一信号转换器a1中的第一比较电路a11的一个实施例的框图。参考图3,第一比较电路a11可以包括第一采样电路ca11、第二采样电路ca12、第一在前比较器aa11、第一开关swa11、第二开关swa12、第三采样电路ca13、第四采样电路ca14、第一在后比较器aa12、第三开关swa13和第四开关swa14。

51.第一采样电路ca11可以在行时间期间采样第一像素信号vp11,并且将采样的第一像素信号输出到第一在前比较器aa11的第一输入端子。该第一输入端子可以是反相(

‑

)输入端子。

52.第二采样电路ca12可以在行时间期间采样斜坡信号vr,并且将采样的斜坡信号输出到第一在前比较器aa11的第二输入端子。该第二输入端子可以是同相( )输入端子。

53.第一在前比较器aa11可以基于采样的第一像素信号和采样的斜坡信号来生成第一在前比较信号vaout1。例如,第一在前比较器aa11可以在行时间期间将采样的第一像素信号与采样的斜坡信号进行比较,并且可以在比较结果表明采样的第一像素信号的电压电平变得低于采样的斜坡信号的电压电平时,允许第一在前比较信号vaout1转变。第一在前比较器aa11可以在行时间之前的初始化时间期间,由第一开关swa11和第二开关swa12初始化。

54.第一开关swa11可以耦合在第一在前比较器aa11的第一输入端子与第一输出端子之间。第一输出端子可以是同相( )输出端子,并且可以是通过其输出第一在前比较信号vaout1的输出端子。第一开关swa11可以基于第一开关控制信号s1选择性地将第一输入端子耦合到第一输出端子。例如,第一开关swa11可以在初始化时间期间将第一输入端子电耦合到第一输出端子,并且可以在行时间期间将第一输入端子与第一输出端子电去耦合。

55.第二开关swa12可以耦合在第一在前比较器aa11的第二输入端子与第二输出端子之间。第二输出端子可以是反相(

‑

)输出端子。第二开关swa12可以基于第一开关控制信号s1选择性地将第二输入端子耦合到第二输出端子。例如,第二开关swa12可以在初始化时间期间将第二输入端子电耦合到第二输出端子,并且可以在行时间期间将第二输入端子与第二输出端子电去耦合。

56.第三采样电路ca13可以在行时间期间采样第一在前比较信号vaout1,并且可以将采样的第一在前比较信号输出到第一在后比较器aa12的第一输入端子n11。第一输入端子n11可以是反相(

‑

)输入端子。第三采样电路ca13可以在初始化时间期间采样第一在后比较器aa12的第一输入端子n11的电压电平。

57.第四采样电路ca14可以在初始化时间期间采样被输入到第一在后比较器aa12的第二输入端子n12的第一参考信号vref1(例如,在该第二输入端子n12处生成的第一参考信号vref1)。第二输入端子n12可以是同相( )输入端子。第四采样电路ca14可以耦合在第一在后比较器aa12的第二输入端子n12与低电压端子(例如,接地电压端子)之间。

58.第一在后比较器aa12可以在行时间期间基于采样的第一在前比较信号和第一参考信号vrefl来生成第一在后比较信号vout11。例如,第一在后比较器aa12可以在第一比较前提下将采样的第一在前比较信号与第一参考信号vref1进行比较,并且可以在比较结果

表明采样的第一在前比较信号的电压电平变得低于第一参考信号vref1的电压电平时,允许第一在后比较信号vout11转变。

59.例如,第一比较前提可以包括以下条件:在初始化时间期间,第一在后比较器aa12的第一输入端子n11被初始化为第一电压电平。在一个实施例中,第一比较前提可以包括以下条件:在初始化时间期间,第一参考信号vref1的电压电平被调节为第一电压电平。

60.第一在后比较器aa12可以在初始化时间期间被初始化,并且当被初始化时,第一在后比较器aa12可以基于第一控制码信号cc1s通过自生成,将第一输入端子n11初始化为第一电压电平,或者将第一参考信号vref1的电压电平调节为第一电压电平。自生成与在第一在后比较器aa12中生成的电流有关。自生成操作的示例在下面例如参考图4更详细地描述。

61.第三开关swa13可以耦合在第一在后比较器aa12的第一输入端子n11与第一输出端子之间。第一输出端子可以是通过其输出第一在后比较信号vout11的同相( )输出端子。第三开关swa13可以基于第二开关控制信号s2选择性地将第一输入端子n11耦合到第一输出端子。例如,第三开关swa13可以在初始化时间期间将第一输入端子n11电耦合到第一输出端子,并且可以在行时间期间将第一输入端子n11与第一输出端子电去耦合。

62.第四开关swa14可以耦合在第一在后比较器aa12的第二输入端子n12与第二输出端子之间。第二输出端子可以是反相(

‑

)输出端子。第四开关swa14可以基于第二开关控制信号s2选择性地将第二输入端子n12耦合到第二输出端子。例如,第四开关swa14可以在初始化时间期间将第二输入端子n12电耦合到第二输出端子,并且可以在行时间期间将第二输入端子n12与第二输出端子电去耦合。

63.图4是示出第一在后比较器aa12的一个实施例、连同第三开关swa13和第四开关swa14的电路图。

64.参考图4,第一在后比较器aa12可以包括输入电路an11和an12、加载电路ap11和ap12、第一电流源as11和第二电流源as12。输入电路an11和an12可以分别耦合在加载电路ap11和ap12与电流源as11和as12之间。输入电路an11和an12可以接收采样的第一在前比较信号和第一参考信号vref1。例如,输入电路an11和an12可以分别包括第一nmos晶体管an11和第二nmos晶体管an12。第一nmos晶体管an11可以包括耦合到第二输入端子n12的栅极端子、以及耦合在第二输出端子与第一节点之间的源极端子和漏极端子。第二nmos晶体管an12可以包括耦合到第一输入端子n11的栅极端子、以及耦合在第一输出端子与第一节点之间的源极端子和漏极端子。

65.加载电路ap11和ap12可以耦合在相应输入电路an11和an12与高电压端子(例如,电源电压端子)之间。例如,加载电路ap11和ap12可以分别包括第一pmos晶体管ap11和第二pmos晶体管ap12。第一pmos晶体管ap11可以包括耦合到第一共同耦合节点的栅极端子、以及耦合在高电压端子与第二输出端子之间的源极端子和漏极端子。第一共同耦合节点和第二输出端子可以彼此电耦合。第二pmos晶体管ap12可以包括耦合到第一共同耦合节点的栅极端子、以及耦合在高电压端子与第一输出端子之间的源极端子和漏极端子。

66.第一电流源as11和第二电流源as12可以并联耦合在第一节点与低电压端子之间。第一电流源as11可以生成与第一参考信号vref1的默认电压电平对应的第一电流。第二电流源as12可以基于第一控制码信号cc1s生成第一调节电流。第一调节电流可以用于调节第

一参考信号vref1的电压电平。

67.具有上述配置的第一在后比较器aa12可以在初始化时间期间基本上使用第一电流,并且可以在初始化时间期间选择性地使用基于第一控制码信号cc1s的第一调节电流。因此,从第一电流获得的第一参考电流可以通过第三开关swa13被提供给第一输入端子n11,并且通过第四开关swa14被提供给第二输入端子n12。

68.在一个实施例中,从第一电流和第一调节电流的总和电流(下文中称为“第一总和电流”)获得的第一参考电流可以通过第三开关swa13被提供给第一输入端子n11,并且通过第四开关swa14被提供给第二输入端子n12。例如,当第一总和电流在初始化时间的初始时段期间生成并且第一电流在初始化时间的最后时段期间生成时,第一输入端子n11可以基于从第一总和电流获得的第一参考电流,在初始时段期间被初始化为第一电压电平。而且,基于从第一电流获得的第一参考电流,第一参考信号vref1可以在最后时段期间具有默认电压电平。例如,第三采样电路ca13可以在初始时段期间采样第一输入端子n11的第一电压电平,并且第四采样电路ca14可以在最后时段期间采样第一参考信号vref1的默认电压电平。

69.作为另一示例,当第一电流在初始化时间的初始时段期间生成并且第一总和电流在初始化时间的最后时段期间生成时,第一输入端子n11可以基于从第一电流获得的第一参考电流,在初始时段期间被初始化为默认电压电平。而且,基于从第一总和电流获得的第一参考电流,第一参考信号vref1可以在最后时段期间具有第一电压电平。例如,第三采样电路ca13可以在初始时段期间采样第一输入端子n11的默认电压电平,并且第四采样电路ca14可以在最后时段期间采样第一参考信号vref1的第一电压电平。这样,第一参考信号vref1可以不从外部设备或电路提供,而是可以基于在第一在后比较器aa12中生成的电流来生成(例如,可以自生成)。

70.图5是示出第二信号转换器a2中的第一比较电路a21的一个实施例的框图。参考图5,第一比较电路a21可以包括第一采样电路cb11、第二采样电路cb12、第一在前比较器ab11、第一开关swb11、第二开关swb12、第三采样电路cb13、第四采样电路cb14、第一在后比较器ab12、第三开关swb13和第四开关swb14。

71.第一采样电路cb11可以在行时间期间采样第一像素信号vp21,并且可以将采样的第一像素信号输出到第一在前比较器ab11的第一输入端子。第一输入端子可以是反相(

‑

)输入端子。

72.第二采样电路cb12可以在行时间期间采样斜坡信号vr,并且可以将采样的斜坡信号输出到第一在前比较器ab11的第二输入端子。第二输入端子可以是同相( )输入端子。

73.第一在前比较器ab11可以基于采样的第一像素信号和采样的斜坡信号来生成第一在前比较信号vbout1。例如,第一在前比较器ab11可以在行时间期间将采样的第一像素信号与采样的斜坡信号进行比较,并且可以在比较结果表明采样的第一像素信号的电压电平变得低于采样的斜坡信号的电压电平时,允许第一在前比较信号vbout1转变。第一在前比较器ab11可以在行时间之前的初始化时间期间由第一开关swb11和第二开关swb12初始化。第一在前比较器ab11可以根据与第一信号转换器a1中包括的第一在前比较器aa11相同的比较前提来初始化。例如,第一在前比较器aa11和ab11的输入和输出端子可以被初始化为相同的电平。

74.第一开关swb11可以耦合在第一在前比较器ab11的第一输入端子与第一输出端子之间。第一输出端子可以是同相( )输出端子,并且可以是通过其输出第一在前比较信号vbout1的输出端子。第一开关swb11可以基于第一开关控制信号s1选择性地将第一输入端子耦合到第一输出端子。例如,第一开关swb11可以在初始化时间期间将第一输入端子电耦合到第一输出端子,并且可以在行时间期间将第一输入端子与第一输出端子电去耦合。

75.第二开关swb12可以耦合在第一在前比较器ab11的第二输入端子与第二输出端子之间。第二输出端子可以是反相(

‑

)输出端子。第二开关swb12可以基于第一开关控制信号s1选择性地将第二输入端子耦合到第二输出端子。例如,第二开关swb12可以在初始化时间期间将第二输入端子电耦合到第二输出端子,并且可以在行时间期间将第二输入端子与第二输出端子电去耦合。

76.第三采样电路cb13可以在行时间期间采样第一在前比较信号vbout1,并且可以将采样的第一在前比较信号输出到第一在后比较器ab12的第一输入端子n21。第一输入端子n21可以是反相(

‑

)输入端子。第三采样电路cb13可以在初始化时间期间采样第一在后比较器ab12的第一输入端子n21的电压电平。

77.第四采样电路cb14可以在初始化时间期间采样输入到第一在后比较器ab12的第二输入端子n22的第二参考信号vref2(例如,在该第二输入端子n22处生成的第二参考信号vref2)。第二输入端子n22可以是同相( )输入端子。第四采样电路cb14可以耦合在第一在后比较器ab12的第二输入端子n22与低电压端子之间。

78.第一在后比较器ab12可以在行时间期间基于采样的第一在前比较信号和第二参考信号vref2来生成第一在后比较信号vout21。例如,第一在后比较器ab12可以在不同于第一比较前提的第二比较前提下将采样的第一在前比较信号与第二参考信号vref2进行比较,并且可以在比较结果表明采样的第一在前比较信号的电压电平变得低于第二参考信号vref2的电压电平时,允许第一在后比较信号vout21转变。例如,第二比较前提可以包括以下条件:在初始化时间期间,第一在后比较器ab12的第一输入端子n21被初始化为不同于第一电压电平的第二电压电平。在一个实施例中,第二比较前提可以包括以下条件:在初始化时间期间,第二参考信号vref2的电压电平被调节为第二电压电平。

79.第一在后比较器ab12可以在初始化时间期间被初始化,并且当被初始化时,第一在后比较器ab12可以基于第二控制码信号cc2s通过自生成,将第一输入端子n21初始化为第二电压电平,或者将第二参考信号vref2的电压电平调节为第二电压电平。自生成操作可以与在第一在后比较器ab12中生成的电流有关。自生成操作的一个示例将在下面例如参考图6更详细地描述。

80.第三开关swb13可以耦合在第一在后比较器ab12的第一输入端子n21与第一输出端子之间。第一输出端子可以是同相( )输出端子,并且可以是通过其输出第一在后比较信号vout21的输出端子。第三开关swb13可以基于第二开关控制信号s2选择性地将第一输入端子n21耦合到第一输出端子。例如,第三开关swb13可以在初始化时间期间将第一输入端子n21电耦合到第一输出端子,并且可以在行时间期间将第一输入端子n21与第一输出端子电去耦合。

81.第四开关swb14可以耦合在第一在后比较器ab12的第二输入端子n22与第二输出端子之间。第二输出端子可以是反相(

‑

)输出端子。第四开关swb14可以基于第二开关控制

信号s2选择性地将第二输入端子n22耦合到第二输出端子。例如,第四开关swb14可以在初始化时间期间将第二输入端子n22电耦合到第二输出端子,并且可以在行时间期间将第二输入端子n22与第二输出端子电去耦合。

82.图6是示出第一在后比较器ab12的一个实施例、连同第三开关swb13和第四开关swb14的电路图。参考图6,第一在后比较器ab12可以包括输入电路bn11和bn12、加载电路bp11和bp12、第一电流源bs11和第二电流源bs12。

83.输入电路bn11和bn12可以分别耦合在加载电路bp11和bp12与电流源bs11和bs12之间。输入电路bn11和bn12可以接收采样的第一在前比较信号和第二参考信号vref2。例如,输入电路bn11和bn12可以分别包括第一nmos晶体管bn11和第二nmos晶体管bn12。第一nmos晶体管bn11可以包括耦合到第二输入端子n22的栅极端子、以及耦合在第二输出端子与第二节点之间的源极端子和漏极端子。第二nmos晶体管bn12可以包括耦合到第一输入端子n21的栅极端子、以及耦合在第一输出端子与第二节点之间的源极端子和漏极端子。

84.加载电路bp11和bp12可以耦合在相应输入电路bn11和bn12与高电压端子之间。例如,加载电路bp11和bp12可以分别包括第一pmos晶体管bp11和第二pmos晶体管bp12。第一pmos晶体管bp11可以包括耦合到第二共同耦合节点的栅极端子、以及耦合在高电压端子与第二输出端子之间的源极端子和漏极端子。第二共同耦合节点和第二输出端子可以彼此电耦合。第二pmos晶体管bp12可以包括耦合到第二共同耦合节点的栅极端子、以及耦合在高电压端子与第一输出端子之间的源极端子和漏极端子。

85.第一电流源bs11和第二电流源bs12可以并联耦合在第二节点与低电压端子之间。第一电流源bs11可以生成与第二参考信号vref2的默认电压电平对应的第二电流。第二电流源bs12可以基于第二控制码信号cc2s生成第二调节电流。第二调节电流可以调节第二参考信号vref2的电压电平。

86.具有上述配置的第一在后比较器ab12可以在初始化时间期间基本上使用第二电流,并且可以在初始化时间期间选择性地使用基于第二控制码信号cc2s的第二调节电流。因此,从第二电流获得的第二参考电流可以通过第三开关swb13被提供给第一输入端子n21,并且通过第四开关swb14被提供给第二输入端子n22。

87.在一个实施例中,从第二电流和第二调节电流的总和电流(下文中称为“第二总和电流”)获得的第二参考电流可以通过第三开关swb13被提供给第一输入端子n21,并且通过第四开关swb14被提供给第二输入端子n22。例如,当第二总和电流在初始化时间的初始时段期间生成并且第二电流在初始化时间的最后时段期间生成时,第一输入端子n21可以基于从第二总和电流获得的第二参考电流,在初始时段期间被初始化为第二电压电平。而且,基于从第二电流获得的第二参考电流,第二参考信号vref2可以在最后时段期间具有默认电压电平。

88.例如,第三采样电路cb13可以在初始时段期间采样第一输入端子n21的第二电压电平。第四采样电路cb14可以在最后时段期间采样第二参考信号vref2的默认电压电平。作为另一示例,当第二电流在初始化时间的初始时段期间生成并且第二总和电流在初始化时间的最后时段期间生成时,第一输入端子n21可以基于从第二电流获得的第二参考电流,在初始时段期间被初始化为默认电压电平。基于从第二总和电流获得的第二参考电流,第二参考信号vref2可以在最后时段期间具有第二电压电平。

89.例如,第三采样电路cb13可以在初始时段期间采样第一输入端子n21的默认电压电平。第四采样电路cb14可以在最后时段期间采样第二参考信号vref2的第二电压电平。这样,第二参考信号vref2可以不从外部设备或电路提供,而是可以基于在第一在后比较器ab12中生成的电流来生成(例如,自生成)。

90.图7是示出第三信号转换器a3中包括的第一比较电路a31的一个实施例的框图。参考图7,第一比较电路a31可以包括第一采样电路cc11、第二采样电路cc12、第一在前比较器ac11、第一开关swc11、第二开关swc12、第三采样电路cc13、第四采样电路cc14、第一在后比较器ac12、第三开关swc13和第四开关swc14。

91.第一采样电路cc11可以在行时间期间采样第一像素信号vp31,并且可以将采样的第一像素信号输出到第一在前比较器ac11的第一输入端子。第一输入端子可以是反相(

‑

)输入端子。

92.第二采样电路cc12可以在行时间期间采样斜坡信号vr,并且可以将采样的斜坡信号输出到第一在前比较器ac11的第二输入端子。第二输入端子可以是同相( )输入端子。

93.第一在前比较器ac11可以基于采样的第一像素信号和采样的斜坡信号来生成第一在前比较信号vcout1。例如,第一在前比较器ac11可以在行时间期间将采样的第一像素信号与采样的斜坡信号进行比较,并且可以在比较结果表明采样的第一像素信号的电压电平变得低于采样的斜坡信号的电压电平时,允许第一在前比较信号vcout1转变。第一在前比较器ac11可以在行时间之前的初始化时间期间由第一开关swc11和第二开关swc12初始化。第一在前比较器ac11可以根据与第一信号转换器a1中的第一在前比较器aa11相同的比较前提来初始化。例如,第一在前比较器aa11、ab11和ac11的输入和输出端子可以被初始化为相同的电平。

94.第一开关swc11可以耦合在第一在前比较器ac11的第一输入端子与第一输出端子之间。第一输出端子可以是同相( )输出端子,并且可以是通过其输出第一在前比较信号vcout1的输出端子。第一开关swc11可以基于第一开关控制信号s1选择性地将第一输入端子耦合到第一输出端子。例如,第一开关swc11可以在初始化时间期间将第一输入端子电耦合到第一输出端子,并且可以在行时间期间将第一输入端子与第一输出端子电去耦合。

95.第二开关swc12可以耦合在第一在前比较器ac11的第二输入端子与第二输出端子之间。第二输出端子可以是反相(

‑

)输出端子。第二开关swc12可以基于第一开关控制信号s1选择性地将第二输入端子耦合到第二输出端子。例如,第二开关swc12可以在初始化时间期间将第二输入端子电耦合到第二输出端子,并且可以在行时间期间将第二输入端子与第二输出端子电去耦合。

96.第三采样电路cc13可以在行时间期间采样第一在前比较信号vcout1,并且可以将采样的第一在前比较信号输出到第一在后比较器ac12的第一输入端子n31。第一输入端子n31可以是反相(

‑

)输入端子。第三采样电路cc13可以在初始化时间期间采样第一在后比较器ac12的第一输入端子n31的电压电平。

97.第四采样电路cc14可以在初始化时间期间采样输入到第一在后比较器ac12的第二输入端子n32的第三参考信号vref3(例如,在该第二输入端子n32处生成的第三参考信号vref3)。第二输入端子n32可以是同相( )输入端子。第四采样电路cc14可以耦合在第一在后比较器ac12的第二输入端子n32与低电压端子之间。

98.第一在后比较器ac12可以在行时间期间基于采样的第一在前比较信号和第三参考信号vref3来生成第一在后比较信号vout31。例如,第一在后比较器ac12可以在不同于第一比较前提和第二比较前提的第三比较前提下将采样的第一在前比较信号与第三参考信号vref3进行比较,并且可以在比较结果表明采样的第一在前比较信号的电压电平变得低于第三参考信号vref3的电压电平时,允许第一在后比较信号vout31转变。例如,第三比较前提可以包括以下条件:在初始化时间期间,第一在后比较器ac12的第一输入端子n31被初始化为不同于第一电压电平和第二电压电平的第三电压电平。在一个实施例中,第三比较前提可以包括以下条件:在初始化时间期间,第三参考信号vref3的电压电平被调节为第三电压电平。

99.第一在后比较器ac12可以在初始化时间期间被初始化,并且当被初始化时,第一在后比较器ac12可以基于第三控制码信号cc3s通过自生成,将第一输入端子n31初始化为第三电压电平,或者将第三参考信号vref3的电压电平调节为第三电压电平。自生成操作与在第一在后比较器ac12中生成的电流有关。自生成操作的一个示例将在下面例如参考图8更详细地描述。

100.第三开关swc13可以耦合在第一在后比较器ac12的第一输入端子n31与第一输出端子之间。第一输出端子可以是同相( )输出端子,并且可以是通过其输出第一在后比较信号vout31的输出端子。第三开关swc13可以基于第二开关控制信号s2选择性地将第一输入端子n31耦合到第一输出端子。例如,第三开关swc13可以在初始化时间期间将第一输入端子n31电耦合到第一输出端子,并且可以在行时间期间将第一输入端子n31与第一输出端子电去耦合。

101.第四开关swc14可以耦合在第一在后比较器ac12的第二输入端子n32与第二输出端子之间。第二输出端子可以是反相(

‑

)输出端子。第四开关swc14可以基于第二开关控制信号s2选择性地将第二输入端子n32耦合到第二输出端子。例如,第四开关swc14可以在初始化时间期间将第二输入端子n32电耦合到第二输出端子,并且可以在行时间期间将第二输入端子n32与第二输出端子电去耦合。

102.图8是示出图7所示的第一在后比较器ac12的一个实施例、连同第三开关swc13和第四开关swc14的电路图。

103.参考图8,第一在后比较器ac12可以包括输入电路cn11和cn12、加载电路cp11和cp12、第一电流源cs11和第二电流源cs12。输入电路cn11和cn12可以分别耦合在加载电路cp11和cp12与电流源cs11和cs12之间。输入电路cn11和cn12可以接收采样的第一在前比较信号和第三参考信号vref3。例如,输入电路cn11和cn12可以分别包括第一nmos晶体管cn11和第二nmos晶体管cn12。第一nmos晶体管cn11可以包括耦合到第二输入端子n32的栅极端子、以及耦合在第二输出端子与第三节点之间的源极端子和漏极端子。第二nmos晶体管cn12可以包括耦合到第一输入端子n31的栅极端子、以及耦合在第一输出端子与第三节点之间的源极端子和漏极端子。

104.加载电路cp11和cp12可以耦合在相应输入电路cn11和cn12与高电压端子之间。例如,加载电路cp11和cp12可以分别包括第一pmos晶体管cp11和第二pmos晶体管cp12。第一pmos晶体管cp11可以包括耦合到第三共同耦合节点的栅极端子、以及耦合在高电压端子与第二输出端子之间的源极端子和漏极端子。第三共同耦合节点和第二输出端子可以彼此电

耦合。第二pmos晶体管cp12可以包括耦合到第三共同耦合节点的栅极端子、以及耦合在高电压端子与第一输出端子之间的源极端子和漏极端子。

105.第一电流源cs11和第二电流源cs12可以并联耦合在第三节点与低电压端子之间。第一电流源cs11可以生成与第三参考信号vref3的默认电压电平对应的第三电流。第二电流源cs12可以基于第三控制码信号cc3s,生成用于调节第三参考信号vref3的电压电平的第三调节电流。

106.具有上述配置的第一在后比较器ac12可以在初始化时间期间基本上使用第三电流,并且可以在初始化时间期间选择性地使用基于第三控制码信号cc3s的第三调节电流。因此,从第三电流获得的第三参考电流可以通过第三开关swc13被提供给第一输入端子n31,并且通过第四开关swc14被提供给第二输入端子n32。

107.在一个实施例中,从第三电流和第三调节电流的总和电流(下文中称为“第三总和电流”)获得的第三参考电流可以通过第三开关swc13被提供给第一输入端子n31,并且通过第四开关swc14被提供给第二输入端子n32。例如,当第三总和电流在初始化时间的初始时段期间生成并且第三电流在初始化时间的最后时段期间生成时,第一输入端子n31可以基于从第三总和电流获得的第三参考电流,在初始时段期间被初始化为第三电压电平。基于从第三电流获得的第三参考电流,第三参考信号vref3可以在最后时段期间具有默认电压电平。例如,第三采样电路cc13可以在初始时段期间采样第一输入端子n31的第三电压电平。第四采样电路cc14可以在最后时段期间采样第三参考信号vref3的默认电压电平。

108.作为另一示例,当第三电流在初始化时间的初始时段期间生成并且第三总和电流在初始化时间的最后时段期间生成时,第一输入端子n31可以基于从第三电流获得的第三参考电流,在初始时段期间被初始化为默认电压电平。基于从第三总和电流获得的第三参考电流,第三参考信号vref3可以在最后时段期间具有第三电压电平。例如,第三采样电路cc13可以在初始时段期间采样第一输入端子n31的默认电压电平,并且第四采样电路cc14可以在最后时段期间采样第三参考信号vref3的第三电压电平。这样,第三参考信号vref3可以不从外部设备或电路提供,而是可以基于在第一在后比较器ac12中生成的电流来生成(例如,自生成)。

109.图9是示出存储器160的一个实施例的框图。参考图9,存储器160可以包括第一存储器b1、第二存储器b2和第三存储器b3。

110.如上所述,第一存储器b1可以基于多个第一在后比较信号vx1s中的每个来存储计数信号cnts,并且可以输出所存储的计数信号cnts作为多个第一数字信号dout1s。例如,第一存储器b1可以包括多个第一控制电路ba11至ba1n和多个第一存储电路ba21至ba2n。

111.多个第一控制电路ba11至ba1n可以基于多个第一在后比较信号vx1s和输入控制信号s3,分别生成多个第一存储控制信号ashot1至ashotn。例如,多个第一控制电路ba11至ba1n之中的第一控制电路ba11可以基于第一在后比较信号vx1s中的第一在后比较信号vout11和输入控制信号s3,来生成多个第一存储控制信号ashot1至ashotn之中的第一存储控制信号ashot1。(多个第一控制电路ba11至ba1n之中的)第n控制电路ba1n可以基于第一在后比较信号vx1s中的第n在后比较信号vout1n和输入控制信号s3,来生成(多个第一存储控制信号ashot1至ashotn之中的)第n存储控制信号ashotn。

112.多个第一存储电路ba21至ba2n可以分别基于多个第一存储控制信号ashot1至

ashotn和计数信号cnts,来存储多个第一数字信号dout1s。例如,当(多个第一存储控制信号ashot1至ashotn之中的)第一存储控制信号ashot1被启用时,(多个第一存储电路ba21至ba2n之中的)第一存储电路ba21可以将计数信号cnts存储为第一数字信号dout1s中的第一数字信号d11s。当(多个第一存储控制信号ashot1至ashotn之中的)第n存储控制信号ashotn被启用时,(多个第一存储电路ba21至ba2n之中的)第n存储电路ba2n可以将计数信号cnts存储为第一数字信号dout1s中的第n数字信号d1ns。

113.如上所述,第二存储器b2可以基于多个第二在后比较信号vx2s中的每个来存储计数信号cnts,并且可以输出所存储的计数信号cnts作为多个第二数字信号dout2s。例如,第二存储器b2可以包括多个第二控制电路bb11至bb1n和多个第二存储电路bb21至bb2n。

114.多个第二控制电路bb11至bb1n可以基于多个第二在后比较信号vx2s和输入控制信号s3,分别生成多个第二存储控制信号bshot1至bshotn。例如,(多个第二控制电路bb11至bb1n之中的)第一控制电路bb11可以基于第二在后比较信号vx2s中的第一在后比较信号vout21和输入控制信号s3,来生成(多个第二存储控制信号bshot1至bshotn之中的)第一存储控制信号bshot1。(多个第二控制电路bb11至bb1n之中的)第n控制电路bb1n可以基于第二在后比较信号vx2s中的第n在后比较信号vout2n和输入控制信号s3,来生成(多个第二存储控制信号bshot1至bshotn之中的)第n存储控制信号bshotn。

115.多个第二存储电路bb21至bb2n可以分别基于多个第二存储控制信号bshot1至bshotn和计数信号cnts,来存储多个第二数字信号dout2s。例如,当(多个第二存储控制信号bshot1至bshotn之中的)第一存储控制信号bshot1被启用时,(多个第二存储电路bb21至bb2n之中的)第一存储电路bb21可以将计数信号cnts存储为第二数字信号dout2s中的第一数字信号d21s。当(多个第二存储控制信号bshot1至bshotn之中的)第n存储控制信号bshotn被启用时,多个第二存储电路bb21至bb2n之中的第n存储电路bb2n可以将计数信号cnts存储为第二数字信号dout2s中的第n数字信号d2ns。

116.如上所述,第三存储器b3可以基于多个第三在后比较信号vx3s中的每个来存储计数信号cnts,并且可以输出所存储的计数信号cnts作为多个第三数字信号dout3s。例如,第三存储器b3可以包括多个第三控制电路bc11至bc1n和多个第三存储电路bc21至bc2n。

117.多个第三控制电路bc11至bc1n可以基于多个第三在后比较信号vx3s和输入控制信号s3,分别生成多个第三存储控制信号cshot1至cshotn。例如,多个第三控制电路bc11至bc1n之中的第一控制电路bc11可以基于第三在后比较信号vx3s中的第一在后比较信号vout31和输入控制信号s3,来生成(多个第三存储控制信号cshot1至cshotn之中的)第一存储控制信号cshot1。(多个第三控制电路bc11至bc1n之中的)第n控制电路bc1n可以基于第三在后比较信号vx3s中的第n在后比较信号vout3n和输入控制信号s3,来生成(多个第三存储控制信号cshot1至cshotn之中的)n存储控制信号cshotn。

118.多个第三存储电路bc21至bc2n可以分别基于多个第三存储控制信号cshot1至cshotn和计数信号cnts,来存储多个第三数字信号dout3s。例如,当(多个第三存储控制信号cshot1至cshotn之中的)第一存储控制信号cshot1被启用时,(多个第三存储电路bc21至bc2n之中的)第一存储电路bc21可以将计数信号cnts存储为第三数字信号dout3s中的第一数字信号d31s。当(多个第三存储控制信号cshot1至cshotn之中的)第n存储控制信号cshotn被启用时,(多个第三存储电路bc21至bc2n之中的)第n存储电路bc2n可以将计数信

号cnts存储为第三数字信号dout3s中的第n数字信号d3ns。

119.多个第一控制电路ba11至ba1n、多个第二控制电路bb11至bb1n、多个第三控制电路bc11至bc1n、多个第一存储电路ba21至ba2n、多个第二存储电路bb21至bb2n、和多个第三存储电路bc21至bc2n可以使用相同的电压(例如,电源供应电压vdd)作为源电源供应。多个第一存储电路ba21至ba2n、多个第二存储电路bb21至bb2n、和多个第三存储电路bc21至bc2n可以被称为“线存储器”。

120.图10是示出图9所示的第一控制电路ba11至ba1n之中的第一控制电路ba11的一个实施例的电路图。由于第一控制电路ba11至ba1n可以被设计为全部相同,因此在下文中代表性地描述第一控制电路ba11。

121.参考图10,第一控制电路ba11可以包括输入电路in11、延迟电路dly11和输出电路out11。输入电路in11可以接收多个第一在后比较信号vx1s中的第一在后比较信号vout11和输入控制信号s3。例如,输入电路in11可以包括与非门和非门。与非门可以对第一在后比较信号vout11和输入控制信号s3执行与非操作,并且非门可以使与非门的输出信号反相。

122.延迟电路dly11可以将输入电路in11的输出信号延迟一设置延迟时间。例如,延迟电路dly11可以包括反相器链,在该反相器链中,多个非门相互串联耦合。

123.输出电路out11可以接收输入电路in11的输出信号和延迟电路dly11的输出信号,并且可以生成多个第一存储控制信号ashot1至ashotn之中的第一存储控制信号ashot1。例如,输出电路out11可以包括或门。该或门可以对输入电路in11的输出信号和延迟电路dly11的输出信号执行或操作,从而生成第一存储控制信号ashot1,第一存储控制信号ashot1被生成达设置时间(例如,相对较短的时间)。第一存储控制信号ashot1的脉冲宽度(例如,启用宽度)可以对应于延迟时间。

124.图11是示出图9所示的第二控制电路bb11至bb1n之中的第一控制电路bb11的一个实施例的电路图。由于第二控制电路bb11至bb1n可以被设计为全部相同,因此在下文中代表性地描述第一控制电路bb11。

125.参考图11,第一控制电路bb11可以包括输入电路in21、延迟电路dly21和输出电路out21。输入电路in21可以接收多个第二在后比较信号vx2s中的第一在后比较信号vout21和输入控制信号s3。例如,输入电路in21可以包括与非门和非门。与非门可以对第一在后比较信号vout21和输入控制信号s3执行与非操作,并且非门可以使与非门的输出信号反相。

126.延迟电路dly21可以以延迟时间来延迟输入电路in21的输出信号。例如,延迟电路dly21可以包括反相器链,在该反相器链中,多个非门相互串联耦合。

127.输出电路out21可以接收输入电路in21的输出信号和延迟电路dly21的输出信号,并且可以生成多个第二存储控制信号bshot1至bshotn之中的第一存储控制信号bshot1。例如,输出电路out21可以包括或门。该或门可以对输入电路in21的输出信号和延迟电路dly21的输出信号执行或操作,从而生成第一存储控制信号bshot1,第一存储控制信号bshot1被生成达设置时间(例如,相对较短的时间)。第一存储控制信号bshot1的脉冲宽度(例如,启用宽度)可以对应于延迟时间。

128.图12是示出图9所示的第三控制电路bc11至bc1n之中的第一控制电路bc11的一个实施例的电路图。由于第三控制电路bc11至bc1n可以被设计为全部相同,因此在下文中代表性地描述第一控制电路bc11。

129.参考图12,第一控制电路bc11可以包括输入电路in31、延迟电路dly31和输出电路out31。输入电路in31可以接收多个第三在后比较信号vx3s中的第一在后比较信号vout31和输入控制信号s3。例如,输入电路in31可以包括与非门和非门。与非门可以对第一在后比较信号vout31和输入控制信号s3执行与非操作,并且非门可以使与非门的输出信号反相。

130.延迟电路dly31可以以延迟时间来延迟输入电路in31的输出信号。例如,延迟电路dly31可以包括反相器链,在该反相器链中,多个非门相互串联耦合。

131.输出电路out31可以接收输入电路in31的输出信号和延迟电路dly31的输出信号,并且可以生成多个第三存储控制信号cshot1至cshotn之中的第一存储控制信号cshot1。例如,输出电路out31可以包括或门。该或门可以对输入电路in31的输出信号和延迟电路dly31的输出信号执行或操作,从而生成第一存储控制信号cshot1,第一存储控制信号cshot1被生成达设置时间(例如,相对较短的时间)。第一存储控制信号cshot1的脉冲宽度(例如,启用宽度)可以对应于延迟时间。

132.图13示出了用于操作图像感测设备100的时序图的一个实施例。图13示出了与一个像素信号(例如,第一像素信号vp11)有关的操作,作为代表示例。

133.参考图13,可以在初始化时间rst期间初始化图像感测设备100。例如,可以根据第一比较前提来初始化第一信号转换器a1中的多个在后比较器,可以根据第二比较前提来初始化第二信号转换器a2中包括的多个在后比较器,并且可以根据第三比较前提来初始化第三信号转换器a3中包括的多个在后比较器(例如,参考图14和图15)。

134.图像感测设备100可以在行时间srt期间生成和存储第一像素信号vp11。其更详细的描述如下。

135.像素阵列120可以在行时间srt期间生成第一像素信号vp11。例如,在行时间srt的重置时间rt期间,像素阵列120可以生成与第一像素信号vp11中的噪声分量对应的重置信号vr11,作为第一像素信号vp11。然后,在行时间srt的数据时间dt期间,像素阵列可以生成与入射光对应的数据信号vd11,作为第一像素信号vp11。

136.斜坡信号生成器130可以基于斜坡控制信号rp生成在行时间srt期间具有设置模式的斜坡信号vr。例如,斜坡信号生成器130可以生成如下斜坡信号vr:该斜坡信号vr在重置时间rt期间在重置电压范围内呈斜坡,并且在数据时间dt期间在数据电压范围内呈斜坡。

137.第一在前比较器aa11可以将第一像素信号vp11与斜坡信号vr进行比较,并且可以生成与比较结果对应的第一在前比较信号vaout1。例如,在重置时间rt和数据时间dt期间,当斜坡信号vr的电压电平高于第一像素信号vp11的电压电平时,第一在前比较器aa11可以生成具有逻辑高电平的第一在前比较信号vaout1。当斜坡信号vr的电压电平低于第一像素信号vp11的电压电平时,第一在前比较器aa11可以生成具有逻辑低电平的第一在前比较信号vaout1。第一在前比较信号vaout1可以由第三采样电路ca13采样。

138.第一在后比较器aa12可以在第一比较前提下将采样的第一在前比较信号与第一参考信号vref1进行比较。第一在后比较器aa12可以生成与比较结果对应的第一在后比较信号vout11。例如,在重置时间rt和数据时间dt期间,当采样的在前比较信号的电压电平高于第一参考信号vref1的电压电平时,第一在后比较器aa12可以生成具有逻辑低电平的第一在后比较信号vout11。当采样的在前比较信号的电压电平低于第一参考信号vref1的电

压电平时,第一在后比较器aa12可以生成具有逻辑高电平的第一在后比较信号vout11。

139.此时,由于第一在后比较信号vout11是在第一比较前提下生成的,所以第一在后比较信号vout11的转变时间和第一在前比较信号vaout11的转变时间可以彼此不同。例如,第一在后比较信号vout11的转变时间可以比第一在前比较信号vaout1的转变时间少设置时间。该设置时间可以根据电压差δv来确定,其示例在下面参考图14和图15来描述。

140.全局计数器150可以生成在行时间srt期间以设置方式被计数的计数信号cnts。例如,全局计数器150可以生成在重置时间rt期间被计数和在数据时间dt期间被计数的计数信号cnts。

141.第一控制电路ba11可以基于第一在后比较信号vout11和输入控制信号s3,生成第一存储控制信号ashot1。例如,第一控制电路ba11可以在重置时间rt和数据时间dt期间,根据第一在后比较信号vout11的转变时间,允许第一存储控制信号ashot1被生成达设置时间(例如,相对较短的时间)。例如,第一控制电路ba11可以启用第一存储控制信号ashot1达设置时间(例如,相对较短的时间)。

142.第一存储电路ba21可以基于第一存储控制信号ashot1来存储计数信号cnts。例如,第一存储电路ba21可以在第一存储控制信号ashot1在重置时间rt期间脉冲时,锁存计数信号cnts,并且可以输出锁存的计数信号(下文中称为“重置计数信号”),作为第一数字信号d11s。另外,第一存储电路ba21可以在第一存储控制信号ashot1在数据时间dt期间脉冲时,锁存计数信号cnts,并且可以输出锁存的计数信号(下文中称为“数据计数信号”),作为第一数字信号d11s。

143.重置计数信号还可以包括与设置时间对应的计数码“α”,并且数据计数信号还可以包括与设置时间对应的计数码“α”。例如,不必要的计数码“α”可以被反映在重置计数信号和数据计数信号中。在一个实施例中,计数码“α”可以通过后续操作进行偏移。例如,后续操作可以包括数字双采样(dds)操作。

144.像素阵列120可以在行时间srt期间同时生成包括第一像素信号vp11的多个像素信号vps。此时,在多个像素信号vps中可以存在具有与第一像素信号vp11的电压电平相同的电压电平的像素信号(下文中称为“相同像素信号”)。在这种情况下,与第一像素信号vp11对应的第一在后比较信号vout11的转变时间可以等于与相同像素信号对应的在后比较信号的转变时间。其描述将参考图14和图15更详细地描述。在下文中,为了便于描述,多个第二像素信号vp2s之中的第一像素信号vp21和多个第三像素信号vp3s之中的第一像素信号vp31将被取作相同像素信号的示例,并且进行描述。

145.图14示出了根据一个示例的用于操作第一像素信号vp11、vp21和vp31的时序图的一个实施例。

146.参考图14,在初始化时间rst期间,可以将第一输入端子n11、n21和n31分别初始化为第一至第三电压电平。例如,在初始化时间rst的初始时段期间,第一在后比较器aa12可以基于第一控制码信号cc1s,将第一输入端子n11初始化为与第一总和电流对应的第一电压电平。初始时段对应于其中第一开关控制信号s1被启用的时段。第一电压电平可以比默认电压电平高电压差δv。

147.在初始化时间rst的初始时段期间,第一在后比较器ab12可以基于第二控制码信号cc2s,将第一输入端子n21初始化为与第二总和电流对应的第二电压电平。第二电压电平

可以等于默认电压电平。在初始化时间rst的初始时段期间,第一在后比较器ac12可以基于第三控制码信号cc3s,将第一输入端子n31初始化为与第三总和电流对应的第三电压电平。第三电压电平可以比默认电压电平低电压差δv。

148.在初始化时间rst期间,可以在第二输入端子n12、n22和n32处生成具有默认电压电平的第一至第三参考信号vref1、vref2和vref3。第一至第三参考信号vref1、vref2和vref3可以具有在初始化时间rst的最后时段期间被调节的默认电压电平。最后时段对应于其中第一开关控制信号s1被停用并且第二开关控制信号s2被启用的时段。

149.在这种状态中,在行时间srt期间,可以通过第一输入端子n11输入与第一像素信号vp11对应的采样的第一在前比较信号,可以通过第一输入端子n21输入与第一像素信号vp21对应的采样的第一在前比较信号,并且可以通过第一输入端子n31输入与第一像素信号vp31对应的采样的第一在前比较信号。此时,可以在通过第一输入端子n11、n21和n31输入的采样的第一在前比较信号之间保持电压差δv。

150.因此,在行时间srt期间,在第一在后比较信号vout11、vout21和vout31之间可以出现与电压差δv对应的延迟差。例如,在行时间srt的重置时间rt期间,在采样的第一在前比较信号与第一至第三参考信号vref1、vref2和vref3之间的交叉时间点被稍微改变。因此,第一在后比较信号vout11、vout21和vout31可以顺序地转变。另外,在行时间srt的数据时间dt期间,采样的第一在前比较信号与第一至第三参考信号vref1、vref2和vref3之间的交叉时间点被稍微改变。因此,第一在后比较信号vout11、vout21和vout31可以顺序地转变。

151.根据在第一在后比较信号vout11、vout21和vout31之间出现的延迟差,在行时间srt期间,第一控制电路ba11、bb11和bc11可以顺序地启用第一存储控制信号ashot1、bshot1和cshot1,并且第一存储电路ba21、bb21和bc21可以基于第一存储控制信号ashot1、bshot1和cshot1顺序地存储计数信号cnts。因此,可以分散第一控制电路ba11、bb11和bc11以及第一存储电路ba21、bb21和bc21使用源电源供应(例如,电源供应电压vdd)的时间点。结果,还可以分散源电源供应中的下降量。

152.图15示出了根据另一示例的用于操作第一像素信号vp11、vp21和vp31的时序图的一个实施例。

153.参考图15,在初始化时间rst期间,可以将第一输入端子n11、n21和n31初始化为默认电压电平。例如,在初始化时间rst的初始时段期间,第一在后比较器aa12可以将第一输入端子n11初始化为与第一电流对应的默认电压电平。初始时段对应于其中第一开关控制信号s1被启用的时段。在初始化时间rst的初始时段期间,第一在后比较器ab12可以将第一输入端子n21初始化为与第二电流对应的默认电压电平。在初始化时间rst的初始时段期间,第一在后比较器ac12可以将第一输入端子n31初始化为与第三电流对应的默认电压电平。

154.在初始化时间rst期间,可以在第二输入端子n12、n22和n32处生成分别具有第一至第三电压电平的第一至第三参考信号vref1、vref2和vref3。例如,在初始化时间rst的最后时段期间,第一在后比较器aa12可以基于第一控制码信号cc1s,将第一参考信号vref1的电压电平调节为第一电压电平,第一电压电平对应于第一总和电流。最后时段对应于其中第一开关控制信号s1被停用并且第二开关控制信号s2被启用的时段。第一电压电平可以比

默认电压电平高电压差δv。

155.在初始化时间rst的最后时段期间,第一在后比较器ab12可以基于第二控制码信号cc2s,将第二参考信号vref2的电压电平调节为第二电压电平,第二电压电平对应于第二总和电流。第二电压电平可以等于默认电压电平。

156.在初始化时间rst的最后时段期间,第一在后比较器ac12可以基于第三控制码信号cc3s,将第三参考信号vref3的电压电平初始化为第三电压电平,第三电压电平对应于第三总和电流。第三电压电平可以比默认电压电平低电压差δv。

157.在这种状态中,在行时间srt期间,可以通过第一输入端子n11输入与第一像素信号vp11对应的采样的第一在前比较信号,可以通过第一输入端子n21输入与第一像素信号vp21对应的采样的第一在前比较信号,并且可以通过第一输入端子n31输入与第一像素信号vp31对应的采样的第一在前比较信号。此时,通过第一输入端子n11、n21和n31输入的采样的第一在前比较信号可以具有相同的电压电平。

158.因此,在行时间srt期间,在第一在后比较信号vout11、vout21和vout31之间可以出现与电压差δv对应的延迟差。例如,在行时间srt的重置时间rt期间,采样的第一在前比较信号与第一至第三参考信号vref1、vref2和vref3之间的交叉时间点被稍微改变。因此,第一在后比较信号vout11、vout21和vout31可以顺序地转变。另外,在行时间srt的数据时间dt期间,采样的第一在前比较信号与第一至第三参考信号vref1、vref2和vref3之间的交叉时间点被稍微改变。因此,第一在后比较信号vout11、vout21和vout31可以顺序地转变。

159.根据在第一在后比较信号vout11、vout21和vout31之间出现的延迟差,在行时间srt期间,第一控制电路ba11、bb11和bc11可以顺序地启用第一存储控制信号ashot1、bshot1和cshot1,并且第一存储电路ba21、bb21和bc21可以分别基于第一存储控制信号ashot1、bshot1和cshot1,顺序地存储计数信号cnts。因此,可以分散第一控制电路ba11、bb11和bc11以及第一存储电路ba21、bb21和bc21使用源电源供应(例如,电源供应电压vdd)的时间点。因此,还可以分散源电源供应中的下降量。

160.根据本公开的前述实施例中的一个或多个,可以将用于多个组中的每个组的不同比较前提应用于针对每个对应行而生成的像素信号,从而使源电源供应中的下降量分散。根据本公开的这些或其他实施例,可以通过降低或最小化下降的电源的影响,来提高图像感测设备的操作可靠性。

161.尽管已经关于特定实施例示出和描述了本公开,但是所公开的实施例被提供用于描述,而不旨在是限制性的。此外,注意,如本领域技术人员根据本公开将认识到的,可以通过落入所附权利要求的范围内的替换、改变和修改,以各种方式来实现本公开。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。