氮化镓基cmos制备方法及氮化镓基cmos结构

技术领域

1.本发明涉及半导体技术领域,尤其涉及一种氮化镓基cmos制备方法及氮化镓基cmos结构。

背景技术:

2.互补金属氧化物半导体技术由于其突出的静态功耗优势,是目前数字电路的基础构成单元。但对于氮化镓材料,由于目前缺乏在单个衬底上集成增强型n沟道和p沟道场效应晶体管的合适策略,不仅严重阻碍了氮化镓基数字集成电路的发展,同时制约了氮化镓数字控制器件在射频和功率集成电路方面的拓展。

技术实现要素:

3.本发明提供的氮化镓基cmos制备方法及氮化镓基cmos结构,能够在单个衬底上实现nmos和pmos场效应管的集成,避免了器件之间的串扰,提高了cmos的整体可靠性。

4.第一方面,本发明提供一种氮化镓基cmos制备方法,包括:

5.提供一叠层结构,所述叠层结构包括由下向上依次设置的衬底、氮化镓缓冲及沟道层、氮化铝插入层、氮化镓铝超薄势垒层、氮化铝截止层、p型氮化镓层以及重掺杂p型氮化镓层;

6.对所述叠层结构的部分区域刻蚀至氮化铝截止层;

7.在刻蚀区域制备源/漏电极以及栅电极形成nmos,在未刻蚀的区域制备源/漏电极以及栅电极形成pmos;并对所述nmos和所述pmos进行隔离;

8.将所述nmos和所述pmos的栅电极通过导电金属进行电连接,将所述nmos和所述pmos的漏电极导电金属进行电连接。

9.可选地,在刻蚀区域制备源/漏电极以及栅电极形成nmos,在未刻蚀的区域制备源/漏电极以及栅电极形成pmos包括:

10.在所述刻蚀区域和所述未刻蚀区域形成第一钝化层;在所述刻蚀区域间隔的确定第一源/漏区域,对所述第一源/漏区域刻蚀至氮化镓缓冲及沟道层,并在所述第一源/漏区域形成第一源/漏电极;

11.在所述刻蚀区域和所述未刻蚀区域形成第二钝化层;在所述未刻蚀区域间隔的确定第二源/漏区域,对所述第二源/漏区域刻蚀至重掺杂p型氮化镓层,并在所述第二源/漏区域形成第二源/漏电极;

12.对刻蚀区域和未刻蚀区域的氮化铝插入层、氮化镓铝超薄势垒层和氮化铝截止层进行隔离;

13.在所述第一源/漏区域之间确定第一栅极区域,并将第一栅极区域刻蚀至氮化镓铝超薄势垒层;在所述第二源/漏区域之间确定第二栅极区域,并将第二栅极区域刻蚀至重掺杂p型氮化镓层;

14.在所述第一栅极区域和所述第二栅极区域形成栅电极。

15.可选地,第一源/漏电极为钛、铝、镍和金的叠层结构,或者,第一源/漏电极为钛、铝、钛和氮化钛的叠层结构。

16.可选地,第二源/漏电极为镍金叠层结构。

17.可选地,栅电极为镍/金叠层、铂/钛/金叠层、铝/镍/金叠层或氮化钛。

18.可选地,所述第一钝化层为氧化铝和氧化硅中的一种或两种形成的膜层;所述第二钝化层为氮化硅和氧化硅中的一种或两种形成的膜层。

19.可选地,所述氮化镓铝超薄势垒层中的铝组分为10%~30%。

20.可选地,p型氮化镓层为镁掺杂的氮化镓层,其中,镁的浓度为3e

19

cm-3

~5e

19

cm-3

;

21.重掺杂的p型氮化镓层为镁掺杂的氮化镓层,其中,镁的浓度为1e

20

cm-3

~3e

20

cm-3

。

22.可选地,衬底为硅、碳化硅、蓝宝石或氮化镓中的一种或两种以上的叠层。

23.第二方面,本发明提供一种氮化镓基cmos结构,包括:

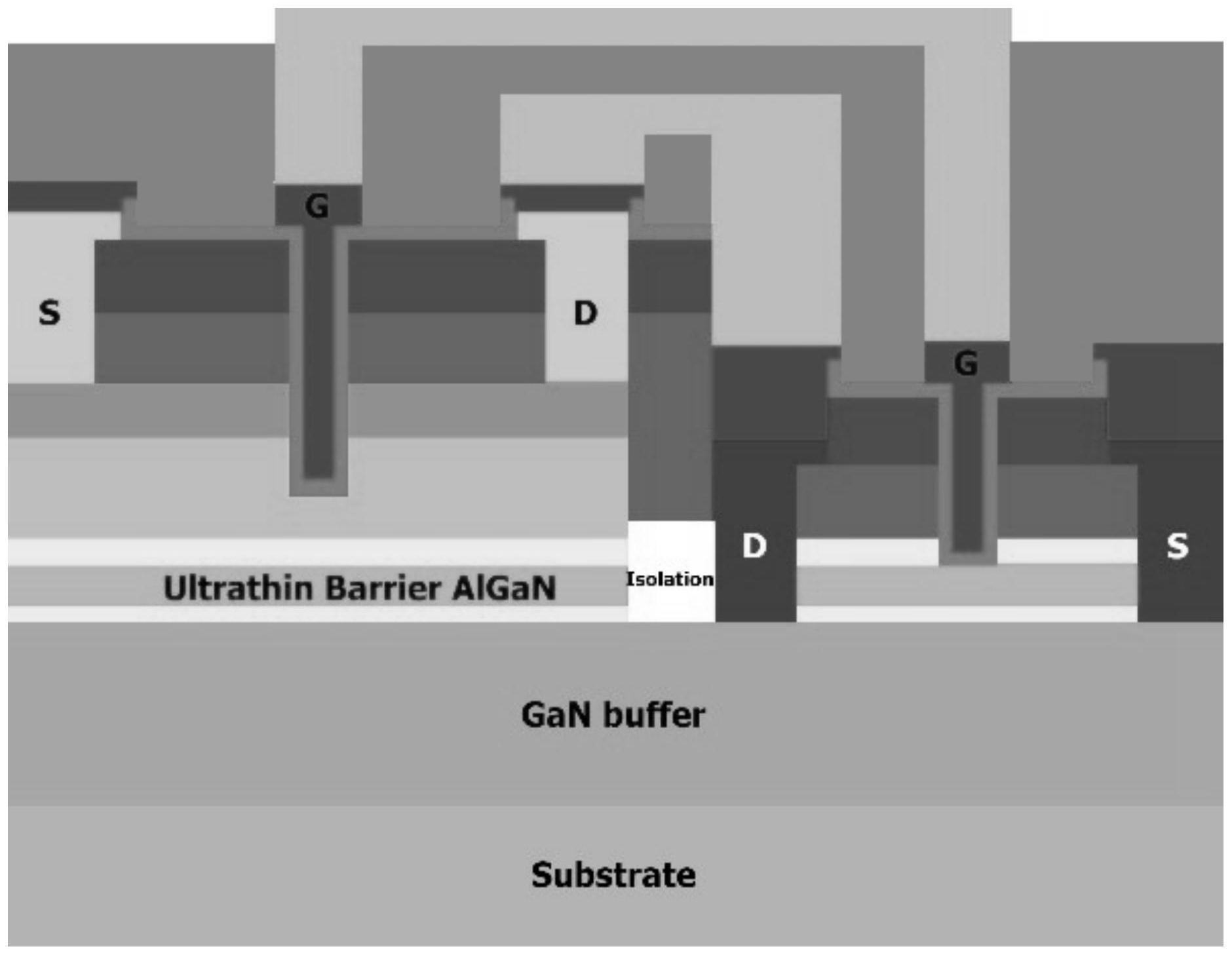

24.叠层结构,包括由下向上依次设置的衬底、氮化镓缓冲及沟道层、氮化铝插入层、氮化镓铝超薄势垒层、氮化铝截止层;所述叠层结构具有第一区域和第二区域;所述第一区域和第二区域的氮化铝插入层、氮化镓铝超薄势垒层及氮化铝截止层隔离设置;

25.所述第一区域具有第一源/漏区域,所述第一源/漏区域分别设置有与氮化镓缓冲及沟道层电接触的第一源/漏电极;第一源/漏电极贯穿所述氮化铝截止层、氮化镓铝超薄势垒层和所述氮化铝插入层,所述第一源漏区域之间设置有第一栅极区域,所述第一栅极区域设置有与所述氮化镓铝超薄势垒层电接触的栅电极;

26.所述第二区域由下向上依次设置有p型氮化镓层和重掺杂p型氮化镓层,所述第二区域具有第二源/漏区域,所述第二源/漏区域分别设置有与重掺杂p型氮化镓层电接触的第二源/漏电极;所述第二源漏区域之间设置有第二栅极区域,所述第二栅极区域设置有与所述p型氮化镓层电接触的栅电极;

27.其中,所述第一漏电极和所述第二漏电极通过金属线电连接,所述第一栅极区域的栅电极与第二栅极区域的栅电极通过金属线电连接。

28.在本发明提供的技术方案中,在单个衬底上实现了增强型nmos和pmos场效应晶体管的集成,氮化镓铝超薄势垒的引入在不但可以获得增强型的nmos器件,同时避免了pmos器件中二维电子气的存在,避免了在pmos器件在工作过程中二维电子气与二维空穴气之间的串扰,提高了cmos的整体可靠性,推动了氮化镓在数字集成电路领域的发展。

附图说明

29.图1为本发明一实施例氮化镓基cmos制备方法的叠层结构示意图;

30.图2为本发明一实施例氮化镓基cmos制备方法的第一次钝化的示意图;

31.图3为本发明一实施例氮化镓基cmos制备方法第一源/漏电极的示意图;

32.图4为本发明一实施例氮化镓基cmos制备方法的第二次钝化的示意图;

33.图5为本发明一实施例氮化镓基cmos制备方法第二源/漏电极的示意图;

34.图6为本发明一实施例氮化镓基cmos制备方法隔离两个器件的示意图;

35.图7为本发明一实施例氮化镓基cmos制备方法刻蚀第一栅极区域和第二栅极区域

并形成栅介质的示意图;

36.图8为本发明一实施例氮化镓基cmos制备方法形成栅电极的示意图;

37.图9为本发明一实施例氮化镓基cmos制备方法采用金属线对nmos和pmos进行电连接的示意图。

具体实施方式

38.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

39.本发明实施例提供一种氮化镓基cmos制备方法,如图1-9所示,包括:

40.提供一叠层结构,所述叠层结构包括由下向上依次设置的衬底、氮化镓缓冲及沟道层、氮化铝插入层、氮化镓铝超薄势垒层、氮化铝截止层、p型氮化镓层以及重掺杂p型氮化镓层;在一些实施例中,氮化铝插入层用于实现氮化镓缓冲及沟道层与氮化镓铝超薄势垒层的晶格适配,氮化铝截止层一方面能够阻止p型氮化镓中的掺杂物进入到氮化镓铝超薄势垒层,一方面能够作为刻蚀的截止层。在一些实施例中,叠层结构如图1所示。在一些实施例中,氮化镓铝超薄势垒层是指6nm以下的氮化镓铝超薄势垒层,作为一种优选的实施方式氮化镓铝超薄势垒层为3~5nm的algan超薄势垒层;重掺杂p型氮化镓层为约10nm厚度的重掺杂p型氮化镓层。

41.对所述叠层结构的部分区域刻蚀至氮化铝截止层;在一些实施例中,将部分区域刻蚀至氮化铝截止层,形成了nmos的形成区域,而未刻蚀的区域,则形成了pmos的形成区域。在刻蚀后,还可以形成钝化层,即图2所示的结构。

42.在刻蚀区域制备源/漏电极以及栅电极形成nmos,在未刻蚀的区域制备源/漏电极以及栅电极形成pmos;并对所述nmos和所述pmos进行隔离;在一些实施例中,如图3-8所示,在刻蚀区域形成第一源/漏电极,即图3所示的结构,形成第一源/漏电极之后继续形成第二钝化层,即形成如图4所示的结构,对未刻蚀区域的第一钝化层和第二钝化层对应第二源/漏区域的部分进行刻蚀后形成第二源/漏电极,即形成如图5所示的结构。再对第一区域和第二区域之间进行隔离,例如可以采用台面隔离或者注入隔离的方式实现,即形成如图6所示的结构。随后,在第一区域和第二区域分别刻蚀栅槽和形成栅介质,依次形成如图7和图8所示的结构。最后在栅槽中形成栅电极即可形成nmos和pmos。

43.将所述nmos和所述pmos的栅电极通过导电金属进行电连接,将所述nmos和所述pmos的漏电极导电金属进行电连接。在一些实施例中,导电金属通过刻蚀通孔和凹槽后进行导电金属的填充形成,形成的结构如图9所示。

44.在本发明实施例提供的技术方案中,在单个衬底上实现了增强型nmos和pmos场效应晶体管的集成,氮化镓铝超薄势垒的引入在不但可以获得增强型的nmos器件,同时避免了pmos器件中二维电子气的存在,避免了在pmos器件在工作过程中二维电子气与二维空穴气之间的串扰,提高了cmos的整体可靠性,推动了氮化镓在数字集成电路领域的发展。

45.作为一种可选的实施方式,如图2-8所示,在刻蚀区域制备源/漏电极以及栅电极形成nmos,在未刻蚀的区域制备源/漏电极以及栅电极形成pmos包括:

46.在所述刻蚀区域和所述未刻蚀区域形成第一钝化层;在一些实施例中,覆盖了刻蚀区域和未刻蚀区域的上表面以及未刻蚀区域与刻蚀区域相邻的侧面,其结构如图2所示,

47.在所述刻蚀区域间隔的确定第一源/漏区域,对所述第一源/漏区域刻蚀至氮化镓缓冲及沟道层,并在所述第一源/漏区域形成第一源/漏电极;在一些实施例中,在刻蚀过程中,刻蚀了第一源/漏区域对应的第一钝化层、氮化铝截止层、氮化镓铝超薄势垒层以及氮化铝插入层,从而,在形成第一源/漏电极时,能使第一源/漏电极与氮化镓沟道及缓冲层电接触,其结构如图3所示。

48.在所述刻蚀区域和所述未刻蚀区域形成第二钝化层;在一些实施例中,第二钝化层覆盖了第一钝化层以及第一源/漏电极,其结构如图4所示。

49.在所述未刻蚀区域间隔的确定第二源/漏区域,对所述第二源/漏区域刻蚀至重掺杂p型氮化镓层,并在所述第二源/漏区域形成第二源/漏电极;在一些实施例中,刻蚀过程中刻蚀了第一钝化层和第二钝化层对应所述第二源/漏区域的部分,其结构如图5所示。

50.对刻蚀区域和未刻蚀区域的氮化铝插入层、氮化镓铝超薄势垒层和氮化铝截止层进行隔离。在一些实施例中,其隔离方式例如可以采用台面隔离或者注入隔离的方式,隔离后的结构如图6所示。

51.在所述第一源/漏区域之间确定第一栅极区域,并将第一栅极区域刻蚀至氮化镓铝超薄势垒层;在所述第二源/漏区域之间确定第二栅极区域,并将第二栅极区域刻蚀至重掺杂p型氮化镓层;在一些实施例中,第一栅极区域的刻蚀过程中,刻蚀了第一钝化层、第二钝化层以及氮化铝截止层的全部厚度。第二栅极区域的刻蚀过程中,刻蚀了第一钝化层、第二钝化层以及重掺杂p型氮化镓层的全部厚度,还刻蚀了p型氮化镓层的部分厚度。刻蚀完成后的结构如图7所示。

52.在所述第一栅极区域和所述第二栅极区域形成栅电极。形成栅电极的过程中,首先形成栅介质,其结构如图8所示,在形成栅介质之后,在凹槽内形成栅极金属即可形成栅电极。

53.上述提供了一种nmos和pmos的形成过程,但是,本领域技术人员应当能够理解,还可以采用其他的形式形成nmos和pmos,例如,将nmos和pmos按照任意的先后顺序形成。

54.作为一种可选的实施方式,第一源/漏电极为钛、铝、镍和金的叠层结构,或者,第一源/漏电极为钛、铝、钛和氮化钛的叠层结构。在一些实施例中,第一源/漏电极可以采用剥离工艺形成,并在形成后在n2氛围中用780~850℃的温度区间进行快速热退火,也可以采用ti/al/ti/tin叠层结构,采用剥离工艺形成,并在形成后在n2氛围中于550~600℃进行快速热退火。

55.作为一种可选的实施方式,第二源/漏电极为镍金叠层结构。第二源/漏电极可以采用剥离工艺并在o2氛围中于550~600℃的温度区间进行快速热退火。

56.作为一种可选的实施方式,栅电极为镍/金叠层、铂/钛/金叠层、铝/镍/金叠层或氮化钛。

57.作为一种可选的实施方式,所述第一钝化层为氧化铝和氧化硅中的一种或两种形成的膜层;所述第二钝化层为氮化硅和氧化硅中的一种或两种形成的膜层。在一些实施例中,第一钝化层可以是氧化铝或氧化硅等具有恢复二维电子气能力的介质,第二钝化层可以是氮化硅和氧化硅等的单一或复合介质,沉积方法采用化学气相沉积lpcvd,原子层沉积

ald或物理气相沉积pecvd等均可。

58.作为一种可选的实施方式,所述氮化镓铝超薄势垒层中的铝组分为10%~30%。在一些实施例中,氮化镓铝超薄势垒层和氮化镓沟道及缓冲层形成异质结构,其中,氮化镓铝超薄势垒层是3-5nm的薄超势垒层。

59.作为一种可选的实施方式,p型氮化镓层为镁掺杂的氮化镓层,其中,镁的浓度为3e

19

cm-3

~5e

19

cm-3

;

60.重掺杂的p型氮化镓层为镁掺杂的氮化镓层,其中,镁的浓度为1e

20

cm-3

~3e

20

cm-3

。

61.作为一种可选的实施方式,衬底为硅、碳化硅、蓝宝石或氮化镓中的一种或两种以上的叠层。作为另一种可选的实施方式,衬底也可以是其他平面型衬底。

62.本发明实施例还提供一种氮化镓基cmos结构,包括:

63.叠层结构,包括由下向上依次设置的衬底、氮化镓缓冲及沟道层、氮化铝插入层、氮化镓铝超薄势垒层、氮化铝截止层;所述叠层结构具有第一区域和第二区域;所述第一区域和第二区域的氮化铝插入层、氮化镓铝超薄势垒层及氮化铝截止层隔离设置;在一些实施例中,氮化铝插入层用于实现氮化镓缓冲及沟道层与氮化镓铝超薄势垒层的晶格适配,氮化铝截止层一方面能够阻止p型氮化镓中的掺杂物进入到氮化镓铝超薄势垒层,一方面能够作为刻蚀的截止层。在一些实施例中。在一些实施例中,氮化镓铝超薄势垒层为3~5nm的algan超薄势垒层。

64.所述第一区域具有第一源/漏区域,所述第一源/漏区域分别设置有与氮化镓缓冲及沟道层电接触的第一源/漏电极;第一源/漏电极贯穿所述氮化铝截止层、氮化镓铝超薄势垒层和所述氮化铝插入层,第一源/漏电极贯穿所述氮化铝截止层、氮化镓铝超薄势垒层和所述氮化铝插入层,所述第一源漏区域之间设置有第一栅极区域,所述第一栅极区域设置有与所述氮化镓铝超薄势垒层电接触的栅电极;

65.所述第二区域由下向上依次设置有p型氮化镓层和重掺杂p型氮化镓层,所述第二区域具有第二源/漏区域,所述第二源/漏区域分别设置有与重掺杂p型氮化镓层电接触的第二源/漏电极;所述第二源漏区域之间设置有第二栅极区域,所述第二栅极区域设置有与所述p型氮化镓层电接触的栅电极;第二栅极区域的栅电极贯穿部分p型氮化镓层;

66.其中,所述第一漏电极和所述第二漏电极通过金属线电连接,所述第一栅极区域的栅电极与第二栅极区域的栅电极通过金属线电连接。

67.在本发明实施例提供的技术方案中,在单个衬底上实现了增强型nmos和pmos场效应晶体管的集成,氮化镓铝超薄势垒的引入在不但可以获得增强型的nmos器件,同时避免了pmos器件中二维电子气的存在,避免了在pmos器件在工作过程中二维电子气与二维空穴气之间的串扰,提高了cmos的整体可靠性,推动了氮化镓在数字集成电路领域的发展。

68.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。