1.本发明涉及芯片技术领域,尤其涉及一种超低延迟的时钟域切换数据传输系统。

背景技术:

2.在摩尔定律逐渐放缓情况下,芯粒(chiplet)技术是系统级芯片(system on chip,简称soc)持续提高集成度和芯片算力的重要途径。超低延迟是芯粒技术的核心指标之一。超低延迟可以使得多个芯粒相互之间传输数据就像单颗芯片一样,几乎没有延迟。典型的芯粒协议标准ucie规定了从发送端的fdi接口到接收端的fdi(filt aware d2d interface)接口传输延迟为2ns。在现有的串行器(serdes)设计技术中,从并行数据的时钟域切换到串行数据的高速时钟域都是需要设置先入先出队列(fifo),但是,fifo的延迟是需要2个并行数据的时钟周期以上,这样的延迟难以满足芯粒协议要求。由此可知,如何实现超低延迟的时钟域切换数据传输成为亟待解决的技术问题。

技术实现要素:

3.本发明目的在于,提供一种超低延迟的时钟域切换数据传输系统,无需使用fifo,实现了超低延迟的时钟域切换数据传输。

4.根据本发明一方面,提供了一种超低延迟的时钟域切换数据传输系统,包括m个数字发送端{a1,a2,

…

,am,

…

,am}和模拟发射机,所述模拟发射机包括m个数据接收模块{b1,b2,

…

,bm,

…

,bm}、锁相环、分频器、并行时钟树、反馈时钟树和串行时钟树,所述并行时钟树、反馈时钟树和串行时钟树的时钟树结构相同;其中,am为第m个数字发送端,bm为第m个数据接收模块,m的取值范围为1到m,每一am均与原始时钟lclk连接,am基于原始时钟lclk发送并行数据,am的数据输出端与bm的数据输入端相连接;所述锁相环包括第一输入接口、第二输入接口和输出接口,所述锁相环的第一输入接口与原始时钟lclk相连接,所述锁相环的第二输入接口和反馈时钟fbclk相连,所述锁相环的输出接口分别与分频器的输入接口和串行时钟树的输入接口相连接;分频器的输出接口分别与并行时钟树的输入接口和反馈时钟树的输入接口连接,所述并行时钟树包括m个输出接口,并行时钟树的第m个输出接口与bm连接;反馈时钟树的输出接口与锁相环的第二输入接口相连接;所述串行时钟树包括m个输出接口,串行时钟树的第m个输出接口与bm连接;所述锁相环用于基于反馈时钟fbclk调整原始时钟lclk,并将调整后的原始时钟lclk乘以n,输出串行时钟sclk,n为预设的时钟翻倍数,n大于等于2;所述分频器用于将串行时钟sclk除以n,通过并行时钟树向bm发送并行时钟pclk,通过反馈时钟树向锁相环的第二输入接口发送反馈时钟fbclk;bm用于将am发送的并行数据转换为串行数据,并基于串行时钟sclk输出。

5.本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明提供的一种超低延迟的时钟域切换数据传输系统可达到相当的技术进步性及实用性,并具

有产业上的广泛利用价值,其至少具有以下有益效果:本发明所述系统通过设置与并行时钟树相同路径的时钟树反馈时钟树,并把反馈时钟树的路径放到锁相环的反馈路径,从而使数据接收模块接收的并行数据时钟的相位和数字发送端发送数据的时钟尽可能同步,不随工艺温度电压的变化而变化,从而可以准确的采样到输入数据,减少了数据的传输延迟。

附图说明

6.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

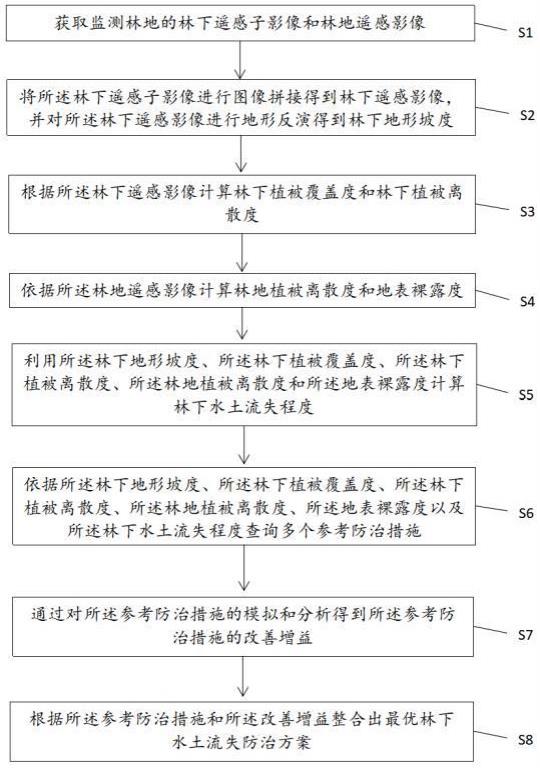

7.图1为本发明实施例提供的超低延迟的时钟域切换数据传输系统示意图;图2为本发明实施例一提供的超低延迟的时钟域切换数据传输系统示意图;图3为本发明实施例一提供的超低延迟的时钟域切换数据传输系统的时序图;图4为本发明实施例二提供的超低延迟的时钟域切换数据传输系统示意图;图5为本发明实施例二提供的超低延迟的时钟域切换数据传输系统的时序图。

具体实施方式

8.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

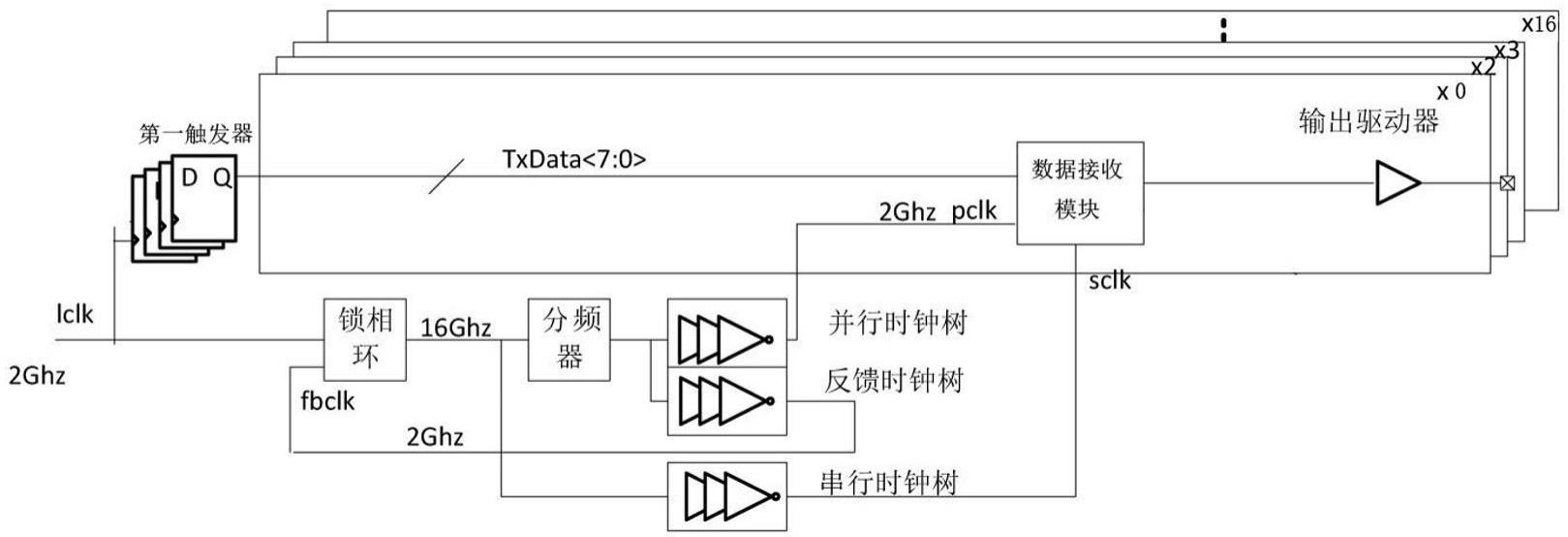

9.本发明实施例提供了一种超低延迟的时钟域切换数据传输系统,如图1所示示例,包括m个数字发送端{a1,a2,

…

,am,

…

,am}和模拟发射机,所述模拟发射机包括m个数据接收模块{b1,b2,

…

,bm,

…

,bm}、锁相环、分频器、并行时钟树、反馈时钟树和串行时钟树,所述并行时钟树、反馈时钟树和串行时钟树的时钟树结构相同,使得并行时钟树、反馈时钟树和串行时钟树具有尽可能相同的延迟。其中,am为第m个数字发送端,bm为第m个数据接收模块,m的取值范围为1到m,每一am均与原始时钟lclk连接,am基于原始时钟lclk发送并行数据txdata《k-1:0》,am的数据输出端与bm的数据输入端相连接。 需要说明的是,图1所示示例中,m=16,并行数据k=8,可以理解的是,这些数据可以根据具体应用需求来灵活调整。

10.所述锁相环包括第一输入接口、第二输入接口和输出接口,所述锁相环的第一输入接口与原始时钟lclk相连接,所述锁相环的第二输入接口和反馈时钟fbclk相连,所述锁相环的输出接口分别与分频器的输入接口和串行时钟树的输入接口相连接。

11.分频器的输出接口分别与并行时钟树的输入接口和反馈时钟树的输入接口连接,所述并行时钟树包括m个输出接口,并行时钟树的第m个输出接口与bm连接;反馈时钟树的输出接口与锁相环的第二输入接口相连接;所述串行时钟树包括m个输出接口,串行时钟树的第m个输出接口与bm连接。

12.所述锁相环用于基于反馈时钟fbclk调整原始时钟lclk,并将调整后的原始时钟lclk乘以n,输出串行时钟sclk,n为预设的时钟翻倍数,n大于等于2。图1所示示例中,原始

时钟lclk为2ghz,经过锁相环输出的串行时钟sclk为16ghz,n设置为8,串行时钟sclk经过分配其后得到的反馈时钟fbclk和并行时钟pclk均为2ghz。

13.所述分频器用于将串行时钟sclk除以n,通过并行时钟树向bm发送并行时钟pclk,通过反馈时钟树向锁相环的第二输入接口发送反馈时钟fbclk。

14.bm用于将am发送的并行数据转换为串行数据,并基于串行时钟sclk输出。

15.所述锁相环使得反馈时钟fbclk和原始时钟lclk的相位差小于等于预设的相位差阈值。

16.作为一种示例,所述模拟发射机还包括m个输出驱动器{c1,c2,

…

,cm,

…

,cm},cm为第m个输出驱动器,bm通过cm输出串行数据。

17.需要说明的是,原始时钟lclk通过锁相环、分频器、并行时钟树到达bm,延迟会随着工艺温度电压的变化而变化,从而使得bm采样接收am发送的数据很难满足bm中触发器的建立时间和保持时间需求。本发明通过增加反馈时钟树,向锁相环实时传输反馈时钟fbclk,使得锁相环基于反馈时钟fbclk动态调整原始时钟lclk,从而使得并行时钟pclk、反馈时钟fbclk、串行时钟sclk的上升沿尽可能对齐,即延迟保持在尽可能小的范围之内。将反馈时钟fbclk传输至锁相环,通过锁相环的环路特性调整使得反馈时钟fbclk和原始时钟lclk的上升沿尽可能对齐,即延迟保持在尽可能小的范围之内。这样使得,当工艺温度电压发生变化时,锁相环会自动补偿延迟变化,使得反馈时钟fbclk和原始时钟lclk的上升沿尽可能对齐。

18.数据接收模块可以设置为不同的结构,以下通过两个具体实施例来说明:实施例一、如图2所示示例,am包括第一触发器d1m,bm包括第二触发器d2m和并串转换器p2sm,d1m的数据输出端与d2m的数据输入端相连接,所述分频器通过并行时钟树向第二触发器d2m发送并行时钟pclk,第一触发器d1m和第二触发器d2m分别采用相反的时钟沿发送数据、接收数据,例如,第一触发器d1m采用上升沿发送并行数据,第二触发器d2m采用下降沿接收并行数据,或者,第一触发器d1m采用下降沿发送并行数据,第二触发器d2m采用上升沿接收并行数据。通过第二触发器d2m来接收并行数据,并串转换器p2sm基于第二触发器d2m接收到的并行数据转换我串行数据发出。

19.如图3所示,图2所示的系统需满足:[(锁相环的静态相差 并行时钟树和反馈时钟树的相差 并行时钟周期/2)-(第一触发器d1m的延迟 第一触发器d1m到第二触发器d2m之间数据线的延迟)]》第二触发器d2m的建立时间。以及[(并行时钟周期 第一触发器d1m的延迟)-(锁相环的静态相差 并行时钟树和反馈时钟树的相差 并行时钟周期/2)]》第二触发器d2m的保持时间。其中,锁相环的静态相差等于反馈时钟fbclk和原始时钟lclk的相位差,反馈时钟fbclk和原始时钟lclk的相位差小于等于预设的相位差阈值。并行时钟树和反馈时钟树的相差等于并行时钟pclk和反馈时钟fbclk的相位差。并行时钟周期为并行时钟pclk的周期,可以理解的是,原始时钟lclk、并行时钟pclk和反馈时钟fbclk的周期均相等,串行时钟的sclk的周期为并行时钟pclk的1/n。需要说明的是,第二触发器d2m的建立时间和第二触发器d2m的建立时间为第二触发器d2m的已知参数。锁相环的静态相差、并行时钟树和反馈时钟树的相差、并行时钟周期、第一触发器d1m的延迟、第一触发器d1m的延迟、第一触发器d1m到第二触发器d2m之间数据线的延迟(图3中简称数据线的延迟)可以根据设计调整,

且均是可以获取到的参数。

[0020]

实施例二、作为图2示例的一种变形,也可以直接基于并串转换器接收并行数据,如图4所示示例,am包括第一触发器d1m,第一触发器d1m用于发送k路并行数据,bm包括并串转换器p2sm,p2sm包括k个级联设置的第三触发器{d3

1m

,d3

2m

,

…

,d3

km

,

…

,d3

km

},其中,d3

km

为p2sm的第k个第三触发器,k的取值范围为1到k,所述分频器通过并行时钟树向d3

km

发送并行时钟pclk,并将并行时钟pclk作为d3

km

的选通信号,第一触发器d1m和并行时钟pclk分别采用相反的时钟沿发送数据、触发d3

km

接收数据。例如,第一触发器d1m采用上升沿发送并行数据,并行时钟pclk采用下降沿触发d3

km

接收数据,或者,第一触发器d1m采用下降沿发送并行数据,并行时钟pclk采用上升沿触发d3

km

接收数据。

[0021]

如图5所示示例,图4所示所述系统需满足:[(锁相环的静态相差 并行时钟树和反馈时钟树的相差 并行时钟周期/2)-(第一触发器d1m的延迟 第一触发器d1m到第二触发器d2m之间数据线的延迟)]和选通信号建立时间中的最小值,大于第三触发器d3

km

的建立时间。以及[(并行时钟周期 第一触发器d1m的延迟)-(锁相环的静态相差 并行时钟树和反馈时钟树的相差 并行时钟周期/2)]和选通信号保持时间的最小值,大于第三触发器d3

km

的保持时间。其中,选通信号建立时间=串行时钟sclk的周期-串行时钟sclk的上升沿到选通信号选通的延迟;选通信号保持时间=串行时钟sclk的上升沿到选通信号选通的延迟。锁相环的静态相差等于反馈时钟fbclk和原始时钟lclk的相位差,锁相环的静态相差小于等于预设的相位差阈值;并行时钟树和反馈时钟树的相差等于并行时钟pclk和反馈时钟fbclk的相位差;并行时钟周期为并行时钟pclk的周期。需要说明的是,第三触发器d3

km

的建立时间和第三触发器d3

km

的建立时间为第三触发器d3

km

的已知参数。锁相环的静态相差、并行时钟树和反馈时钟树的相差、并行时钟周期、第一触发器d1m的延迟、第一触发器d1m的延迟、第一触发器d1m到第二触发器d2m之间数据线的延迟(图5中简称数据线的延迟)、串行时钟sclk的上升沿到选通信号选通的延迟(图5简称sclk到load的延迟)可以根据设计调整,且均是可以获取到的参数,选通信号建立时间在图5中示为load建立时间,选通信号保持时间在图5中示为load保持时间。

[0022]

本发明实施例所述系统通过设置与并行时钟树相同路径的时钟树反馈时钟树,并把反馈时钟树的路径放到锁相环的反馈路径,从而使数据接收模块的接收的并行数据时钟的相位和数字发送端发送数据的时钟尽可能同步,不随工艺温度电压的变化而变化,从而可以准确的采样到输入数据,减少了数据的传输延迟。

[0023]

以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。