1.本公开内容涉及控制对电子设备的通用串行总线(usb)电力传输的集成电路(ic)。

背景技术:

2.各种电子设备(例如,诸如智能电话、平板电脑、笔记本计算机、膝上型计算机、充电器、适配器、电源组等)被配置成根据在usb电力传输(usb-pd)规范的各种版本和修订版本中定义的usb电力传输协议通过usb连接器传递电力。例如,在一些应用中,电子设备可以被配置为电力消耗者以通过usb连接器接收电力(例如,用于电池充电),而在其他应用中,电子设备可以被配置为电力提供者以通过usb连接器向连接至该电子设备的另一设备提供电力。在各种应用中,电子制造商还可能使用电力转换器(例如,诸如交流/直流(ac-dc)反激式转换器)从ac电网电源进行usb-pd。这样的转换器的效率已经变得越来越重要。这要求对初级功率晶体管和次级功率晶体管进行精确控制,而不管变压器的次级侧上的正弦波形中的正弦振荡(例如,振铃)如何。

技术实现要素:

3.本公开内容的一方面涉及一种用于反激式转换器的次级侧控制器,该次级侧控制器包括集成电路ic,该集成电路包括:同步整流器sr感测引脚,其耦接至反激式转换器的次级侧上的sr晶体管的漏极;电容器,其具有耦接至sr感测引脚的第一侧,该电容器响应于在sr感测引脚处感测的电压进行充电或放电;连接有二极管的晶体管,其耦接在电容器的第二侧与地之间;第一电流镜,其耦接至连接有二极管的晶体管,并且被配置成从可变电流源接收参考电流作为输入电流;以及峰值检测晶体管,其耦接至连接有二极管的晶体管并且耦接至第一电流镜的输出,其中,峰值检测晶体管响应于检测到来自电容器的电流下降低于参考电流而输出峰值检测信号。

4.本公开内容的另一方面涉及一种反激式转换器系统,包括:变压器;同步整流器sr晶体管,其耦接至变压器的次级侧;电容器,其耦接至sr晶体管,该电容器响应于从变压器的次级侧接收到的电压进行充电或放电;以及次级侧控制器,包括:sr感测引脚,其耦接至电容器;连接有二极管的晶体管,其耦接至sr感测引脚;第一电流镜,其耦接至连接有二极管的晶体管,并且被配置成从可变电流源接收参考电流作为输入电流;以及峰值检测晶体管,其耦接至连接有二极管的晶体管并且耦接至第一电流镜的输出,其中,峰值检测晶体管响应于检测到来自电容器的电流下降低于参考电流而输出峰值检测信号。

5.本公开内容的又一方面涉及一种操作用于反激式转换器的次级侧控制器的方法,该次级侧控制器包括:耦接至反激式转换器的次级侧上的同步整流器sr晶体管的sr感测引脚、耦接至sr感测引脚的电容器、耦接在电容器与地之间的连接有二极管的晶体管、第一电流镜、第一可变电流源、以及耦接至连接有二极管的晶体管并耦接至第一电流镜的输出的峰值检测晶体管,其中,操作次级侧控制器的方法包括:使电容器响应于在sr感测引脚处感

测的电压进行充电或放电;由第一可变电流源向第一电流镜的输入提供参考电流,其中,第一可变电流源被编程为生成参考电流,使得峰值检测晶体管在sr感测引脚处感测的电压的实际峰值处或在sr感测引脚处感测的电压的实际峰值前触发所述输出;由峰值检测晶体管检测来自电容器的电流下降低于参考电流;以及由峰值检测晶体管响应于所述检测输出峰值检测信号。

附图说明

6.图1a是描绘根据一些实施方式的生成电力开关(ps)信号以提高效率的包括次级侧控制器和同步反激式架构的ac-dc转换器的实施方式的示意性框图。

7.图1b是描绘根据一些实施方式的包括校准块的实施方式的图1a的次级侧控制器的一部分的示意性框图。

8.图2是示出根据实施方式的用于图1a和图1b的反激式转换器的控制方法的流程图。

9.图3是示出根据实施方式的当通过图2的方法操作时在图1a和图1b的电路中的到电力开关(ps)和同步整流器(sr)晶体管的栅极驱动信号随时间变化的图。

10.图4是示出根据实施方式的当由图1a和图1b的电路控制并通过图2的方法操作时在ps的漏极节点上的电压随时间变化的图。

11.图5是示出当由图1a和图1b的电路感测并通过图2的方法操作时在sr晶体管的漏极节点上的电压随时间变化的图。

12.图6是描绘根据至少一些实施方式的次级侧控制器的示意性框图。

13.图7是示出根据至少一个实施方式的包括图1的次级侧控制器的输入正弦波、ac信号电容器电流和峰值检测器输出的多个波形的图。

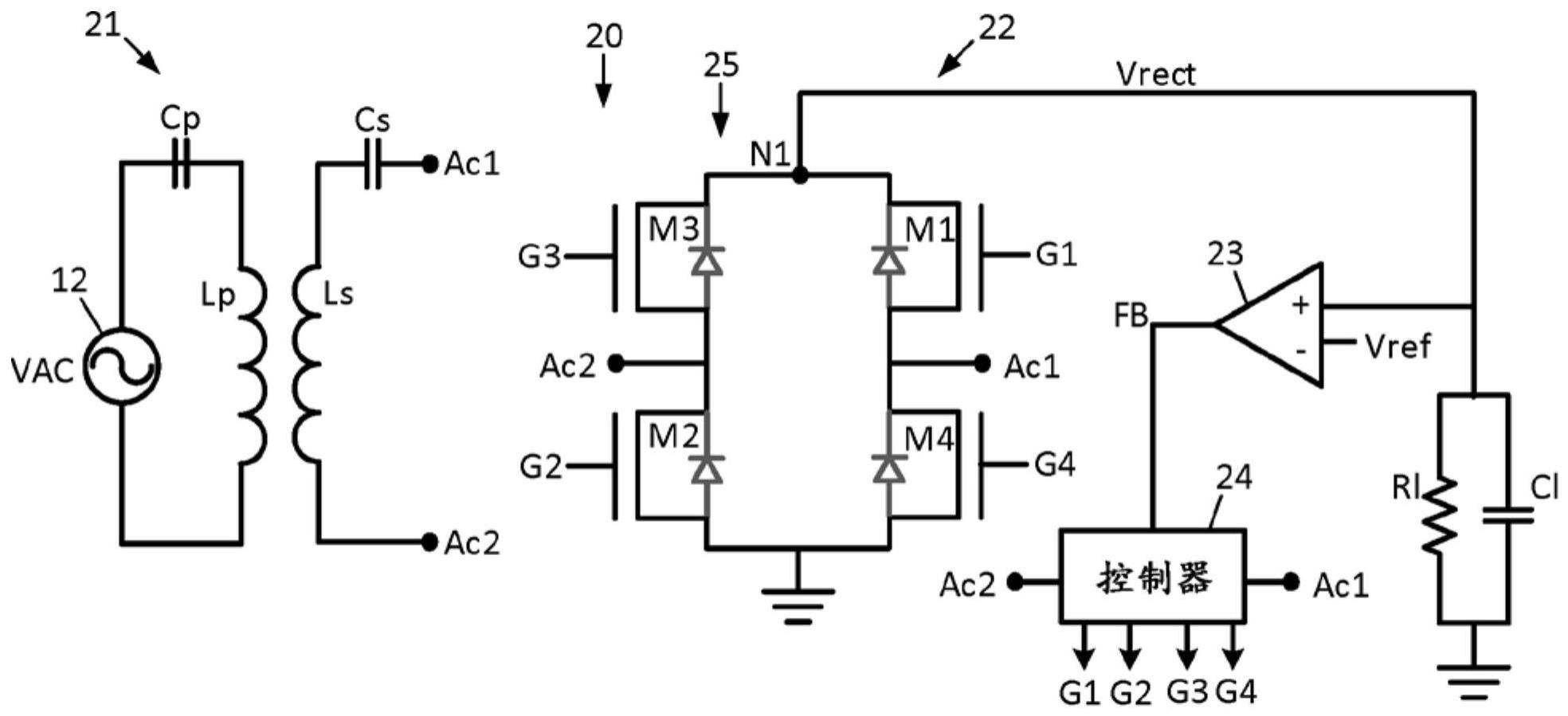

14.图8是描绘根据至少一个实施方式的反激式转换器系统的示意性框图。

15.图9是根据至少一个实施方式的对反激式转换器的次级侧控制器进行操作的方法的流程图。

具体实施方式

16.以下描述阐述了许多具体细节,例如具体系统、部件、方法等的示例,以便提供对本文描述的用于usb c型控制器的ac-dc反激式转换器的各种实施方式的良好理解。然而,对于本领域技术人员而言明显的是,可以在没有这些具体细节的情况下实践至少一些实施方式。在其他实例中,为了避免使本文描述的主题不必要地模糊,未详细描述或者以简单的框图格式呈现公知的部件、元件或方法。因此,在下文中阐述的具体细节仅是示例性的。特定实现方式可以根据这些示例性细节而变化,并且仍然被认为在本实施方式的精神和范围之内。

17.在描述中对“实施方式”、“一个实施方式”、“示例实施方式”、“一些实施方式”和“各种实施方式”的引用意指结合实施方式描述的特定特征、结构、步骤、操作或特性包括在至少一个实施方式中。此外,在说明书中各个地方出现的短语“实施方式”、“一个实施方式”、“示例实施方式”、“一些实施方式”和“各种实施方式”不一定全部指的是相同的实施方式。

18.描述包括对附图的参照,这些附图形成具体实施方式的一部分。附图示出了根据示例性实施方式的图示。以足够详细的方式对本文中也可以被称为“示例”的这些实施方式进行描述,以使得本领域技术人员能够实践本文描述的要求保护的主题的实施方式。在不脱离所要求保护的主题的范围和精神的情况下,可以对实施方式进行组合、可以利用其他实施方式或者可以进行结构、逻辑和电气改变。应当理解,本文描述的实施方式并不旨在限制主题的范围,而是使得本领域技术人员能够实践、制造和/或使用本主题。

19.本文描述了可以被设置成在各种电子设备中进行操作的usb c型控制器中的ac-dc反激式转换器的各种实施方式。这样的电子设备的示例包括但不限于个人计算机(例如,膝上型计算机、笔记本计算机等)、移动计算设备(例如,平板、平板计算机、电子阅读器设备等)、移动通信设备(例如,智能电话、移动电话、个人数字助理、消息收发设备、掌上个人电脑等)、连接和充电设备(例如,线缆、集线器、坞站、适配器、充电器等)、音频/视频/数据记录和/或播放设备(例如,摄相机、录音机、手持式扫描仪、监视器等)以及可以使用usb接口进行通信、电池充电和/或电力传输的其他类似电子设备。

20.如本文所使用,“usb使能”设备或系统是指包括usb连接器接口、配置有usb连接器接口或以其他方式与usb连接器接口相关联的设备或系统。usb使能的电子设备可以符合通用串行总线(usb)规范的至少一个发布版本。这样的usb规范的示例包括但不限于usb规范修订版本2.0、usb 3.0规范、usb 3.1规范、usb 3.2规范和/或其各种补充、版本和勘误。usb规范通常定义设计和构建标准通信系统和外围设备所需的差分串行总线的特性(例如,属性、协议定义、交易类型、总线管理、编程接口等)。例如,usb使能的外围设备通过usb使能的主设备的usb端口附接至该主设备以形成usb使能的系统。usb 2.0端口包括5v的电力电压线(表示为vbus)、数据线的差分对(表示为d 或dp以及d-或dn)以及用于电力返回的接地线(表示为gnd)。usb 3.0端口也提供vbus线、d 线、d-线和gnd线以用于向下兼容usb 2.0。另外,为了支持较快的差分总线(usb超高速总线),usb 3.0端口还提供了发送器数据线的差分对(表示为sstx 和sstx-)、接收器数据线的差分对(表示为ssrx 和ssrx-)、用于供电的电力线(表示为dpwr)以及用于电力返回的接地线(表示为dgnd)。usb 3.1端口提供与usb 3.0端口相同的线以向下兼容usb 2.0通信和usb 3.0通信,但是通过被称为增强型超高速的一系列特征扩展了超高速总线的性能。

21.在usb c型规范的各种发布版本和/或版本中定义了一种用于被称为usb c型(本文中也称为“usb-c”)的usb连接器的更新的技术。usb c型规范定义c型插座、c型插头和c型线缆,所述c型插座、c型插头和c型线缆可以支持通过在usb-pd规范的各种修订版本/版本中定义的较新的usb电力传输协议进行的usb通信以及电力传输。usb c型功能和要求的示例可以包括但不限于根据usb 2.0和usb 3.0/usb 3.1的数据和其他通信、关于c型线缆的机电定义和性能要求、关于c型插座的机电定义和性能要求、关于c型插头的机电定义和性能要求、关于c型对传统线缆组件和适配器的要求、关于基于c型的设备检测和接口配置的要求、关于优化的c型连接器的电力传输的要求等。根据usb c型规范,c型端口提供vbus线、d 线、d-线、gnd线、sstx 线、sstx-线、ssrx 线和ssrx-线等。另外,c型端口还提供用于边带功能的信令的边带使用(表示为sbu)线以及用于发现、配置和管理跨c型线缆的连接的配置信道(或通信信道,表示为cc)线。c型端口可以与c型插头和/或c型插座相关联。为了便于使用,c型插头和c型插座被设计为无论插头到插座的取向如何均可以操作的可逆对。因此,被

设置为标准c型插头或插座的标准usb c型连接器针对下述提供引脚:四根vbus线、四根接地返回(gnd)线、两根d 线(dp1和dp2)、两根d-线(dn1和dn2)、两根sstx 线(sstxp1和sstxp2)、两根sstx-线(sstxn1和sstxn2)、两根ssrx 线(ssrxp1和ssrxp2)、两根ssrx-线(ssrxn1和ssrxn2)、两根cc线(cc1和cc2)以及两根sbu线(sbu1和sbu2)等。

22.一些usb使能的电子设备可能符合特定修订版本和/或特定版本的usb-pd规范。usb-pd规范定义了下述标准协议,该标准协议被设计成通过usb c型端口在单根usb c型线缆上提供更灵活的电力传输以及数据通信来使得usb使能的设备的功能最大化。usb-pd规范还描述了用于管理通过usb c型线缆以高达100w功率进行电力传输所必需的架构、协议、电力供应行为、参数和线缆。根据usb-pd规范,与旧usb规范(例如,诸如usb 2.0规范、usb 3.1规范、usb电池充电规范1.1/1.2版等)中所允许的相比,具有usb c型端口的设备(例如,诸如usb使能的设备)可以通过usb c型线缆协商(negotiate)较多电流以及/或者较高电压或较低电压。例如,usb-pd规范定义了可以在一对usb使能的设备之间协商的针对电力传输合同(pd合同)的要求。pd合同可以指定电力水平和电力传输方向两者,所述电力水平和电力传输方向可以适应于两个设备并且可以根据由任一设备进行的请求和/或响应于各种事件和状况(例如,电力角色交换、数据角色交换、硬复位、电力源故障等)动态地重新协商(例如,无需设备解插)。如本文所使用的,“usb-pd子系统”是指一个或更多个逻辑块和其他模拟/数字硬件电路系统,其可以由ic控制器中的固件控制,并且其被配置且可操作成执行功能并满足usb-pd规范的至少一个发布版本中规定的要求。ic控制器可以在usb c型设备中实现。ic控制器可以在usb设备中实现。

23.根据usb-pd规范的电力传输可以以若干种不同类型的usb c型应用来实现。这种类型的c型应用的示例包括但可以不限于:下行端口(dfp)应用,其中具有usb pd子系统的ic控制器被配置成提供下行usb端口(例如,在usb使能的主设备中);上行端口(ufp)应用,其中具有usb-pd子系统的ic控制器被配置成提供上行usb端口(例如,在usb使能的外围设备或适配器中);双角色端口(drp)usb应用,其中具有usb-pd子系统的ic控制器被配置成在同一usb端口(例如,usb c型端口,其被配置成作为电力提供者或电力消耗者进行操作,或者可以通过使用usb-pd电力角色交换在这两个角色之间动态切换)上支持dfp应用和ufp应用两者;以及有源线缆应用,其中具有usb-pd子系统的ic控制器被置入并且被配置成操作电子标记线缆组件(emca)c型线缆。

24.在一些实施方式中,公开了具有包括单个sr-感测引脚(sr_sen)的次级侧控制和同步整流器(sr)架构的ac-dc转换器及其操作方法,以用于降低转换器的成本、复杂性和尺寸,同时提高效率。本公开内容的系统和方法在ac-dc反激式转换器中特别有用或者在具有ac-dc反激式转换器的情况下特别有用,以改进峰值检测和谷值检测,从而改进次级侧控制器对初级侧开关或初级fet的控制,以提高ac-dc反激式转换器的效率。

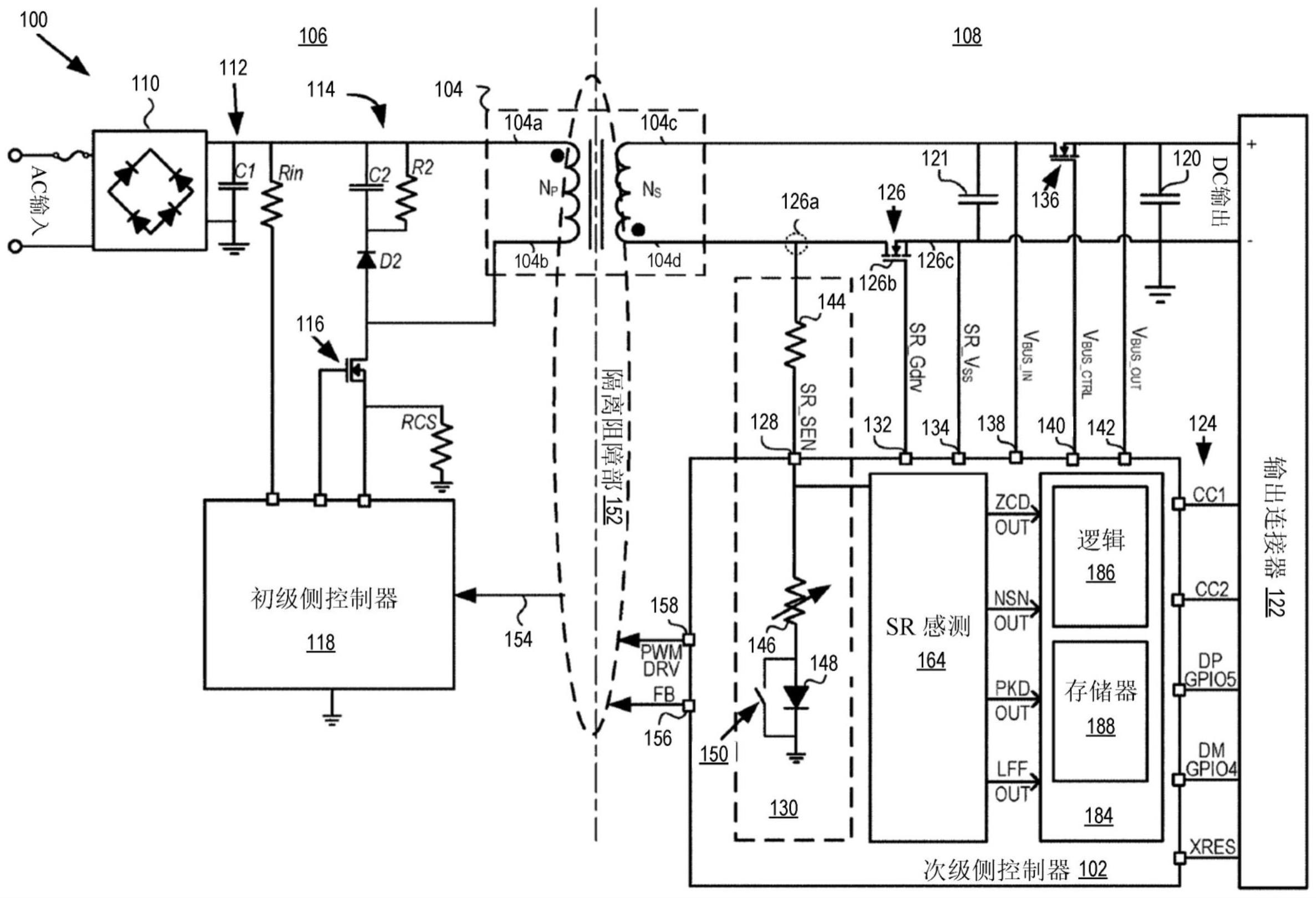

25.图1a是描绘根据一些实施方式的生成电力开关(ps)信号以提高效率的包括次级侧控制器102和同步反激式架构的ac-dc反激式转换器100的实施方式的示意性框图。图1b是描绘根据一些实施方式的包括校准块184的实施方式的图1a的次级侧控制器102的一部分的示意性框图。在这些实施方式中,次级侧控制器102被配置成生成初级场效应晶体管(fet)或电力开关(ps)信号,以提高峰值检测和谷值检测的准确性,并且因此提高反激式转换器100及其操作方法的效率。

26.参照图1a,反激式转换器100通常包括变压器104,该变压器104具有电连接或耦接至ac输入的初级侧106上的初级绕组(np)以及耦接至dc输出的次级侧108上的次级绕组(ns)。在初级侧106上,耦接至变压器104的第一端子104a的诸如桥式整流器110的整流电路以及一个或更多个输入滤波器112、114对ac输入电压进行整流,并且向变压器104的初级绕组供应输入电力。输入滤波器可以包括:第一输入滤波器112,其具有耦接至桥式整流器110的输出或跨桥式整流器110的输出的电容器(c1);以及第二rc滤波器114,其包括在变压器104的第一端子104a与二极管或整流器(d2)的阴极之间并联耦接的电阻器或电阻元件(r2)和电容器(c2),该二极管或整流器(d2)具有耦接至变压器的第二端子104b的阳极。

27.在一些实施方式中,反激式转换器100还包括诸如初级场效应晶体管(pr_fet)的电力开关(ps)116,所述电力开关(ps)116具有耦接至变压器104的第二端子104b的第一节点或漏极节点、耦接至初级侧控制器118的第二节点或栅极节点、以及耦接至初级侧控制器118并通过诸如电阻元件(rcs)的电流感测元件耦接至地的第三节点或源级节点,以在ps 116闭合或导电时感测流过初级绕组的初级侧电流(i_初级)。通常,如在所示的实施方式中,初级侧控制器118还通过电阻元件(rin)耦接至变压器104的第一端子104a,以接收相当于经整流的ac输入电压的或与经整流的ac输入电压成比例的电压或信号。

28.在这些实施方式中,反激式转换器100的次级侧108包括:滤波电容器121,其耦接在变压器104的第三端子104c与电接地或接地端子之间;以及输出电容器120,其通过诸如提供者mosfet的附加或次级开关(ss)136耦接在变压器104的第三端子104c与电接地或接地端子之间以向输出接口或输出连接器122提供dc输出电压。在至少一些实施方式中,输出连接器122还通过多个通信信道124耦接至次级侧控制器102,以支持各种充电协议。合适的输出连接器122可以包括兼容并支持下述标准和专有充电协议的连接器,所述标准和专有充电协议包括具有可编程电力供应(pps)的通用串行总线电力传输usb pd 2.0和usb pd 3、quick charge、afc和充电协议。例如,连接器可以包括通用串行总线c型(usb-c)兼容性连接器,其中,反激式转换器100符合usb协议以在从约300毫安(ma)至约5000毫安(ma)的电流下提供约3.3vdc至约28vdc的dc输出电压。

29.根据一些实施方式,反激式转换器100的次级侧108还包括耦接在变压器104的第四端子104d与dc输出的接地端子之间的同步整流器例如至少包括同步整流器场效应晶体管(sr_fet 126)的电路。sr_fet 126包括:第一节点或漏极节点例如sr_drain节点126a,其耦接至变压器104的第四端子104d和次级侧控制器102以感测sr_fet 126的漏极上的电压;第二节点或栅极节点126b,其耦接至次级侧控制器以驱动或控制sr_fet 126;以及第三节点或源极节点126c,其耦接至次级侧控制器102和dc输出的接地端子。

30.在某些实施方式中,次级侧控制器102被实现或实施为单个集成电路(ic)或者被实现或实施为封装在单个ic封装中的多个ic,并且sr_drain节点126a通过分压器130耦接至ic的单个sr感测引脚128(例如,sr_sen引脚),该分压器130既包括次级侧控制器的ic内部的电路元件也包括次级侧控制器的ic外部的电路元件。在这些实施方式中,sr_fet 126的栅极节点126b通过sr-驱动引脚132耦接至次级侧控制器102,而sr_fet 126的源极节点126c通过sr_vss(负电压供应)引脚134耦接至次级侧控制器。

31.可选地,在一些实施方式中,次级侧108还包括诸如nfet的附加或次级开关(ss)136,所述附加或次级开关(ss)136耦接在变压器104的第三端子104c与正dc输出之间,以使

得次级侧控制器102能够关断dc输出以使得免受过电压和/或欠电压状况以及/或者过电流状况和/或短路状况。ss 136包括:漏极节点,其耦接至次级侧控制器102的电压总线输入引脚(v

bus_in

)138;栅极节点,其耦接至电压总线控制引脚(v

bus_ctrl

)140以驱动或控制ss 136;以及源极节点,其耦接至电压总线输出引脚(v

bus_out

)142和dc输出的正极端子。

32.在至少一些实施方式中,分压器130包括外部电阻元件144、内部电阻元件146和内部整流器148。尽管示意性地示出为二极管,但应当理解,在每个实施方式中不必都是这种情况,并且应当理解,内部整流器148可以是pn二极管(如图所示)或者可替选地是同步二极管或者被配置或连接成用作二极管的fet。内部整流器148的配置或放置——即阴极接地连接——确保了在负感测或过零操作期间基本上没有电流流过分压器130,从而允许sr_drain节点126a上的完整的未分压负电压耦接至sr感测引脚128。

33.在各种实施方式中,外部电阻元件144的电阻值由反激式转换器100的制造商固定并且基于预期的最大ac电压输入、变压器104的匝数比来选择以限制sr_drain节点126a上的最大电压,这限制了sr感测引脚128上的最大电压,以使得能够利用非超高电压设备技术制成次级侧控制器102,例如使用标准的、更低的电压技术制成次级侧控制器102。电阻元件144的电阻的合适值为从约4kω至约101kω。例如,在一个实施方式中(其中,桥式整流器110之后的最大输入电压为380v以及变压器104的匝数比为4:1),而v

bus_in

上的电压为21.5v dc,sr_drain节点126a的电压为116.5v。在一些实施方式中,次级侧控制器102可以使用20v的容错技术来制造,并且外部电阻元件144可以具有约10kω的电阻,以将sr_drain节点126a上的最大电压限制成不超过约21.5v。

34.在一些实施方式中,在图1a中示意性地示出为可变电阻的内部电阻元件146具有由制造商在基于期望输入电压或输出电压制造反激式转换器100时设置的电阻值,或者具有用于补偿反激式转换器100中的ic或其他部件的参数变化的电阻值。可替选地,内部电阻元件146的电阻值可以由反激式转换器100或次级侧控制器102中的校准电路在反激式转换器启动或通电时动态地调整或者在反激式转换器启动或通电之后周期性地调整。

35.可选地,如在所示的实施方式中,分压器130还包括与内部整流器148并联的开关元件或开关150。响应于在检测到漏极sr_drain126a上升高的或非零的正电压(这指示前馈操作)时在次级侧控制器102中生成的ff-信号(ff_enable),开关150在前馈(ff)感测期间闭合。尽管内部整流器148和开关150被示意性地示出为两个单独且不同的元件,但不必总是这样的情况。在至少一些实施方式中,内部整流器148和开关150交替地包括有单个器件例如fet,其中,开关150由fet形成,并且内部整流器148由fet的源极与漏极之间的本征体二极管形成。

36.在至少一些实施方式中,参照图1a,反激式转换器100还包括隔离电路或阻障部152,以将次级侧108与在初级侧106上出现的高ac输入电压电隔离。因为变压器104是降压变压器,所以变压器104通常被认为是隔离阻障部152的一部分。附加地,如所示,转换器100是反激式转换器,其中,信号154从次级侧控制器102上的引脚例如反馈引脚156或脉冲宽度调制(pwm)驱动引脚158提供至初级侧控制器118。隔离阻障部152还可以包括在次级侧控制器102与初级侧控制器118或ps 116之间的附加电路或元件。隔离阻障部152可以包括例如光隔离器或脉冲变压器。在其他实施方式中,可以实现可以或可以不包括这些图中示出的所有元件和部件的隔离阻障部152。

37.参照图1b,根据一些实施方式,如在图1a中示出的次级侧控制器102和sr感测块164中,次级侧控制器102还包括从其分别提供pwm_drv信号和反馈(fb)信号并且通过隔离阻障部152耦接至初级侧控制器118的pwm电路160和反馈(fb)电路162,所有这些与次级侧控制器102的其他部件和元件一体地形成在单个ic上。

38.在各种实施方式中,sr感测块164包括过零检测器(zcd)块166、负信号(nsn)块168、峰值检测器(pkd)块170和线前馈(lff)块172。zcd块166(例如,zcd电路)可以包括比较器,该比较器具有通过sr_vss引脚134耦接至sr_fet 126的源极节点126c的第一反相输入以及耦接至sr感测引脚128并且通过分压器130耦接至sr的sr_drain节点126a的第二非反相输入。在其中sr_drain节点126a处于负电压并且朝向0v倾斜的zcd检测阶段期间,内部整流器148保持启用而不启用开关150,以使得分压器130中无分压。这在zcd比较器的非反相输入处实现了sr_drain节点126a的直接电压。zcd块166的比较器可以被配置成当在无任何分压的情况下在sr感测引脚128和sr_drain节点126a上感测零电压时生成零电流信号(zcd_out)以关断sr_fet 126。无分压使得能够精确地检测sr_drain节点126a的过零电流或过零电压,这提高了反激式转换器100的效率。

39.nsn块168也可以包括比较器,该比较器具有耦接至sr感测引脚128并且通过分压器130耦接至sr_fet 126的sr_drain节点126a的第一反相输入,以及耦接至负参考电压(vtnesn)的第二非反相输入,该负参考电压可以在-700mv至 200mv之间。该参考电压vtnesn可以被定义成期望的负电压跳变点,在该期望的负电压跳变点处,控制器需要导通耦接至栅极节点126b的sr_gdrv。用于负参考电压的可替选方法可以是例如将通过sr_vss引脚134耦接的非反相输入连接至sr_fet 126的源极节点126c,并且比较器可以具有内置偏移以在sr感测引脚128处于负参考电压时跳变。在其中sr_drain节点126a从正电压变成负电压的nsn检测阶段期间,内部整流器148可以保持启用而不启用开关150,以使得在分压器130中无分压。这在nsn比较器的反相输入(例如,从sr感测引脚128)处实现了sr_drain节点126a的直接电压。nsn比较器生成负电压信号(nsn_out)以导通sr_fet 126。

40.在次级侧上的电力传输期间,当sr_fet 126关断时,并且由于ps 116尚未导通,因此导致sr_drain节点126a上的lc正弦振荡以及反激式变压器104的初级端子104b上的反向正弦。为了提高ac-dc转换器效率,当在这些正弦振荡中存在谷值(其对应于次级sr_drain节点126a上的峰值)时,导通电力开关116。pkd块170是次级侧108上的峰值感测块。pkd块170也可以包括比较器,该比较器具有通过开关175和内部电容器174耦接至sr感测引脚128并且通过分压器130的第一反相输入,以及耦接至地的第二非反相输入。通常,如在所示的实施方式中,pkd块170还包括在比较器的第一输入与第二输入之间的背靠背连接的二极管电路176,以检测在sr感测128上可见的正弦波形的峰值。比较器被配置成生成峰值电压检测信号(pkd_out),其可以被耦接至初级侧控制器118以导通ps 116来启用谷值切换操作模式。开关175在nsn和zcd检测阶段期间保持关断,以避免在sr感测引脚128上的由pkd块提供的电容性负载,从而使在感测操作的负感测模式(nsn)和/或过零检测(zcd)方面的任何延迟减少,从而提高反激式转换器100的性能和效率。通过使用在zcd_out决定sr_fet 126的关断时的导出信号形式的zcd_out,在峰值检测功能期间导通开关175,在这之后lc正弦振荡可以发生。

41.最后,ac线前馈(lff)块172可以包括电压至电流(v2i)块,该电压至电流(v2i)块

通过开关178、使用二极管元件180以及电荷-存储元件(电容器182)的采样和保持电路耦接至sr感测引脚128,并且通过分压器130耦接至sr_fet 126的sr_drain节点126a。在当电力开关116导通时的阶段期间,根据反激式变压器104的匝数比(n),反激式变压器100的第四端子104d与第三端子104c之间的差异在变压器104的第一端子104a上形成线输入整流电压的成比例的反射电压。由于第四端子104d也耦接至sr_drain节点126a,该sr_drain节点126a用作在电阻分压器130之后的次级侧控制器102内的感测节点,因此sr感测引脚128节点也携带使用lff块172导出的线输入电压信息。可以由次级侧控制器102使用线输入信息来改变谷值切换或pwm脉冲宽度,以跨可变的ac线输入优化反激式转换器100的效率。

42.在各种实施方式中,电力开关116导通并且sr_drain节点126a获得反射的成比例电压的阶段被定义为前馈感测阶段,并且在该阶段期间,开关178导通以经由sr感测引脚128开始感测线输入电压。同时,开关150也导通以旁路内部整流器148,以允许sr_drain节点126a的精确电阻分压版本到达lff块172的输入处。开关178在nsn和zcd检测阶段期间保持关断,以避免在sr感测引脚128节点上的由lff块提供的电容性负载,这有助于使感测nsn和zcd的延迟减少,并且提高反激式转换器100的性能和效率。lff块172被配置成当反激式转换器100在前馈感测模式下进行操作时生成电流信号(iff_out)。然后,该iff_out电流可以用于根据每线ac电压来调节pwm脉冲宽度,这在宽范围的ac输入电压范围内提高了ac-dc转换器的性能和效率。iff_out电流也可以被转换成与线ac输入电压成比例的电压,并且可以用于次级侧控制器102上所需的任何功能,例如用于针对相同的输出电力要求基于线ac电压来改变ps 116以其导通的谷值,以提高反激式转换器100的性能。

43.根据一些实施方式,次级侧控制器102还包括校准块184,该校准块184包括逻辑电路186(例如,控制逻辑)和在存储器188中存储的指令。校准块184可以被配置成执行校准,以测量回路回转延迟(tloop)以及为响应于在sr_fet 126的sr_drain节点126a上感测的电压导通ps116的信号设置定时。由于在初级侧上谷值出现紧接着导通ps 116并且使得在sr_fet 126的sr_drain节点126a上感测的电压上升,因此可以在校准块184中通过以下测量tloop:对从信号被发送以导通ps时的时间起直至在sr_fet 126的sr_drain节点126a上感测的电压如通过在ccm模式下由zcd块166检测到过零所指示的那样上升时的时间为止的延迟进行测量。例如,在图3、图4和图5中的时间t5与时间t1之间示出tloop。后校准,诸如存储在存储器188中的固件的指令可以被执行,以参照通过zcd块166的过零来计算针对用于导通ps 116的后续信号的精确定时,从而确保在初级侧上的谷值处或在谷值附近导通ps并提高反激式转换器100的效率。

44.通常,在至少一些实施方式中,校准块184参照过零电压准确地确定或检测初级侧106上的谷值。关于校准之后的第一谷值(第1谷值)的定时如下面的公式中所示:

45.第1谷值=tzpk-tloop

46.其中,tzpk是从在校准之后首次感测过零时到在校准循环之后在sr_fet126的sr_drain节点126a上感测第一峰值电压时的时间。例如,在图5中,tzpk被示出在时间t2与t3之间。

47.针对在第一谷值之后的后续谷值(第n谷值)的定时如下面的公式中所示:

48.第n谷值=tzpk-tloop (n-1)tpkpk

49.其中,n是2或更大的整数,以及tpkpk是当在sr_fet 126的sr_drain节点126a上感

测两个连续峰值电压时之间的时间。例如,在图5中,tpkpk的示例被示出在时间t3与t4之间。

50.从上面应当理解,校准循环还包括确定tzpk的值和tpkpk的值。在一个实施方式中,校准块184可以通过以下直接测量tzpk:对从使用zcd块166在sr_fet 126的sr_drain节点126a上感测过零时直至由pkd块170首次感测峰值电压时的时间为止进行测量。类似地,校准块184可以通过以下直接测量tpkpk:对如由pkd块170感测的在sr_fet 126的sr_drain节点126a上感测两个连续峰值电压时之间的时间进行测量。附加地,在一些实施方式中,校准循环包括重复地对tpkpk多次迭代进行测量,以获得两个连续峰值电压之间的时间的平均值(tpkpk

avg

),从而进一步提高初级侧106中的谷值检测的准确性和反激式转换器利用其进行操作的效率。

51.在替选实施方式中,由于在反激式转换器通电之后在初级侧上的电感-电容(lc)或谷值振铃取决于具有固定值(即初级侧的电感(lprim)和初级fet或ps 116的漏极节点的电容)的外部部件,因此可以针对特定应用或反激式转换器100计算或测量在第一过零与第一峰值电压之间的时间(tzpk)以及两个连续峰值电压之间的时间(tpkpk)并且将它们作为到存储器188的输入被存储而非被测量。

52.现在将参照图2和图3至图5的流程图描述用于操作包括次级侧控制器的反激式转换器的方法。图3是示出当通过图2的方法操作时在图1a的电路中到初级fet或ps 116的栅极驱动信号302和到sr_fet 116的栅极驱动信号304的图。图4是示出在ps 116的漏极节点上产生的初级漏极电压402随时间变化的图,以及图5示出了当由图1的电路感测并通过图2的方法操作时在sr_fet 126的漏极节点上的次级漏极电压502。

53.图2是示出根据实施方式的用于图1a和图1b的反激式转换器的控制方法的流程图。参照图2,在反激式转换器100通电之后,方法开始执行校准循环200。通常,校准循环200涉及至少三个操作,这些操作可以同时地或以任何次序顺序地执行。校准循环的三个操作包括对从次级侧控制器102给出pwm信号到在耦接至次级侧108的sr_fet 126的sr_drain节点126a上感测过零(zcd)电压时的时间之间的回路回转延迟(tloop 504)进行测量的第一操作202。例如当次级侧控制器102在时间t5处发送栅极驱动信号(图3中的302)时,因为sr_drain节点126a因为在初级侧106中导通的ps 116而升高,导致产生的初级漏极电压(图4中的402)在时间t6处下降,这可以在反激式转换器100在连续导电模式(ccm)模式下进行操作的同时在时间t6处作为过零(图5中的zcd 516)而被检测到。

54.校准循环的三个操作还包括确定在sr_fet 126的漏极上感测的第一过零(图5中的zcd 511)与第一峰值电压(图5中的510)之间的时间(tzpk 506)的第二操作204。最后,三个操作校准循环中的第三操作206包括确定在sr_fet 126的漏极上感测的两个连续峰值电压(例如,图5中的510和514)之间的时间(图5中的tpkpk 512)。

55.再次参照图2,在校准循环之后,基于tloop、tzpk和tpkpk计算针对用于导通ps的信号的定时(操作208),以及关于在sr_fet 126的漏极节点上最近感测的过零生成信号(操作210)以便在期望数量的谷值处或非常接近期望数量的谷值处导通初级fet(ps 116),这有助于提高ac-dc反激式转换器的效率和性能。

56.参照图5,由于导通ps 116(初级fet)使sr_drain节点126a处的电压上升,因此次级侧控制器的硬件可以在操作204中通过以下测量回路回转延迟(tloop)504:对从次级控

制器发送导通ps 116的栅极驱动信号(例如,在图4中在初级漏极电压402处)时的时间(t5)起直至在反激式转换器在连续导电模式(ccm)模式下进行操作的同时sr_drain节点126a过零(图5中的zcd 516)时的时间(t6)为止的延迟进行测量。

57.类似地,可以在操作204中通过次级侧控制器102中的硬件对在时间(t2)处的第一过零(图5中的zcd 511)与在时间(t3)处的sr_drain节点126a上感测的第一峰值电压510之间的时间(tzpk 506)进行测量,并且可以在操作206中对从时间(t3)至时间(t4)的两个连续峰值电压510与514之间的时间(tpkpk 512)进行测量。附加地,在一些实施方式中,校准循环200包括重复操作206多次以测量多个峰值到峰值延迟,以获得两个连续峰值电压之间的时间(tpkpk)的平均值,从而进一步提高初级侧106中的谷值检测的准确性和反激式转换器利用其进行操作的效率。

58.在替选实施方式中,由于在反激式转换器通电之后在初级侧上的电感-电容(lc)或谷值振铃取决于具有固定值(即初级侧的电感(lprim)和初级fet或ps 116的漏极节点的电容)的外部部件,因此可以针对特定应用/转换器计算或测量在第一过零与第一峰值电压之间的时间(tzpk)、以及两个连续峰值电压之间的时间(tpkpk),并且将它们作为到存储器例如次级侧控制器的固件的输入给出而非由次级侧控制器中的硬件进行测量。

59.在至少一些实施方式中,如所讨论的,初级fet或ps 116应当在sr_fet 126的sr_drain节点126a处的峰值处导通,以使开关损耗最小化并因此实现最优效率。使用低初级电感的变压器104和低初级开关电容(例如,coss)的高频转换器具有2mhz至10mhz范围内的正弦振铃频率。在这样的情况下,为了实现最优效率,应当寻求次级侧108上的高速准确峰值检测。否则,当延迟导通ps 116时,在初级侧上会引入损耗。因此,对峰值检测器(pkd)块170进行增强以实现6mhz至10mhz的附加操作带宽。

60.此外,从次级峰值检测到ps 116导通的感测延迟和路径延迟导致相当数量的频率大于3mhz的峰值缺失,进而导致潜在的相当的效率损失。换言之,高频引起从次级峰值检测到ps 116导通的延迟。附加地,为了准确的零电压感测(zvs)开关,应当在sr_fet 126处实现准确的谷值感测,以使sr_fet 126中的电力损耗减小。参照图6至图9示出并讨论了高速的基于电流的感测架构,以检测反激式转换器100的次级侧108上的sr_drain节点126a处的高频峰值和谷值。

61.图6是描绘根据至少一些实施方式的次级侧控制器602的示意性框图。例如,次级侧控制器602包括例如峰值和谷值检测器块670,而不是pkd块170(图1b)。在这些实施方式中,次级侧控制器602是ic,正如参照次级侧控制器102(图1a至图1b)所讨论的。该次级侧控制器602包括耦接至反激式转换器100的次级侧108上的sr晶体管(例如,sr_fet126)的漏极的同步整流器(sr)感测引脚128(例如,sr_sen引脚)。在至少一些实施方式中,次级侧转换器602被配置成控制反激式转换器100以提供与通用串行总线c型标准(usb-c)兼容的直流(dc)输出,正如本文中参照图1a至图5进一步详细讨论的。

62.在这些实施方式中,次级侧控制器602包括耦接至sr感测引脚128的可变电阻器(例如,内部电阻部件146),其中,可变电阻器是耦接在sr晶体管(例如,sr_fet 126)的漏极与sr感测引脚128之间的分压器630的一部分。次级侧控制器602还包括耦接在可变电阻器与地之间的例如其阴极耦接至地的二极管(例如,内部整流器148)。在一些实施方式中,分压器630是先前参照图1a至图1b讨论的分压器130的至少一部分。

63.此外,在至少一些实施方式中,峰值和谷值检测器块670包括具有耦接至sr感测引脚128的第一侧的电容器cp,电容器cp响应于在sr感测引脚128处感测的电压进行充电或放电。连接有二极管的晶体管n1耦接在电容器cp的第二侧与地例如gnd之间。在这些实施方式中,第一电流镜604耦接至连接有二极管的晶体管n1,并且被配置成从可变电流源606接收参考电流作为输入电流。在一些实施方式中,峰值检测晶体管n2具有耦接至连接有二极管的晶体管n1的栅极并耦接至第一电流镜604的输出的栅极,其中,峰值检测晶体管n2响应于检测到来自电容器cp的电流下降低于参考电流而输出峰值检测信号。

64.因此,通过电容器cp的通过输入正弦波(参见图7)注入的ac信号电流由n2反映并与供应有来自可变电流源606的可编程idac的参考电流的第一电流镜604进行比较。来自电容器cp的该ac电流信号可以变成零,并且然后变成负电流,如图7中所示。当电容器cp电流首先达到零,这对应于峰值电压输入(vin)。当输入正弦波达到其峰值时,跨cp的电压随时间的变化减小,并且信号电流减小至低于参考电流,引起峰值-检测信号升高,如图7中的峰值_检测输出信号所示。

65.在一些实施方式中,可变电流源606是电流数字-模拟转换器(idac),该电流数字-模拟转换器被编程为生成参考电流使得峰值检测晶体管n2在sr感测引脚128处感测的电压的实际峰值处或在sr感测引脚128处感测的电压的实际峰值前触发输出。因此,在一些实施方式中,电流参考以较低的电流(或iref)值被编程,使得检测峰值比实际峰值稍早,例如,将图7的峰值检测输出信号稍微向左移动。这是用于补偿反激式转换器100中的检测延迟和/或路径延迟且便于提高开关效率的一种方式。

66.如参照图1a至图1b所讨论的,pwm驱动引脚158可以被配置成驱动反激式转换器100的初级侧106中的电力开关(ps)116。此外,校准块184的控制逻辑186可以耦接至峰值检测晶体管n2,类似于在图1b中将来自pkd块170的比较器的pkd输出信号耦接至校准块184。因此,峰值和谷值检测器块670可以被理解为对pkd块170的可选替代。在这些实施方式中,控制逻辑186被配置成响应于峰值检测晶体管n2的输出峰值检测信号经由pwm驱动引脚158向ps 116发送导通信号。

67.在各种实施方式中,如参照图1a所讨论的,zcd块166被配置成检测在sr感测引脚128处感测的电压的过零。峰值和谷值检测器块670还可以包括可编程的并且耦接至峰值检测晶体管n2的输出的延迟电路622。例如,延迟电路622可以被编程以提供总延迟,所述总延迟包括:i)回路回转延迟(tloop),其被确定为从导通信号被发送至ps 116时到在sr感测引脚128处感测到电压过零时的时间;以及ii)峰值到峰值延迟(tpkpk),其被确定为峰值检测晶体管n2在sr感测引脚128处感测的电压的峰值之间的时间。此外,为了检测启动之后的第一峰值,初始总延迟可以包括:估计的回路回转延迟(例如,被预编程为预期初始tloop延迟)和过零到峰值延迟,所述过零到峰值延迟被确定为从在sr感测引脚128处感测到电压过零时到峰值检测晶体管n2检测到第一峰值的时间。这些是用于补偿检测延迟和路径延迟——特别是用于补偿频率高于3mhz的检测延迟和路径延迟的附加方式。

68.根据至少一些实施方式,峰值和谷值检测器块670还包括耦接在电容器cp与地之间的二极管650,例如,其中,二极管650的阴极耦接至电容器cp的第二侧,而二极管650的阳极耦接至地。峰值和谷值检测器块670还包括第二电流镜612,该第二电流镜612从第二可变电流源616接收第二参考电流作为输入电流。峰值和谷值检测器块670还包括谷值检测晶体

管n3,该谷值检测晶体管n3具有耦接至地的栅极、耦接至连接有二极管的晶体管的源极、以及耦接至电流镜612的输出的漏极,其中,谷值检测晶体管n3的漏极响应于二极管650处的电压(例如,vdiode)朝向负电压摆动而转变成低电压,以及响应于二极管处的电压朝向正电压摆动返回而转变成高电压。

69.因此,当ac信号摆动低时,电容器cp的另一端(在vdiode处)朝向负0.7v(例如,-0.7v)摆动。作为谷值检测晶体管n3的nmos的vgs足够高以吸取电流并且下拉谷值_检测输出信号。当ac信号在该谷值之后摆动高时,vdiode节点上升。随着nmos(n3)的vgs减小,跨n3的信号电流也减小,并且谷值检测升高。

70.在至少一些实施方式中,峰值和谷值检测块670还包括可编程的并且耦接至谷值检测晶体管n3的输出的第二延迟电路632。例如,第二延迟电路632可以被编程以提供总延迟,所述总延迟包括:i)回路回转延迟(tloop),其被确定为从导通信号被发送至ps 116时到在sr感测引脚128处感测到电压过零时的时间;以及ii)峰值到峰值延迟(tpkpk),其被确定为峰值检测晶体管n2在sr感测引脚128处感测的电压的峰值之间的时间。此外,为了检测启动之后的第一谷值,初始总延迟可以包括估计的回路回转延迟(例如,被预编程为预期初始tloop延迟)和被确定为从在sr感测引脚128处感测到电压过零时到峰值检测晶体管n2检测到第一谷值的时间的过零到谷值延迟。这些是用于补偿检测延迟和路径延迟——特别是用于补偿频率高于3mhz的检测延迟和路径延迟的附加方式。

71.图8是描绘根据至少一个实施方式的反激式转换器系统800的示意性框图。在该实施方式中,反激式转换器系统800类似于反激式转换器100和次级侧控制器602。然而,在该实施方式中,替代采用未采用分压器130或内部电容器cp的稍微改变的控制器(例如,次级侧控制器802)。替代地,在sr_fet 126的sr_drain节点126a与sr感测引脚128之间采用外部电容器cext。外部电容器cext耦接至sr晶体管(sr_fet 126),电容器cext响应于从变压器104的次级侧108接收到的电压进行充电或放电。现在,次级侧控制器802替代地采用峰值和谷值检测器块870,该峰值和谷值检测器块870不包括内部电容器cp,而是耦接至外部电容器cext。该替选实施方式可以被采用以用于甚至更高频率(例如,通常在5mhz或高于5mhz)的应用,并且/或者适合于基于氮化镓(gan)的fet ad-dc转换器的应用。此外,根据该替选实施方式,外部电容器cext的电容可以显著大于内部电容器cp的电容,例如,在6倍至12倍之间大的电容。

72.在至少一些实施方式中,反激式转换器系统800包括耦接至sr晶体管(例如,sr_fet 126)的源极的输出电容器120。在这些实施方式中,输出电容器120提供与通用串行总线c型标准(usb-c)兼容的直流(dc)输出。

73.除了已经提及的提高的效率之外,次级侧控制器802和反激式转换器系统800的优点还包括高达例如5mhz至10mhz的高频操作,可以在距实际峰值50mv内检测到峰值,从而引起在初级侧106上的谷值检测的准确性。此外,峰值可以在实际峰值事件之前被检测到,并且可以补偿峰值感测延迟和路径延迟,这将在本文中详细讨论。优点还可以包括采用使用可编程延迟利用先前的峰值精确地达到第n个峰值的技术。在实施方式中,反激式转换器系统800与仅使用利用峰值到峰值延迟的数字峰值相比,不会在多个峰值上累积误差。此外,高频谷值可以被准确地检测到,以例如在零感测电压检测中使用。附加地,本实施方式不采用采样和保持电路,而是通过采用晶体管和可编程电流源来使用更高效的电流比较和触

发。最终,当前的实施方式采用低功率和低面积解决方案,使材料清单(bom)的增加最小化。

74.图9是根据至少一个实施方式的对反激式转换器100的次级侧控制器进行操作的方法900的流程图。在这些实施方式中,方法900由采用参照图6示出和讨论的次级侧控制器602的反激式转换器100执行,尽管通常也可适用于次级侧控制器802(图8),如下面所说明的。

75.在操作910处,方法900包括使电容器cp响应于在sr感测引脚处感测的电压来进行充电或放电(或者在使用外部电容器cext的情况下,使电容器通过sr_drain节点126a进行充电/放电)。

76.在操作920处,方法900还包括由第一可变电流源606向第一电流镜604的输入提供参考电流,其中,第一可变电流源被编程为生成参考电流,使得峰值检测晶体管n2在sr感测引脚128处感测的电压的实际峰值处或在sr感测引脚128处感测的电压的实际峰值前触发输出。

77.在操作930处,方法900还包括由峰值检测晶体管n2检测来自电容器的电流下降低于参考电流。

78.在操作940处,方法900还包括由峰值检测晶体管n2响应于所述检测输出峰值检测信号(peak__detect)。

79.本文中描述的ac-dc反激式转换器的各种实施方式可以包括各种操作。这些操作可以由硬件部件、数字硬件和/或固件以及/或者其组合来执行和/或控制。如本文所使用的,术语“耦接至”可以意指直接连接或通过一个或更多个中间部件间接连接。通过各种片上总线提供的任何信号可以与其他信号进行时分复用并且可以通过一个或更多个公共的片上总线提供。附加地,电路部件或块之间的互连可以被示出为总线或单个信号线。所述总线中的每一个可以替选地是一个或更多个单个信号线,并且所述单个信号线中的每一个可以替选地是总线。

80.某些实施方式可以通过在非暂态计算机可读介质(例如,诸如易失性存储器和/或非易失性存储器)上存储的固件指令来实现。这些指令可以用于对包括处理器(例如,cpu)或其等同物(例如,诸如处理核、处理引擎、微控制器等)的一个或更多个设备进行编程和/或配置,使得在由处理器或其等同物执行这些指令时,这些指令使所述设备执行针对本文所描述的usb-c模式-转变架构所描述的操作。非暂态计算机可读存储介质可以包括但不限于电磁存储介质、只读存储器(rom)、随机存取存储器(ram)、可擦除可编程存储器(例如,eprom和eeprom)、闪存存储器或者另一种现在已知或后来开发的适于存储信息的非暂态类型的介质。

81.尽管以特定次序示出并描述了本文中的电路和块的操作,但是在一些实施方式中,每个电路/块的操作的次序可以改变使得可以以相反的次序执行某些操作,或者使得可以至少部分地与其他操作同时和/或并行地执行某些操作。在其他实施方式中,可以以间歇和/或交替的方式执行不同操作的指令或子操作。

82.在前述说明书中,已经参照本发明的具体示例性实施方式描述了本发明。然而,将明显的是,在不脱离如所附权利要求中阐述的本发明的更宽泛的精神和范围的情况下,可以对发明进行各种修改和改变。因此,说明书和附图应被认为是说明性的而不是限制性的。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。