1.本发明涉及集成电路技术领域,特别涉及一种半导体器件结构及其制备方法。

背景技术:

2.随着技术节点的发展,gaa(gate all around,环绕式栅极)结构开始计划用于mos晶体管。在gaa结构的hk-mg(高k金属栅极)的阈值电压(vt)调整中,需要将部分区域的功函数层刻蚀干净。由于器件单元中相邻的纳米层(包括纳米片/纳米线)之间较为接近,刻蚀之后可能在纳米层之间的间隔中残留功函数层,从而使gaa结构的阈值电压无法达到所需的目标值或者波动过大;若刻蚀加强则可能损坏其他结构层。

3.因此,有必要提供一种半导体器件结构的制备方法,以解决纳米层之间的间隔中功函数层残留的问题。

技术实现要素:

4.本发明的目的在于提供一种半导体器件结构及其制备方法,以解决纳米层之间的间隔中功函数层残留的问题。

5.为了实现上述目的以及其他相关目的,本发明提供了一种半导体器件结构的制备方法,包括以下步骤:

6.提供晶体管基底以及设于所述晶体管基底上的器件单元,所述器件单元包括nmos器件单元和pmos器件单元,所述nmos器件单元位于所述晶体管基底的nmos区域,所述pmos器件单元位于所述晶体管基底的pmos区域,所述nmos器件单元和pmos器件单元分别包括多个相互间隔的纳米层;

7.依次形成牺牲层和第一光刻胶层于所述器件单元上,所述牺牲层还填充部分所述纳米层之间的间隔;

8.去除所述pmos区域的第一光刻胶层和牺牲层,以裸露出所述pmos器件单元;

9.去除所述nmos区域的第一光刻胶层,以裸露出所述nmos区域的牺牲层;

10.依次形成功函数层和第二光刻胶层于所述nmos区域的牺牲层上和所述pmos器件单元上,所述功函数层还填充所述pmos器件单元中的所述纳米层之间的间隔;

11.去除所述nmos区域的第二光刻胶层、功函数层以及牺牲层。

12.可选的,在所述的半导体器件结构的制备方法中,所述牺牲层的材质包括si或者lao

x

。

13.可选的,在所述的半导体器件结构的制备方法中,在所述牺牲层的材质为si时,形成所述牺牲层的工艺包括pecvd或者pvd;在所述牺牲层的材质为lao

x

时,形成所述牺牲层的工艺包括ald。

14.可选的,在所述的半导体器件结构的制备方法中,所述去除所述pmos区域的第一光刻胶层和牺牲层,以裸露出所述pmos器件单元的步骤包括:

15.对所述第一光刻胶层进行曝光和显影,形成图形化的第一光刻胶层,所述图形化

的第一光刻胶层裸露出所述pmos区域的牺牲层;

16.以所述图形化的第一光刻胶层为掩膜,刻蚀去除所述pmos区域的牺牲层。

17.可选的,在所述的半导体器件结构的制备方法中,所述nmos区域的第一光刻胶层的去除工艺包括:灰化工艺。

18.可选的,在所述的半导体器件结构的制备方法中,所述去除所述nmos区域的第二光刻胶层、功函数层以及牺牲层的步骤包括:

19.对所述第二光刻胶层进行曝光和显影,形成图形化的第二光刻胶层,所述图形化的第二光刻胶层裸露出所述nmos区域的功函数层;

20.以所述图形化的第二光刻胶层为掩膜,依次刻蚀去除所述nmos区域的功函数层以及牺牲层。

21.可选的,在所述的半导体器件结构的制备方法中,所述nmos区域和pmos区域的牺牲层的去除工艺包括湿法刻蚀工艺,在所述牺牲层的材质为si时,所述湿法刻蚀工艺的腐蚀剂包括nh4oh溶液;在所述牺牲层的材质为lao

x

时,所述湿法刻蚀工艺的腐蚀剂包括hcl溶液。

22.可选的,在所述的半导体器件结构的制备方法中,所述nmos区域的功函数层的去除工艺包括湿法刻蚀工艺,且腐蚀剂包括h2o2溶液。

23.可选的,在所述的半导体器件结构的制备方法中,所述纳米层包括:器件单元中基底、依次包覆所述器件单元中基底的界面层、hk电介质层、阻挡层以及刻蚀停止层。

24.为了实现上述目的以及其他相关目的,本发明还提供了一种半导体器件结构,采用上述所述的半导体器件结构的制备方法制备得到。

25.与现有技术相比,本发明的技术方案具有以下有益效果:

26.本发明提供的半导体器件结构的制备方法在nmos区域形成功函数层之前形成了牺牲层,由于牺牲层会部分填充所述纳米层之间的间隔,封闭住所述纳米层之间的间隔(或者通道),使得所述功函数层并不会填充到所述纳米层之间的间隔中,而且所述牺牲层在所述纳米层之间的填充也比较少,在后续很容易清除干净,因此,最终制得的半导体器件结构的纳米层之间并不存在功函数层,也不存在牺牲层,能够解决传统工艺中纳米层之间的间隔中功函数层残留的问题。

附图说明

27.图1是一种半导体器件结构的结构示意图;

28.图2是本发明一实施例的半导体器件结构的制备方法的流程图;

29.图3至图15是本发明一实施例的半导体器件结构的制备方法的各步骤的结构示意图;

30.图1中,

31.01-晶体管基底,02-纳米层,0201-器件单元中基底,0202-hk电介质层,0203-阻挡层,0204-刻蚀停止层,03-功函数层,0301-残留的功函数层;

32.图2~图15中,

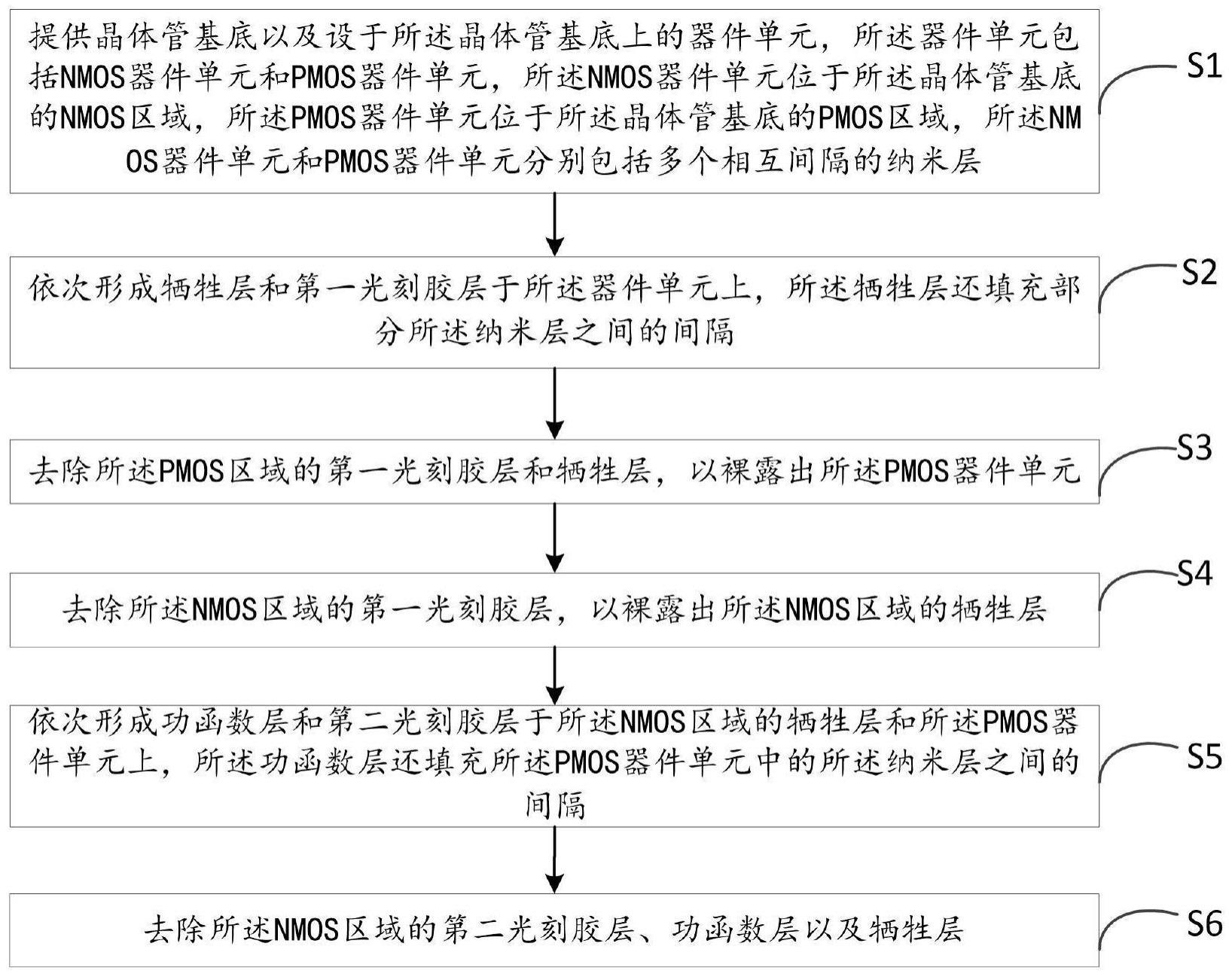

33.10-晶体管基底,20-纳米层,201-器件单元中基底,202-hk电介质层,203-阻挡层,204-刻蚀停止层,30-功函数层,40-牺牲层,501-第一光刻胶层,502-第二光刻胶层。

具体实施方式

34.以下结合附图和具体实施例对本发明提出的半导体器件结构及其制备方法作进一步详细说明。根据下面说明书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

35.参阅图1,一种半导体器件结构的制备方法具体包括以下步骤:

36.步骤s01:提供晶体管基底01以及设于所述晶体管基底01上的器件单元,所述器件单元包括nmos器件单元和pmos器件单元,所述nmos器件单元位于所述晶体管基底01的nmos区域,所述pmos器件单元位于所述晶体管基底01的pmos区域,所述nmos器件单元和pmos器件单元分别包括多个相互间隔纳米层02;

37.步骤s02:依次形成功函数层03和光刻胶层(图中未示出)于所述器件单元上,所述功函数层03还填充所述纳米层02之间的间隔;

38.步骤s03:去除所述nmos区域的光刻胶层和功函数层03,以裸露出所述nmos器件单元;

39.步骤s04:去除所述pmos区域的光刻胶层。

40.所述晶体管基底01包括nmos区域和与所述nmos区域相邻的pmos区域,且所述晶体管基底01上形成有器件单元,所述器件单元包括位于nmos区域的nmos器件单元和位于所述pmos区域的pmos器件单元。所述nmos器件单元和pmos器件单元分别包括多个相互间隔纳米层02。所述纳米层02包括:器件单元中基底0201、依次包覆所述器件单元中基底0201的界面层(il,图中未示出)、hk(高k)电介质层0202、阻挡层0203以及刻蚀停止层0204。

41.由所述半导体器件结构最终可以制得gaa结构,而在gaa结构的高k金属栅极的阈值电压调整中,需要将所述半导体器件结构中的部分区域的功函数层刻蚀干净,但是,由于器件单元的各区域中的相邻的纳米层02之间较为接近,刻蚀功函数层之后容易在层间残留一些功函数层,即纳米层02之间会有残留的功函数层0301,造成gaa结构的阈值电压无法达到所需的目标值或波动过大。若加强功函数层的刻蚀则可能损坏其他结构层,例如损坏阻挡层0203、刻蚀停止层0204等结构层。

42.为了解决gaa结构平台的功函数层残留的问题,即解决纳米层之间的间隔中功函数层残留的问题,本发明提供了一种半导体器件结构的制备方法,参见图2。

43.所述半导体器件结构的制备方法包括以下步骤:

44.步骤s1:提供晶体管基底以及设于所述晶体管基底上的器件单元,所述器件单元包括nmos器件单元和pmos器件单元,所述nmos器件单元位于所述晶体管基底的nmos区域,所述pmos器件单元位于所述晶体管基底的pmos区域,所述nmos器件单元和pmos器件单元分别包括多个相互间隔的纳米层;

45.步骤s2:依次形成牺牲层和第一光刻胶层于所述器件单元上,所述牺牲层还填充部分所述纳米层之间的间隔;

46.步骤s3:去除所述pmos区域的第一光刻胶层和牺牲层,以裸露出所述pmos器件单元;

47.步骤s4:去除所述nmos区域的第一光刻胶层,以裸露出所述nmos区域的牺牲层;

48.步骤s5:依次形成功函数层和第二光刻胶层于所述nmos区域的牺牲层和所述pmos

器件单元上,所述功函数层还填充所述pmos器件单元中的所述纳米层之间的间隔;

49.步骤s6:去除所述nmos区域的第二光刻胶层、功函数层以及牺牲层。

50.参阅图3和图4,其中图4是图3中的器件单元的局部放大图。在步骤s1中,所述晶体管基底10可以是硅或基于硅的其他材质,也可以为其他材料,例如,该晶体管基底10可以为硅基底或者硅锗基底等。同时,所述晶体管基底10可以是掺杂的,也可以是不掺杂的。所述晶体管基底10包括nmos区域和与所述nmos区域相邻的pmos区域,且所述晶体管基底10上形成有器件单元,所述器件单元包括位于nmos区域的nmos器件单元和位于所述pmos区域的pmos器件单元。

51.所述nmos器件单元和pmos器件单元分别包括多个相互间隔纳米层20。所述纳米层20可以为纳米线,也可以为纳米片,还可以为其他形状。同一个区域中,多层所述纳米层20的厚度可以相同,也可以不同,相邻的所述纳米层20之间的间隔可以相同也可以不同。例如,nmos区域中的各所述纳米层20的厚度相同,且相邻的所述纳米层20之间的间隔相同。所述纳米层20包括:器件单元中基底201、依次包覆所述器件单元中基底201的界面层(图中未示出)、hk电介质层202、阻挡层203以及刻蚀停止层204。

52.所述器件单元中基底201可以是硅或基于硅的其他材质,也可以为其他材料。包覆所述器件单元中基底201的界面层(il)材质可以包括诸如氮化硅之类的材质,或其他合适的材质,例如氮氧化硅。包覆所述界面层的hk电介质层202的材质为高k材质,本实施例中使用的高k材质的示例可包括氧化钽(ta2o5)、氧化锶钛(srtio3)、氧化铪(hfo2)、氧化铪硅(hfsio)、氧化锆(zro2)等,优选为氧化铪。包覆所述hk电介质层202的阻挡层203。所述阻挡层203的材质优选为tin,但不限于此。包覆所述阻挡层203的刻蚀停止层204,用于后续湿法去除所述功函数层的停止层,以防湿法工艺对阻挡层203造成损伤。所述刻蚀停止层204的材质优选为tan,但不限于此。

53.参阅图5,在步骤s2中,形成所述牺牲层40于所述nmos器件单元和pmos器件单元表面上,且所述牺牲层40的厚度优选为例如,所述牺牲层40的厚度为所述牺牲层40的材质优选为si或者lao

x

,但不限于此。在所述牺牲层的材质为si时,形成所述牺牲层40的工艺优选为pecvd(plasma enhanced chemical vapor deposition,等离子体增强化学的气相沉积)或者pvd(physical vapor deposition,物理气相沉积),但不限于此。在所述牺牲层的材质为lao

x

时,形成所述牺牲层的工艺优选为ald(atomic layer deposition,原子层沉积),但不限于此。在ald工艺中,la的前驱体与h2o生长的lao

x

。

54.由于采用pecvd或者pvd形成的si,以及采用ald工艺形成的lao

x

的填充能力均比较差,因此,所述牺牲层40可在封闭gaa栅极间通道(即纳米层间的间隔)的同时较少填充通道,即所述牺牲层40可部分填充所述纳米层20之间的间隔,且可以防止后续形成的光刻胶层和功函数层填充到所述纳米层20之间的间隔中。由于所述牺牲层40的填充能力比较差,其只是较少的填充所述纳米层20之间的间隔,因此后续更容易将所述牺牲层40清除干净。

55.参阅图6,在所述牺牲层40上旋涂光刻胶,形成所述第一光刻胶层501。所述第一光刻胶层501的上表面齐平。在所述第一光刻胶层501与所述牺牲层40之间还可以形成第一底部抗反射层。所述第一底部抗反射层的反射率低。所述第一底部抗反射层的材料可以是有机抗反射涂层(organic),采用旋涂的方式涂布形成;所述第一底部抗反射层的材料也可以是无机抗反射涂层(inorganic),利用等离子增强化学气相沉积(pecvd)形成,所述无机抗

反射涂层的材料为氮化钛或氮化硅,但不限于此。在本实施例中,所述第一底部抗反射层优选为有机抗反射涂层。

56.参阅图7和图8,在步骤s3中,所述去除所述pmos区域的第一光刻胶层和牺牲层,以裸露出所述pmos器件单元的步骤包括:

57.步骤s31:对所述第一光刻胶层501进行曝光和显影,形成图形化的第一光刻胶层,所述图形化的第一光刻胶层裸露出所述pmos区域的牺牲层40;

58.步骤s32:以所述图形化的第一光刻胶层为掩膜,刻蚀去除所述pmos区域的牺牲层40。

59.参阅图7,在步骤s31中,所述图形化的第一光刻胶层裸露出所述pmos区域的牺牲层40,即曝光和显影掉所述pmos区域的光刻胶,而所述nmos区域的光刻胶被保留下来。

60.在所述第一光刻胶层与所述牺牲层40之间存在第一底部抗反射层时,在步骤s31和步骤s32之间还包括:对所述第一底部抗反射层进行刻蚀。所述第一底部抗反射层优选为有机抗反射涂层,所述有机抗反射涂层的刻蚀优选为干法刻蚀,所述刻蚀气体优选为ch2f2或c4h8,但不限于此。

61.参阅图8,在步骤s32中,以所述图形化的第一光刻胶层为掩膜对所述牺牲层40进行刻蚀。由于所述pmos区域的光刻胶被刻蚀掉,因此以所述图形化的第一光刻胶层为掩膜,刻蚀掉所述pmos区域的牺牲层40。

62.所述牺牲层40的刻蚀工艺优选为湿法刻蚀工艺。在所述牺牲层40的材质为si时,所述湿法刻蚀工艺的腐蚀剂包括nh4oh溶液,但不限于此;在所述牺牲层的材质为lao

x

时,所述湿法刻蚀工艺的腐蚀剂包括hcl溶液,但不限于此。由于所述牺牲层40的填充能力比较差,其只是较少的填充所述纳米层20之间的间隔,因此湿法刻蚀工艺很容易将所述牺牲层40清除干净,并不会残留在所述纳米层20之间的间隔中。

63.参阅图9,在步骤s4中,去除所述nmos区域的第一光刻胶层501,即去除图形化的所述第一光刻胶层。所述nmos区域的第一光刻胶层的去除方法优选为灰化的方法。

64.参阅图10,在步骤s5中,形成功函数层30于所述nmos区域的牺牲层40和所述pmos器件单元上,所述功函数层30还填充所述pmos器件单元中的所述纳米层20之间的间隔。所述功函数层30的材质优选为tin,但不限于此。所述功函数层30的厚度优选为且所述功函数层30的形成工艺可以为pvd、cvd以及ald中的任意一种。由于所述pmos区域的第一光刻胶层501和牺牲层40均被刻蚀掉,会裸露出所述pmos器件单元,即pmos器件单元中的纳米层20以及纳米层20之间的间隔均被裸露出来,因此,所述功函数层30还填充所述纳米层20之间的间隔,且填满所述纳米层20之间的间隔。

65.参阅图11,在所述功函数层30上旋涂光刻胶,形成第二光刻胶层502。在所述第二光刻胶层502与所述功函数层30之间还可以形成第二底部抗反射层。所述第二底部抗反射层的反射率低。所述第二底部抗反射层的材料可以是有机抗反射涂层(organic),采用旋涂的方式涂布形成;所述第二底部抗反射层的材料也可以是无机抗反射涂层(inorganic),利用等离子增强化学气相沉积(pecvd)形成,所述无机抗反射涂层的材料为氮化钛或氮化硅,但不限于此。在本实施例中,所述第二底部抗反射层优选为有机抗反射涂层。

66.参阅图12~图14,在步骤s6中,所述去除所述nmos区域的第二光刻胶层502、功函数层30以及牺牲层40的步骤包括。

67.步骤s61:对所述第二光刻胶层502进行曝光和显影,形成图形化的第二光刻胶层,所述图形化的第二光刻胶层裸露出所述nmos区域的功函数层30;

68.步骤s62:以所述图形化的第二光刻胶层为掩膜,依次刻蚀去除所述nmos区域的功函数层30以及牺牲层40。

69.参阅图12,在步骤s61中,所述图形化的第二光刻胶层裸露出所述nmos区域的功函数层30,即曝光和显影掉所述nmos区域的光刻胶,而所述pmos区域的光刻胶被保留下来。

70.在所述第二光刻胶层与所述功函数层30之间存在第二底部抗反射层时,在步骤s61和步骤s62之间还包括:对所述第二底部抗反射层进行刻蚀。所述第二底部抗反射层优选为有机抗反射涂层,所述有机抗反射涂层的刻蚀优选为干法刻蚀,所述刻蚀气体优选为ch2f2或c4h8,但不限于此。

71.参阅图13,在步骤s62中,以所述图形化的第二光刻胶层为掩膜,刻蚀去除所述nmos区域的功函数层30,即图形化所述功函数层。所述功函数层30的去除方法优选为湿法刻蚀工艺,所述腐蚀剂优选为sc2或者h2o2,但不限于此。

72.参阅图14,以所述图形化的第二光刻胶层和图形化的功函数层为掩膜,刻蚀去除所述nmos区域的牺牲层40。在所述牺牲层40的材质为si时,所述湿法刻蚀工艺的腐蚀剂包括nh4oh溶液,但不限于此;在所述牺牲层的材质为lao

x

时,所述湿法刻蚀工艺的腐蚀剂包括hcl溶液,但不限于此。由于所述牺牲层40的填充能力比较差,其只是较少的填充所述纳米层20之间的间隔,因此湿法刻蚀工艺很容易将所述牺牲层40清除干净,并不会残留在所述纳米层20之间的间隔中。即nmos区域的纳米层20之间的间隔中并不存在牺牲层的残留。

73.参阅图15,在去除所述nmos区域的第二光刻胶层、功函数层以及牺牲层的步骤之后,还可以包括:去除所述pmos区域的第二光刻胶层502,以裸露出所述pmos区域的功函数层30。所述pmos区域的第二光刻胶层502的去除方法优选为灰化。

74.综上可见,在半导体器件的制备方法中,本发明在形成nmos区域的功函数层之前形成了牺牲层,由于牺牲层的填充能力差,可在封闭纳米层之间的间隔(即通道)的同时较少填充所述间隔,可以防止nmos区域的功函数层填充到纳米层之间的间隔中,因此所述nmos区域的纳米层之间的间隔中不存在功函数的残留,可以防止器件电性难以达标或波动过大。

75.本发明还提供了同一种由上述所述的半导体器件的制备方法制备的半导体器件结构。所述半导体器件结构的nmos区域的纳米层之间的间隔中没有功函数层残留,可以避免半导体器件阈值电压无法达到所需的目标值或波动过大的问题。

76.在制备的所述半导体器件上沉积金属层可以制备gaa结构,所述金属层覆盖在整个半导体器件上,且所述金属层还填充所述nmos区域的纳米层之间的间隔,即所述金属层还填充所述nmos区域的纳米层之间的间隔。所述金属层至少包括tial层、tin层以及钨金属层。gaa结构的制备方法可以改善传统功函数层去除技术在gaa平台存在的功函数层残留,提高所述gaa结构的电学性能。

77.此外,可以理解的是,虽然本发明已以较佳实施例披露如上,然而上述实施例并非用以限定本发明。对于任何熟悉本领域的技术人员而言,在不脱离本发明技术方案范围情况下,都可利用上述揭示的技术内容对本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术

实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

78.而且还应该理解的是,本发明并不限于此处描述的特定的方法、化合物、材料、制造技术、用法和应用,它们可以变化。还应该理解的是,此处描述的术语仅仅用来描述特定实施例,而不是用来限制本发明的范围。必须注意的是,此处的以及所附权利要求中使用的单数形式“一个”、“一种”以及“该”包括复数基准,除非上下文明确表示相反意思。因此,例如,对“一个步骤”引述意味着对一个或多个步骤的引述,并且可能包括次级步骤。应该以最广义的含义来理解使用的所有连词。因此,词语“或”应该被理解为具有逻辑“或”的定义,而不是逻辑“异或”的定义,除非上下文明确表示相反意思。此处描述的结构将被理解为还引述该结构的功能等效物。可被解释为近似的语言应该被那样理解,除非上下文明确表示相反意思。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。