采用电容性存储电路的内存中计算(cim)单元电路和cim位单元阵列电路

1.相关申请的交叉引用

2.本技术要求于2020年10月9日提交的题为“compute-in-memory(cim)cell circuits employing capacitive storage circuits for reduced area and cim bit cell array circuits”的美国专利申请序列号17/067,205的优先权,该申请通过引用整体并入本文。

技术领域

3.本公开的领域总体上涉及用于高速并行数据处理(诸如神经网络)的电路中的内存中计算(cim)阵列。

背景技术:

4.机器学习是人工智能(ai)的一个示例。在初始学习阶段,配置有机器学习的计算机接收一组已知输入数据,并且执行对输入数据的评估。对输入数据的评估可以包括数千次计算,其中基于存储在计算机存储器中的权重数据对个体输入进行加权。评估的正确性的指示作为反馈被提供,并且计算机响应于该反馈而修改所存储的权重数据。计算机使用修改后的权重数据来评估新数据。随着接收到的反馈越多,评估结果就越准确。

5.在常规计算机中,每次计算都需要从存储器中传输输入数据和权重数据,并且然后生成传输到存储器的输出数据。当计算机试图并行执行很多计算时,处理电路与存储器之间的数据传输瓶颈会导致处理电路缺少数据,这会延长执行时间并且增加功耗。

6.在替代方法中,计算机中的专用处理电路可以并行执行很多乘法和累加运算。这些运算可以通过由节点阵列组成的神经网络框架有效地实现,该节点以类似于大脑突触的结构被组织。这些处理节点每个执行乘法累加(mac)运算,其中每个输入乘以对应权重数据并且所得的的乘积被求和。图1是被配置为执行mac运算的神经网络的节点100的图示。节点100接收一组输入x

0-xm,每个输入乘以权重值w

0-wm中的对应一个。权重值w

0-wm基于来自先前计算的反馈,并且随着时间的推移,提高关于特定类型输入数据的计算精度。乘法的乘积是相应乘积p

0-pm。乘积p

0-pm相加以生成总和sum,并且节点100生成作为总和sum的函数af(例如,激活函数)的输出out。

7.内存中计算(cim)阵列被开发以实现神经网络框架的节点,该框架对一位二进制数执行mac运算,并且减少数据传输瓶颈,从而更快地生成结果。cim阵列将二进制权重数据的位存储在cim阵列的位单元内,并且还执行权重数据和输入数据的乘法运算。一位二进制值的乘法可以实现为基于逻辑and的运算(例如,and或not and(nand))。每个cim位单元包括用于存储权重数据位并且执行乘法的电路。当处理电路中采用包括cim阵列的神经网络以减少数据瓶颈时,处理速度的增加以cim位单元电路所占用的集成电路(ic)的面积的增加为代价。

技术实现要素:

8.本文中公开的方面包括采用电容性存储电路以减小面积的内存中计算(cim)位单元电路。还公开了采用cim位单元电路的cim位单元阵列电路和操作这种cim位单元阵列电路的方法。与在常规处理器中执行mac运算的每个个体计算相比,采用cim位单元阵列电路在神经网络中并行执行多个乘法累加(mac)运算减少了执行时间,但是cim位单元阵列电路所占用的面积增加了集成电路(ic)的尺寸。六晶体管(6t)静态随机存取存储器(sram)位单元电路先前已经用于cim位单元电路中。在示例性方面,一种采用电容性存储电路来存储二进制权重数据作为电压的cim位单元电路占用6tsram cim位单元电路的面积的一半或更少,从而减少了将cim位单元阵列电路添加到ic中所引起的面积增加。电容性存储电路被配置为将二进制权重数据存储在电容器中,并且生成乘积电压,该乘积电压指示由所存储的二进制权重数据和激活信号的基于逻辑and的运算产生的二进制乘积。cim位单元电路包括被配置为将写入位电压耦合到电容性存储电路的写入访问开关。电容性存储电路被配置为基于写入位电压将二进制权重数据存储为电荷,并且基于所存储的二进制权重数据和激活信号在读取位输出上生成乘积电压。在示例中,电容性存储电路可以包括电容器和读取访问开关或晶体管。

9.在这点上,在一个方面,公开了一种cim位单元电路。cim位单元电路包括写入访问开关。写入访问开关包括耦合到写入位输入的输入端子。写入访问开关还包括耦合到写入字输入的控制端子。写入访问开关还包括输出端子。写入访问开关被配置为响应于提供给写入字输入的写入字电压而将写入位输入耦合到输出端子。cim位单元电路还包括电容性存储电路。电容性存储电路包括耦合到写入访问开关的输出端子的第一端口。电容性存储电路还包括耦合到读取位输出的第二端口。电容性存储电路被配置为存储权重数据,权重数据基于响应于提供给写入字输入的写入字电压而在写入位输入上提供的写入位电压。电容性存储电路还被配置为基于激活信号和所存储的权重数据在读取位输出上生成乘积电压。

10.在另一方面,公开了一种cim位单元阵列电路。cim位单元阵列电路包括cim位单元电路阵列。cim位单元电路阵列还包括多行cim位单元电路和多列cim位单元电路。多行中的每一行包括对应激活线和对应写入字线,对应激活线耦合到行中的cim位单元电路中的每个cim位单元电路中的激活输入,对应写入字线耦合到行中的cim位单元电路中的每个cim位单元电路中的写入字输入。多列中的每一列包括对应写入位线和对应读取位线,对应写入位线耦合到列中的cim位单元电路中的每个cim位单元电路中的写入位输入,对应读取位线耦合到列中的cim位单元电路中的每个cim位单元电路中的读取位输出。每个cim位单元电路包括写入访问开关。写入访问开关包括耦合到写入位输入的输入端子。写入访问开关还包括耦合到写入字输入的控制端子。写入访问开关还包括输出端子。每个cim位单元电路还包括电容性存储电路。电容性存储电路包括耦合到写入访问开关的输出端子的第一端口。电容性存储电路还包括第二端口。电容性存储电路被配置为存储权重数据,权重数据基于响应于提供给写入字线的写入字电压而在写入位线上提供的写入位电压。电容性存储电路还被配置为基于激活线上的激活信号和所存储的权重数据在读取位输出上生成乘积电压。

附图说明

11.图1是神经网络中用于执行乘法累加(mac)运算的处理节点的示意图;

12.图2a是示例性三晶体管(3t)内存中计算(cim)位单元电路的示意图,该cim位单元电路包括电容性存储电路中的n型金属氧化物半导体(mos)(nmos)场效应晶体管(mosfet)和nmos读取访问晶体管,并且生成输入数据位和存储在电容性存储电路中的权重数据位的逻辑乘积(基于and的运算);

13.图2b是示出图2a中的3t cim位单元电路中的所存储的二进制权重数据和激活信号的逻辑乘法(基于and)运算的真值表;

14.图3是示例性3t cim位单元电路的示意图,该3t cim位单元电路包括电容性存储电路中的p型mos(pmos)fet(mosfet)和pmos读取访问晶体管电路;

15.图4是示例性双晶体管(2t)单电容器(1c)(2t1c)cim位单元电路的示意图,该2t1c cim位单元电路包括电容性存储电路中的平行板电容器和nmos读取访问晶体管;

16.图5是示例性2t1c cim位单元电路的示意图,该2t1c cim位单元电路包括电容性存储电路中的平行板电容器和pmos读取访问晶体管;

17.图6是图2中的多个3t cim位单元电路的2

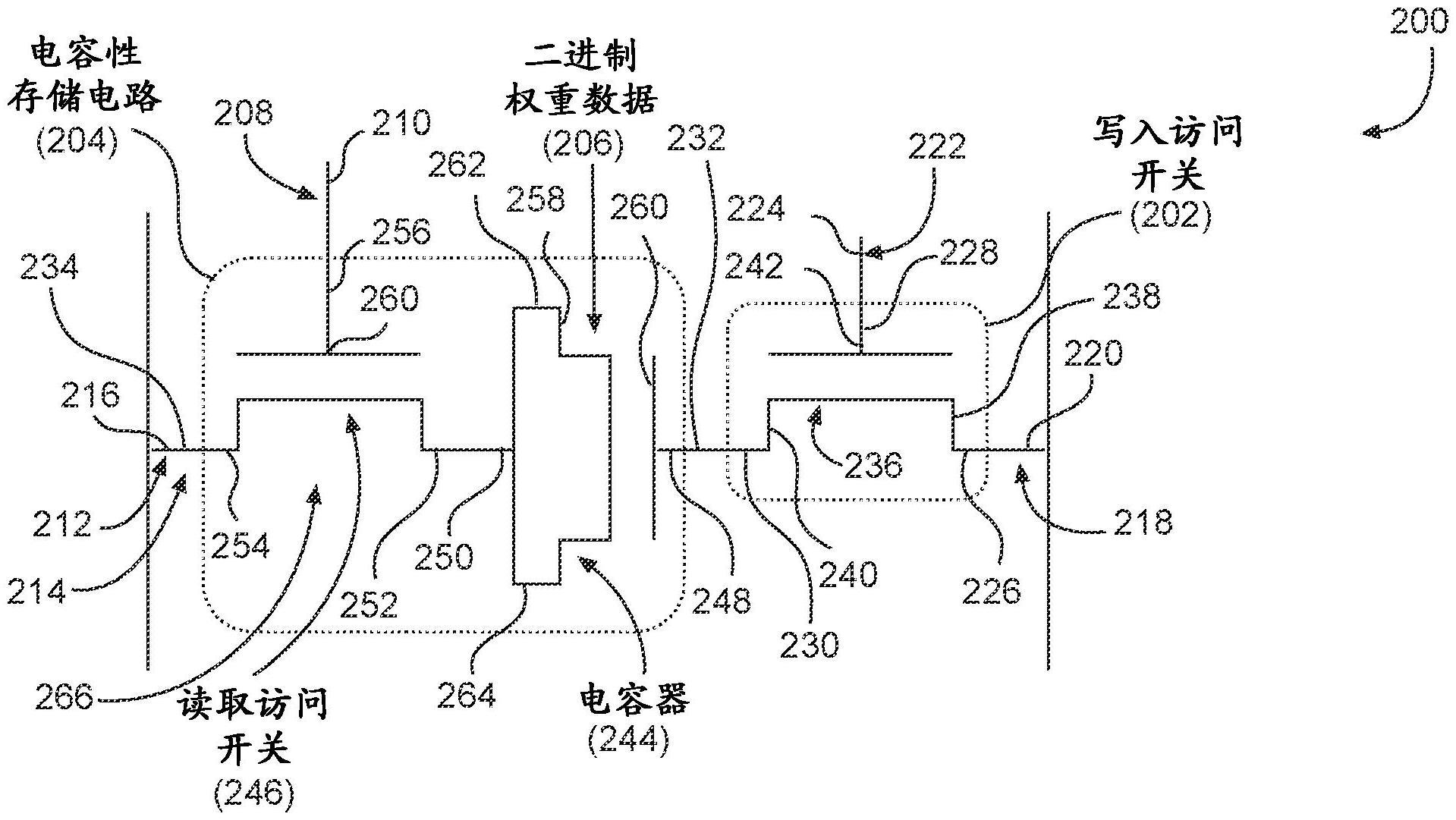

×

2阵列的示意图,并且在2

×

2阵列的每一列中包括求和电路;

18.图7a是基于动态随机存取存储器(dram)位电路的示例性2tcim位单元电路的示意图,该2t cim位单元电路包括电容性存储电路中的p型mosfet和pmos读取访问晶体管;

19.图7b是示出图7a的2t cim位单元电路的操作的真值表;

20.图8a是示例性2t cim位单元电路的示意图,该2t cim位单元电路包括电容性存储电路中的n型mosfet和nmos读取访问晶体管;

21.图8b是示出图8a的2t cim位单元电路的操作的真值表;

22.图9是图8中的多个2t cim位单元电路的2

×

2阵列的示意图,该2t cim位单元电路在2

×

2阵列的每一列中包括求和电路;

23.图10是其中集成有如图6和图9所示的cim位单元阵列电路的集成电路的框图;以及

24.图11是示例性的基于处理器的系统的框图,该系统包括根据本文中公开的任何方面的图2-图5和图7-图8中的cim位单元电路的cim位单元阵列电路,cim位单元电路每个包括电容性存储电路并且被配置为存储权重数据并且生成输入数据位和所存储的权重数据的逻辑乘积(基于and的运算),如图6和图9中的任何一个中所示。

具体实施方式

25.现在参考附图,描述了本公开的若干示例性方面。本文中使用“示例性”一词是指“用作示例、实例或说明”。本文中描述为“示例性的”的任何方面不一定被解释为优选于或优于其他方面。

26.本文中公开的方面包括采用电容性存储电路以减小面积的内存中计算(cim)位单元电路。还公开了采用cim位单元电路的cim位单元阵列电路和操作这种cim位单元阵列电路的方法。与在常规处理器中执行mac运算的每个个体计算相比,采用cim位单元阵列电路在神经网络中并行执行多个乘法累加(mac)运算减少了执行时间,但是cim位单元阵列电路

所占用的面积增加了集成电路(ic)的尺寸。六晶体管(6t)静态随机存取存储器(sram)位单元电路先前已经用于cim位单元电路中。在示例性方面,一种采用电容性存储电路来存储二进制权重数据作为电压的cim位单元电路占用6tsram cim位单元电路的面积的一半或更少,从而减少了将cim位单元阵列电路添加到ic中所引起的面积增加。电容性存储电路被配置为将二进制权重数据存储在电容器中,并且生成乘积电压,该乘积电压指示由所存储的二进制权重数据和激活信号的基于逻辑and的运算产生的二进制乘积。cim位单元电路包括被配置为将写入位电压耦合到电容性存储电路的写入访问开关。电容性存储电路被配置为基于写入位电压将二进制权重数据存储为电荷,并且基于所存储的二进制权重数据和激活信号在读取位输出上生成乘积电压。在示例中,电容性存储电路可以包括电容器和读取访问开关或晶体管。

27.图2a是用于mac运算的第一示例性cim位单元电路200的示意图。cim位单元电路200采用电容性的基于电荷的数据存储,并且在基于6t sram的cim位单元的面积的一半或更少中执行二进制乘法。cim位单元电路200包括写入访问开关202,该写入访问开关202被控制为用二进制权重数据206对电容性存储电路204进行编程。cim位单元电路200在激活输入210上接收激活信号208,以控制乘积数据212的生成。乘积数据212是激活信号208和二进制权重数据206的二进制乘法(例如,基于逻辑and的运算)的结果。乘积数据212由在读取位输出216上生成的乘积电压214指示。

28.电容性存储电路204基于写入位电压218将二进制权重数据206存储为电荷。写入位电压218被提供在写入位输入220上,并且响应于在写入字输入224上接收的写入字电压222而通过写入访问开关202提供给电容性存储电路204。在这点上,写入访问开关202包括耦合到写入位输入220的输入端子226、耦合到写入字输入224的控制端子228、以及耦合到电容性存储电路204的第一端口232的输出端子230。输入端子226电耦合到输出端子230,以响应于在控制端子228上提供的写入字电压222而将写入位电压218提供给电容性存储电路204的第一端口232。

29.在一个示例中,写入位电压218可以是指示二进制权重数据206为二进制“1”的电源电压v

dd

,或者可以是指示二进制权重数据206为二进制“0”的接地电压v

ss

。替代地,接地电压v

ss

可以指示二进制“1”,并且电源电压v

dd

可以指示二进制值“0”。激活输入210上的激活信号208的二进制值可以以与二进制权重数据206相同的方式来指示。cim位单元电路200生成乘积电压214,以指示二进制权重数据206和激活信号208的逻辑and运算的二进制乘积。电容性存储电路204通过耦合到读取位输出216的第二端口234生成乘积电压214。cim位单元电路200还可以被配置为生成作为逻辑and运算的乘积的乘积电压214。

30.在图2a的示例中,写入访问开关202是n型金属氧化物半导体(mos)场效应晶体管(fet)(n型mosfet)(nfet)236。nfet 236的源极/漏极238是写入访问开关202的输入端子226,并且nfet 236的漏极/源极240是输出端子230。nfet 236的栅极242是控制端子228。在替代示例中,写入访问开关202可以被实现为p型mosfet(pfet)。通常,根据实现,本文中提及的源极/漏极可以用作fet的源极或漏极,并且漏极/源极是指fet的漏极或源极中的另一个。接入开关202还可以实现为双极结晶体管(bjt)、微机电系统(mems)器件或其他开关技术。在这样的替代方案中,写入访问开关202的输入端子226、输出端子230和控制端子228由这样的器件的适当端子实现,并且控制端子228可以由不同信号、电压和/或电流激活,以将

写入位输入220电耦合到电容性存储电路204的第一端口232。

31.电容性存储电路204包括用于存储二进制权重数据206的电容器244和用于生成乘积电压214的读取访问开关246。电容器244包括耦合到第一端口232的第一端子248。电容器244还包括耦合到读取访问开关246的输入端子252的第二端子250。读取访问开关246的输出端子254耦合到电容性存储电路204的第二端口234,并且读取访问开关246的控制端子256耦合到cim位单元电路200的激活输入210。

32.在图2a的示例中,nfet 258被配置为电容器244。nfet 258的栅极260是电容器244的第一端子248。nfet 258的源极/漏极262和漏极/源极264彼此电短路,并且还耦合到电容器244的第二端子250。

33.为了在cim位单元电路200中写入用于mac运算的二进制权重数据206,写入访问开关202由提供给写入字输入224的写入字电压222导通,并且激活的写入访问开关202将提供给写入位输入220的写入位电压218传递给栅极260。在cim位单元电路200中,响应于写入字电压222为电源电压v

dd

,写入访问开关202的nfet 236导通(例如,以在源极/漏极238与漏极/源极240之间传导)。写入位电压218将栅极260充电至指示二进制权重数据206为“0”或“1”的电压电平。栅极260上的电荷在电容器244的第二端子250上被反射。为了从cim位单元电路200中读取乘积数据212,在激活输入210上提供的激活信号208导通读取访问开关246,并且乘积电压214在读取位输出216上被生成。响应于写入字电压222为电源电压v

dd

,读取访问开关246导通(例如,以在源极/漏极238与漏极/源极240之间传导)。在这点上,读取访问开关246可以是nfet 266或其他类型的电开关。在从电容性存储电路204读取乘积数据212之后,表示二进制权重数据206的电荷保留在电容器244上。因此,用于读取乘积数据212的读取操作是非破坏性的。

34.用作电容器244的nfet 258基于写入位电压218被充电,但nfet 258中的漏电流允许电荷随时间缓慢消散。因此,为了保持nfet 258上的电荷以避免丢失写入cim位单元电路200的二进制权重数据206,通过向写入位输入220提供相同写入位电压218并且通过向写入字输入224提供写入字电压222来激活写入访问开关202,可以动态地(例如,周期性地或偶尔地)刷新电容器244上的电荷。

35.此外,读取访问开关246可以被激活,以在电容器244上的电荷被刷新的同时(例如,相同时间)读取读取位输出216上的乘积数据212。在这点上,刷新操作不会与乘积数据212从cim位单元电路200中的读取冲突,这消除了对控制逻辑的需要以及由于冲突而导致的处理延迟的可能性。

36.参考真值表270,图2b示出了,只有当二进制权重数据206和激活信号208都具有二进制值“1”时,乘积数据212才会具有二进制值“1”。否则,乘积数据212将具有二进制值“0”。因此,cim位单元电路200执行所存储的二进制权重数据206和激活信号208的二进制乘法以产生乘积数据212。

37.写入访问开关202也由nfet 266实现。因此,cim位单元电路200仅包括三(3)个晶体管(即,写入访问开关202、电容器244和读取访问开关246),它们在该示例中都是nfet。cim位单元电路200的三个nfet占据先前在cim电路中采用的6t sram位单元电路所占据的面积的大约一半。由于存储在电容器244中的电荷泄漏,电容性的存储的二进制权重数据206需要周期性地刷新,但是基于sram的电路的面积减少50%对于不断试图减少ic面积的

ic设计者来说是可接受的折衷。与采用由6t sram位单元电路形成的神经网络处理电路相比,采用图2a中的多个cim位单元电路200作为神经网络处理电路的ic将导致更小的尺寸增加,这降低了ic成本。

38.此外,cim位单元电路200(其中电气组件为mosfet)可以在无需特殊工艺的情况下制造,该特殊工艺将需要在具有基于mosfet的逻辑电路的ic上采用嵌入式动态随机存取存储器(dram)。因此,提供了面积减小的cim处理电路,而无需附加处理步骤。

39.如上所述,图2a中的写入访问开关202和电容性存储电路204均采用n型mosfet(即,分别为nfet 236和nfet 258)。图3中示出了替代cim位单元电路300的示意图。cim位单元电路300采用电容性的基于电荷的数据存储,并且在基于6t sram的cim位单元的面积的一半或更少中执行二进制乘法。cim位单元电路300包括用于控制电容性存储电路304的编程的写入访问开关302。cim位单元电路300在操作上与图2a的cim位单元电路200相同,除了提供给写入字输入308以导通写入访问开关302的写入字电压306。在cim位单元电路300中,写入访问开关302采用p型mosfet(pfet)310,该pfet 310由作为接地电压v

ss

的写入字电压306激活,这与图2a中提供给写入字输入224的电源电压v

dd

相反。写入访问开关302响应于写入字输入308上的写入字电压306而将写入位输入312耦合到电容性存储电路304的第一端口314。电容性存储电路304的第一端口314耦合到用作电容器320的pfet 318的第一端子316。在电容性存储电路304中,pfet 318的源极/漏极322和漏极/源极324耦合到第一端子316,并且pfet 316的栅极326耦合到第二端子328。电容器320被电气充电以存储基于在写入位输入312上提供的写入位电压332的二进制权重数据330。

40.响应于激活输入340上的激活信号338,电容性存储电路304中的读取访问开关334将电容器320的第二端子328耦合到电容性存储电路304的第二端口336。激活输入340耦合到读取访问开关334的控制端子342。第二端口336进一步耦合到读取位输出344。读取访问开关334是与图2中的nfet 266相对应的nfet 346。在读取位输出344上生成的乘积数据348是二进制权重数据330和激活信号338的逻辑and的二进制结果。

41.在另一示例中,图4中示出了cim位单元电路400的示意图。cim位单元电路400采用电容性的基于电荷的数据存储,并且在基于6t sram的cim位单元的面积的一半或更少中执行二进制乘法。cim位单元电路400包括用于控制电容性存储电路404的编程的写入访问开关402。cim位单元电路400的操作与图2a的cim位单元电路200的操作相同。也就是说,cim位单元电路400存储二进制权重数据406,该二进制权重数据406基于响应于写入字输入414上的写入字电压412的写入位输入410上的写入位电压408。此外,乘积数据416通过二进制权重数据406和激活输入420上的激活信号418的逻辑and运算来生成。

42.cim位单元电路400在结构上等同于cim位单元电路200,除了电容性存储电路404采用电容器422代替图2a中的电容性存储电路204中采用的nfet 258。cim位单元电路400在功能上也等同于cim位单元电路200。电容器422存储二进制权重数据406。写入访问开关402和读取访问开关424可以分别是nfet 426和428,其对应于图2a中的nfet 236和266。电容器422可以是在前端线(feol)工艺或后端线(beol)工艺中形成的平行板电容器或其他类型的电容器。根据本公开的cim位单元电路400可以替代地包括除了平行板电容器422之外的另一电容器结构。

43.在另一示例中,cim位单元电路500的示意图如图5所示。cim位单元电路500也在基

于6t sram的cim位单元的面积的一半或更少中采用电容性的基于电荷的数据存储。cim位单元电路500包括用于控制电容性存储电路504的编程的写入访问开关502。cim位单元电路500的操作与图3的cim位单元电路300的操作相同。也就是说,cim位单元电路500存储二进制权重数据506,该二进制权重数据506基于响应于在写入字输入514上提供的写入字电压512而在写入位输入510上提供的写入位电压508。乘积数据516通过二进制权重数据506和在激活输入520上提供的激活信号518的逻辑and运算来生成。cim位单元电路500在结构上等同于cim位单元电路300,除了电容性存储电路504采用电容器522代替图3中的电容性存储电路304中采用的pfet 318。电容器522可以是在feol工艺或beol工艺中形成的平行板电容器或其他类型的电容器。与图3中的写入访问开关302中的pfet 310类似,写入访问开关502包括pfet 524,该pfet 524由写入字电压512激活(例如,开关闭合),该写入字电压512是提供给写入字输入514的接地电压v

ss

。

44.图6是cim位单元电路602(0,0)-602(1,1)(统称为cim位单元电路602)的cim位单元阵列电路(cim阵列电路)600的示意图。cim阵列电路600中的cim位单元电路602是图2a中的cim位单元电路200,并且图2a所示的标签在对cim位单元电路602的特征的所有引用中被引用。因此,每个cim位单元电路602包括激活输入210、写入位输入220、写入字输入224和读取位输出216。每个cim位单元电路602存储二进制权重数据206,如图2a所示。

45.cim阵列电路600包括具有cim位单元电路602(0,0)和602(0,1)的行r0、以及具有cim位单元电路602(1,0)和602(1,1)的行r1。cim阵列电路600还包括具有cim位单元电路602(0,0)和602(1,0)的列c0、以及具有cim位单元电路602(0,1)和602(1,1)的列c1。如下面进一步描述的,响应于写入操作,在乘法之前,与每个激活信号208相对应的二进制权重数据206存储在cim位单元电路602中。来自列c0或c1中的每个cim位单元电路602中的乘法的乘积数据212被求和以完成mac运算的“累加”部分。

46.参考图6描述cim阵列电路600的结构细节。cim阵列电路600的行r0和r1包括对应激活线604(0)和604(1)以及对应写入字线606(0)和606(1)。激活线604(0)耦合到行r0中的每个cim位单元电路602的激活输入210,并且激活线604(1)耦合到列r1中的每个cim位单元电路602的激活输入210。写入字线606(0)耦合到行r0中的每个cim位单元电路602的写入字输入224,并且写入字线608(1)耦合到列r1中的每个cim位单元电路602的写入字输出224。

47.列c0和c1包括对应写入位线608(0)和608(1)以及对应读取位线610(0)和610(1)。写入位线608(0)耦合到列c0中的每个cim位单元电路602的写入位输入220,并且写入位线608(1)耦合到列c1中的每个cim位单元电路602的写入位输入220。读取位线610(0)耦合到列c0中的每个cim位单元电路602的读取位输出216,并且读取位线610(1)耦合到列c1中的每个cim位单元电路602的读取位输出216。

48.cim阵列电路600包括分别耦合到读取位线610(0)和610(1)的求和电路612(0)和612(1)。在读取操作中,来自列c0中的每个cim位单元电路602的乘积数据212被累积在读取位线610(0)上。特别地,指示cim位单元电路602(0,0)和602(1,0)中的每个中的乘法结果的乘积电压214被提供给读取位线610(0)。生成乘积数据212作为二进制“1”的列中的每个cim位单元电路602有助于对读取位线610(0)充电,这增加了读取位线610(0)的电压,如下所示。对于生成二进制“1”的乘积数据212的列c0中的cim位单元电路602中的一个,读取位线610(0)上的电压可以根据以下等式确定:

[0049]vrbl

=v

gg

(c

gg

/(c

gg

c

rbl

)),

[0050]

其中:

[0051]vrbl

=向读取位线610(0)生成的电压

[0052]vgg

=从写入位电压218提供的电容性存储电路204中的电容器(例如,244)上的电压

[0053]cgg

=电容性存储电路204中的电容器244的电容

[0054]crbl

=读取位线610(0)的电容

[0055]

求和电路612(0)可以包括例如感测放大器或模数转换器(adc),该感测放大器或adc根据电压v

rbl

生成指示列c0中对读取位线610(o)充电的“1”的数目的总和614(“o”)。类似地,求和电路612(1)生成指示列c1中对读取位线610(1)充电的“1”的数目的总和614(“1”)。以这种方式,cim阵列电路600执行神经网络的mac运算的乘法和累加。

[0056]

与电容性存储电路204中的电容器244的电容c

gg

相比,读取位线610(0)的电容c

rbl

非常小。因此,将读取位线610(0)充电到乘积电压214不会对电容器244放电,因此在乘积数据212被读取之后,二进制权重数据206保持在电容器244上。因此,cim阵列600中的cim位单元电路602的读取操作被称为非破坏性读取操作。

[0057]

图7是用于在神经网络(未示出)中的mac运算中执行二进制乘法示例性cim位单元电路700的示意图,该cim位单元电路700包括用于用二进制权重数据706对电容性存储电路704编程的写入访问开关702。如图2a和图3-图5所示的示例中,cim位单元电路700在激活输入710上接收激活信号708。激活信号708和二进制权重数据706的二进制乘法(例如,基于逻辑and的运算)的乘积数据712被生成为读取位输出716上的乘积电压714。

[0058]

响应于写入字输入724上的写入字电压722,写入访问开关702将写入位输入718耦合到电容性存储电路704的第一端口720。电容性存储电路704的第一端口720耦合到电容器728的第一端子726。电容器728被充电以存储基于在写入位输入718上提供的写入位电压730的二进制权重数据706。

[0059]

与其中电容性存储电路204包括电容器244和读取访问开关246两者的图2a的cim位单元电路200不同,cim位单元电路700的电容性存储电路704仅采用电容器728,即nfet 732。电容器728的第一端子726是nfet 732的栅极734。nfet 732包括源极/漏极738a和漏极/源极738b。这里,不像源极/漏极262和漏极/源极264那样,将源极/漏极738a和漏极/源极738b两者耦合在一起,而是将源极/漏极738a耦合到激活输入710,并且将漏极/源极738b耦合到读取位输出716。在读取位输出716上生成的乘积数据712是二进制权重数据706和在激活输入710上提供的激活信号708的逻辑and的二进制结果。特别地,响应于二进制权重数据706为二进制“1”,在nfet 732的情况下,激活输入710耦合到读取位输出716,并且乘积数据712取激活信号708的值。

[0060]

图7中的写入访问开关702也是nfet 740。因此,与图2a中的三晶体管(3t)cim位单元电路200或图4中的两个晶体管(2t)和单电容器(1c)(2t1c)cim位单元电路400相比,cim位单元电路700能够执行乘法运算,如图2a的cim位单元电路200,但仅包括2个晶体管(732和740)。在这点上,cim位单元电路700所占用的面积小于采用6t sram的先前cim位单元所占用的面积的一半。真值表750说明了cim位单元电路700的基于逻辑and的运算,其与图2b中的真值表270相同。

[0061]

在另一示例中,图8是用于二进制乘法的示例性cim位单元电路800的示意图,该cim位单元电路800包括写入访问开关802,写入访问开关802用于基于在写入位输入810上提供的写入位电压808用二进制权重数据806对电容性存储电路804进行编程。与图7的cim位单元电路700一样,cim位单元电路800是2t电路。cim位单元电路800在激活输入814上接收激活信号812以读取乘积数据816。乘积数据816是激活信号812与二进制权重数据806的二进制乘法(例如,基于逻辑and的运算)的乘积。乘积数据816在读取位输出820上被生成作为乘积电压818。

[0062]

与cim位单元电路700相比,写入访问开关802采用pfet 822作为写入访问开关802,以响应于写入字输入828上的写入字电压826将写入位输入810耦合到电容性存储电路804的第一端口824。电容性存储电路804的第一端口824耦合到由pfet 834提供的电容器832的第一端子830。第一端子830是pfet 834的栅极836。电容器832被充电以存储基于在写入位输入810上提供的写入位电压808的二进制权重数据806。由pfet 822提供的写入访问开关802响应于写入字电压826为接地电压v

ss

(例如,0伏)而将写入位输入810耦合到电容性存储电路804的第一端口824,该接地电压与图7中提供给写入字输入724的写入字电压722极性相反。

[0063]

此外,响应于二进制权重数据806为接地电压v

ss

,电容性存储电路804中的pfet 834将激活输入814耦合到读取位输出820。在这点上,存储在cim位单元电路800中的二进制权重数据806的极性必须与cim位单元电路700中的二进制权重数据706相反,以使pfet 834导通。因此,cim位单元电路800的二进制权重数据806与图7中的二进制权数据706极性相反。图8中的真值表850中说明了cim位单元电路800的基于逻辑and的运算。真值表850示出了,乘积数据816是激活信号812的逻辑and,并且还示出了二进制权重数据806的倒数(在括号中)。与cim位单元电路700类似,cim位单元电路800所占用的面积小于采用6t sram的先前cim位单元所占用的面积的一半。

[0064]

图9是cim位单元电路902(0,0)-902(1,1)(统称为cim位单元电路902)的cim位单元阵列电路(cim阵列电路)900的示意图。cim阵列电路900中的cim位单元电路902是图7中的cim位单元电路700,并且图7的标签关于cim位单元电路902的特征被引用。因此,每个cim位单元电路902包括激活输入710、写入位输入718、写入字输入724和读取位输出716。每个cim位单元电路902存储二进制权重数据706,如图7所示。

[0065]

cim阵列电路900包括具有cim位单元电路902(0,0)和902(0,1)的行r0、以及具有cim位单元电路902(1,0)和902(1,1)的行r1。cim阵列电路900还包括具有cim位单元电路902(0,0)和902(1,0)的列c0、以及具有cim位单元电路902(0,1)和902(1,1)的列c1。如下面进一步描述的,响应于写入操作,在乘法之前,与每个激活信号708相对应的二进制权重数据706存储在cim位单元电路902中。来自列c0或c1中的每个cim位单元电路902中的乘法的乘积数据712被求和以完成mac运算的“累加”部分。

[0066]

行r0和r1包括耦合到对应行中的cim位单元电路902的激活输入710的激活线904(0)和904(1)。行r0和r1还包括耦合到对应行中的cim位单元电路902的写入字输入724的写入字线906(0)和906(1)。列c0和c1包括耦合到对应列中的cim位单元电路902的写入位输入718的写入位线908(0)和908(1)。列c0和c1还包括耦合到对应列中的cim位单元电路902的读取位输出716的读取位线910(0)和910(1)。

[0067]

将二进制权重位数据706写入cim位单元电路902与以上关于将二进制权重数据206写入图6的cim阵列电路600中的cim位单元电路602而描述的相同。然而,由于图2中的电容性存储电路204与图7中的电容性存储器电路704之间的结构差异,从相应cim位单元电路902中读取乘积数据712的操作不同于读取cim阵列电路600中的cim位单元电路602。

[0068]

列c0和c1包括求和电路912(0)和912(1),求和电路912(0)和912(1)用于确定cim阵列电路900的列c0和c1中的一列中的cim位单元电路902中有多少正在存储具有二进制值“1”的二进制权重数据706。激活信号708在激活线904(0)上提供,以在cim位单元电路902中的特定一个的读取位输出716上生成乘积电压714。在cim位单元电路700和800的情况下,激活信号708是电源电压v

dd

或接地电压v

ss

,并且不基于上面关于图6讨论的电荷共享等式。因此,对例如列c0中的每个cim位单元电路902依次逐个执行读取操作。列c0中的求和电路912(0)在与每个读取操作相对应的时间感测乘积电压714,以确定存储在cim位单元电路902中的二进制权重数据706是二进制“1”还是“0”,并且将在该列中感测到的“1”的数目相加。因此,对于由cim位单元电路700形成的阵列(诸如cim阵列电路900)所提供的面积减小的附加权衡是,需要更多的周期来从列中的所有cim位单元电路902中读取乘积数据712,这增加了mac运算的执行时间。如在cim阵列电路600中那样,cim阵列电路900中的读取操作是非破坏性的,二进制权重数据706需要周期性地或偶尔地刷新,并且特定cim位单元电路902可以在读取操作中读取乘积数据712的相同时间(例如,同时)被刷新。

[0069]

图10示出了包括射频(rf)组件1002的示例性无线通信设备1000,其中一个或多个rf组件1002可以是ic的形式,其中任何rf组件1002可以包括cim位单元阵列电路,如图6和图9中的任何一个中所示,该cim位单元阵列电路包括根据本文中公开的任何方面的cim位单元电路,该cim位单元电路提供电容性的基于电荷的数据存储并且在6t sram位单元电路的面积的一半或更少中执行二进制乘法,如图2a、图3-图5、图7和图8中的任何一个中所示。作为示例,无线通信设备1000可以包括任何上述设备或设置在任何上述设备中。如图10所示,无线通信设备1000包括收发器1004和数据处理器1006。数据处理器1006可以包括用于存储数据和程序代码的存储器。收发器1004包括支持双向通信的传输器1008和接收器1010。通常,无线通信设备1000可以包括用于任何数目的通信系统和频带的任何数目的传输器1008和/或接收器1010。收发器1004的全部或一部分可以在一个或多个模拟ic、rfic、混合信号ic等上实现。

[0070]

传输器1008或接收器1010可以用超外差架构或直接转换架构来实现。在超外差架构中,对于接收器1010,信号在多个级中在rf与基带之间进行频率转换,例如,在一个级中从rf到中频(if),然后在另一级中从if到基带。在直接转换架构中,信号在一个级中在rf与基带之间进行频率转换。超外差和直接转换架构可以使用不同电路块和/或具有不同要求。在图10中的无线通信设备1000中,传输器1008和接收器1010用直接转换架构来实现。

[0071]

在传输路径中,数据处理器1006处理要传输的数据,并且向传输器1008提供i和q模拟输出信号。在示例性无线通信设备1000中,数据处理器1006包括数模转换器(dac)1012(1)、1012(2),该dac 1012(1)、1012(2)用于将由数据处理器1006生成的数字信号转换为i和q模拟输出信号,例如i和q输出电流,以供进一步处理。

[0072]

在传输器1008内,低通滤波器1014(1)、1014(2)分别对i和q模拟输出信号进行滤波,以去除先前数模转换引起的不期望的信号。放大器(amp)1016(1)、1016(2)分别放大来

自低通滤波器1014(1)、1014(2)的信号,并且提供i和q基带信号。上变频器1018通过混频器1020(1)、1020(2)利用来自tx lo信号发生器1022的i和q传输(tx)本地振荡器(lo)信号对i和q基带信号进行上变频,以提供上变频信号1024。滤波器1026对上变频信号1024进行滤波,以去除由上变频引起的不期望的信号以及接收频带中的噪声。功率放大器(pa)1028放大来自滤波器1026的上变频信号1024以获取期望的输出功率电平并且提供传输rf信号。传输rf信号被路由通过双工器或开关1030,并且经由天线1032进行传输。

[0073]

在接收路径中,天线1032接收由基站传输的信号,并且提供接收的rf信号,该信号被路由通过双工器或开关1030并且提供给低噪声放大器(lna)1034。双工器或开关1030被设计为以特定接收(rx)到tx双工器频率分离进行操作,使得rx信号与tx信号隔离。所接收的rf信号由lna 1034放大并且由滤波器1036滤波以获取期望的rf输入信号。下变频混频器1038(1)、1038(2)将滤波器1036的输出与来自rx lo信号发生器1040的i和q rx lo信号(即,lo_i和lo_q)进行混频,以生成i和q基带信号。i和q基带信号由amp 1042(1)、1042(2)放大,并且由低通滤波器1044(1)、1044(2)进一步滤波,以获取i和q模拟输入信号,这些信号被提供给数据处理器1006。在该示例中,数据处理器1006包括用于将模拟输入信号转换为数字信号以由数据处理器1006进一步处理的adc 1046(1)、1046(2)。

[0074]

在图10的无线通信设备1000中,tx lo信号发生器1022生成用于上变频的i和q tx lo信号,而rx lo信号发生器1040生成用于下变频的i和q rx lo信号。每个lo信号是具有特定基频的周期性信号。tx锁相环(pll)电路1048从数据处理器1006接收定时信息,并且生成用于调节来自tx lo信号发生器1022的tx lo信号的频率和/或相位的控制信号。类似地,rx pll电路1050从数据处理器1006接收定时信息,并且生成用于调节来自rx lo信号发生器1040的rx lo信号的频率和/或相位的控制信号。

[0075]

无线通信设备1000可以设置在或集成到任何上述基于处理器的设备中,该无线通信设备1000每个包括cim位单元阵列电路,如图6和图9中的任何一个中所示,该cim位单元阵列电路包括根据本文中公开的任何方面的cim位单元电路,该cim位单元电路提供电容性的基于电荷的数据存储并且在6t sram位单元电路的面积的一半或更少中执行二进制乘法,如图2a、图3-图5、图7和图8中的任何一个中所示。示例(但不限于)包括机顶盒、娱乐单元、导航设备、通信设备、固定位置数据单元、移动位置数据单元、全球定位系统(gps)设备、移动电话、蜂窝电话、智能电话、会话发起协议(sip)电话、平板电脑、平板手机、服务器、计算机、便携式计算机、移动计算设备、可穿戴计算设备(例如,智能手表、健康或健身跟踪器、眼镜等)、台式计算机、个人数字助理(pda)、显示器、计算机显示器、电视、调谐器、无线电、卫星无线电、音乐播放器、数字音乐播放器、便携式音乐播放器、数字视频播放器、视频播放器、数字视频盘(dvd)播放器、便携式数字视频播放器、机动车、车辆组件、航空电子系统、无人机和多旋翼直升机。

[0076]

在这点上,图11示出了基于处理器的系统1100的示例,该系统1100包括cim位单元阵列电路,如图6和图9中的任何一个中所示,该cim位单元阵列电路包括根据本文中公开的任何方面的cim位单元电路,该cim位单元电路提供电容性的基于电荷的数据存储并且在6t sram位单元电路的面积的一半或更少中执行二进制乘法,如图2a、图3-图5、图7和图8中的任何一个中所示。在该示例中,基于处理器的系统1100包括一个或多个中央处理器单元(cpu)1102,cpu 1102其也可以称为cpu或处理器核,每个cpu 1102包括一个或多个处理器

1104。(多个)cpu 1102可以具有耦合到(多个)处理器1104以快速访问临时存储的数据的高速缓冲存储器1106。作为示例,(多个)处理器1104可以包括根据本文中公开的任何方面的sram位单元阵列,该sram位单元阵列包括最小化的不活动位单元区域、最小化的不活跃阵列区域、和与存储电路活动区域重叠以减少阵列长度的栅极触点,如图4和图8中的任何一个中所示。(多个)cpu 1102耦合到系统总线1108,并且可以互连基于处理器的系统1100中包括的主设备和从设备。众所周知,(多个)cpu 1102通过在系统总线1108上交换地址、控制和数据信息来与这些其他设备通信。例如,作为从设备的示例,(多个)cpu 1102可以向存储器控制器1110传送总线事务请求。尽管图11中未示出,但可以提供多个系统总线1108,其中每个系统总线1102构成不同结构。

[0077]

其他主设备和从设备可以连接到系统总线1108。如图11所示,作为示例,这些设备可以包括存储器系统1112(其包括存储器控制器1110和一个或多个存储器阵列1114)、一个或多个输入设备1116、一个或多个输出设备1118、一个或多个网络接口设备1120和一个或多个显示控制器1122。存储器系统1112、一个或多个输入设备1116、一个或多个输出设备1118、一个或多个网络接口设备1120和一个或多个显示控制器1122中的每个可以包括cim位单元阵列电路,如图6和图9中的任何一个中所示,该cim位单元阵列电路包括根据本文中公开的任何方面的cim位单元电路,该cim位单元电路提供电容性的基于电荷的数据存储并且在6t sram位单元电路的面积的一半或更少中执行二进制乘法,如图2a、图3-图5、图7和图8中的任何一个中所示。(多个)输入设备1116可以包括任何类型的输入设备,包括但不限于输入键、开关、语音处理器等。(多个)输出设备1118可以包括任何类型的输出设备,包括但不限于音频、视频、其他视觉指示器等。(多个)网络接口设备1120可以是被配置为允许与网络1124交换数据的任何设备。网络1124可以是任何类型的网络,包括但不限于有线或无线网络、专用或公共网络、局域网(lan)、无线局域网(wlan)、广域网(wan)、bluetooth

tm

网络和互联网。(多个)网络接口设备1120可以被配置为支持所需要的任何类型的通信协议。

[0078]

(多个)cpu 1102还可以被配置为通过系统总线1108访问(多个)显示控制器1122,以控制发送给一个或多个显示器1126的信息。(多个)显示控制器1122经由一个或多个视频处理器1128将要显示的信息发送给(多个)显示器1126,该视频处理器1128将要显示的信息处理成适合(多个)显示器1126的格式。(多个)显示器1126可以包括任何类型的显示器,包括但不限于阴极射线管(crt)、液晶显示器(lcd)、等离子显示器、发光二极管(led)显示器等。(多个)显示控制器1122、(多个)显示器1126和/或(多个)视频处理器1128可以包括cim位单元阵列电路,如图6和图9中的任何一个中所示,该cim位单元阵列电路包括根据本文中公开的任何方面的cim位单元电路,该cim位单元电路提供电容性的基于电荷的数据存储并且在6t sram位单元电路的面积的一半或更少中执行二进制乘法,如图2a、图3-图5、图7和图8中的任何一个中所示。

[0079]

本领域技术人员将进一步认识到,结合本文中公开的各方面而描述的各种说明性逻辑块、模块、电路和算法可以实现为电子硬件、存储在存储器或另一计算机可读介质中并且由处理器或其他处理设备执行的指令、或这两者的组合。作为示例,本文中描述的主设备和从设备可以用于任何电路、硬件组件、ic或ic芯片。本文中公开的存储器可以是任何类型和大小的存储器,并且可以被配置为存储期望的任何类型的信息。为了清楚地说明这种可互换性,上面已经大体上就其功能性描述了各种说明性组件、块、模块、电路和步骤。这样的

功能如何实现取决于特定应用、设计选择和/或施加在整个系统上的设计约束。熟练的技术人员可以针对每个特定应用以不同方式实现所描述的功能,但是这样的实现决策不应当被解释为导致偏离本公开的范围。

[0080]

结合本文中公开的各方面而描述的各种说明性逻辑块、模块和电路可以用被设计为执行本文中描述的功能的处理器、数字信号处理器(dsp)、专用集成电路(asic)、现场可编程门阵列(fpga)或其他可编程逻辑器件、离散门或晶体管逻辑、离散硬件组件、或其任何组合来实现或执行。处理器可以是微处理器,但在替代方案中,处理器可以是任何常规处理器、控制器、微控制器或状态机。处理器还可以被实现为计算设备的组合(例如,dsp和微处理器的组合、多个微处理器、与dsp核相结合的一个或多个微处理器、或任何其他这样的配置)。

[0081]

本文中公开的各方面可以体现在硬件和存储在硬件中的指令中,并且可以驻留在例如随机存取存储器(ram)、闪存、只读存储器(rom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)、寄存器、硬盘、可移动盘、cd-rom、或本领域已知的任何其他形式的计算机可读介质中。示例性存储介质耦合到处理器,使得处理器可以从存储介质读取信息并且向存储介质写入信息。在替代方案中,存储介质可以与处理器成一体。处理器和存储介质可以驻留在asic中。asic可以驻留在远程站中。在替代方案中,处理器和存储介质可以作为分立组件驻留在远程站、基站或服务器中。

[0082]

还应当注意,本文中的任何示例性方面中描述的操作步骤都是为了提供示例和讨论。所描述的操作可以以不同于所示序列的很多不同序列来执行。此外,在单个操作步骤中描述的操作实际上可以在多个不同步骤中执行。此外,在示例性方面中讨论的一个或多个操作步骤可以组合。应当理解,流程图中所示的操作步骤可以进行很多不同修改,这对于本领域的技术人员来说是很清楚的。本领域技术人员还将理解,信息和信号可以使用各种不同科技和技术中的任何一种来表示。例如,在整个以上描述中引用的数据、指令、命令、信息、信号、比特、符号和芯片可以通过电压、电流、电磁波、磁场或粒子、光场或粒子、或其任何组合来表示。

[0083]

提供本公开的先前描述是为了使得本领域技术人员能够制作或使用本公开。对本领域技术人员来说,对本公开的各种修改将是很清楚的,并且本文中定义的一般原理可以应用于其他变型。因此,本公开不旨在局限于本文中描述的示例和设计,而是应当被给予与本文中公开的原理和新颖特征一致的最宽范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。