1.本发明涉及集成电路技术领域,特别涉及一种半导体器件及其制作方法。

背景技术:

2.在集成电路制造工艺中,在完成半导体结构的前段工艺的制作和后段工艺的金属互连线的制作后,需要在顶层金属层上形成钝化层。所述钝化层可以减少半导体结构内部氧化层中的各种电荷,增强半导体结构对离子沾污的阻挡能量,保护半导体结构的内部器件的互连以及半导体结构表面的电特性,防止半导体结构的器件受到机械损伤或化学损伤。

3.然而,随着集成电路制造工艺技术特征尺寸的缩小,顶层金属层需要更低的阻值更高的厚度以适配不同的终端设计需求。顶层金属层变厚存在的一个问题是应力变大,顶层金属层内分子间具有内力,顶层金属层变厚使得分子的数量增加,从而导致总内力变大,在宏观上体现为应力变大。而传统的钝化层一般是氧化硅与氮化硅的叠层,顶层金属层的应力过大会导致施加到位于所述顶层金属层上的钝化层的应力过大,从而使得所述钝化层产生裂纹(crack),进而导致产品的可靠性降低。

技术实现要素:

4.本发明的目的在于提供一种半导体器件及其制作方法,能够减小钝化层中的裂纹,提高产品的可靠性。

5.为解决上述技术问题,本发明提供一种半导体器件的制作方法,包括以下步骤:提供一衬底,所述衬底上形成有顶层金属层;在所述顶层金属层上形成钝化层,所述钝化层包含依次层叠的第一氧化物层、氮化物层与第二氧化物层。

6.可选的,采用sod工艺形成所述第一氧化物层,采用hdp cvd工艺形成所述第二氧化物层。

7.可选的,所述钝化层包含依次层叠的第一氧化硅层、氮化硅层与第二氧化硅层。

8.可选的,所述钝化层包含依次层叠的第一氧化硅层、氮氧化硅层与第二氧化硅层。

9.可选的,所述衬底上形成有金属互连结构,所述顶层金属层是位于所述金属互连结构中顶层的金属层。

10.可选的,形成所述钝化层之后,所述制作方法还包括:在所述钝化层内形成开口,所述开口暴露出所述顶层金属层。

11.相应的,本发明还提供一种半导体器件,包括:衬底;位于所述衬底上的顶层金属层;以及位于所述顶层金属层上的钝化层,所述钝化层包含依次层叠的第一氧化物层、氮化物层与第二氧化物层。

12.可选的,所述钝化层包含依次层叠的第一氧化硅层、氮化硅层与第二氧化硅层。

13.可选的,所述钝化层包含依次层叠的第一氧化硅层、氮氧化硅层与第二氧化硅层。

14.可选的,所述衬底上形成有金属互连结构,所述顶层金属层是位于所述金属互连结构中顶层的金属层。

15.本发明提供的半导体器件及其制作方法中,在顶层金属层上形成钝化层,钝化层包含依次层叠的第一氧化物层、氮化物层与第二氧化物层,通过氧化物、氮化物与氧化物三层层叠结构来减小所述钝化层的应力,从而提高所述钝化层抵抗外界应力的能力,以避免所述顶层金属层变厚时在所述钝化层中产生裂纹,从而提高产品的可靠性。

16.进一步的,采用sod工艺形成第一氧化物层,由此形成的第一氧化物层应力小,填充能力比较好,能够进一步减少所述钝化层中裂纹的产生。

17.进一步的,所述钝化层包含依次层叠的第一氧化硅层、氮氧化硅层与第二氧化硅层,氮氧化硅层中的硅氧键的分子间作用力小于氮化硅中的硅氮键的分子间作用力,即与氮化硅层相比,氮氧化硅层本身的应力比较小,采用氮氧化硅层作为中间层能够减小所述钝化层的应力,进一步减少钝化层中裂纹的产生。

附图说明

18.本领域的普通技术人员应当理解,提供的附图用于更好地理解本发明,而不对本发明的范围构成任何限定。

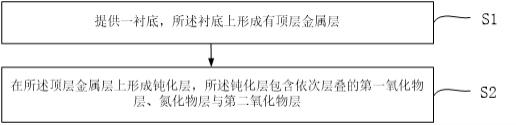

19.图1是本发明一实施例提供的半导体器件的制作方法的流程图。

20.图2是本发明一实施例提供的形成顶层金属层之后的结构示意图。

21.图3是本发明一实施例提供的形成钝化层之后的结构示意图。

22.图4是本发明一实施例提供的形成开口之后的结构示意图。

23.附图标记:10-衬底;20-金属互连结构;21-第一金属互连层;211-第一层间介质层;212-第一金属插塞;213-第一金属层;22-第二金属互连层;221-第二层间介质层;222-第二金属插塞;223-第二金属层;23-第三金属互连层;231-第三层间介质层;232-第三金属插塞;233-第三金属层;24-第四金属互连层;241-第四层间介质层;242-第四金属插塞;243-顶层金属层;30-钝化层;31-第一氧化物层;32-氮化物层;33-第二氧化物层;34-开口。

具体实施方式

24.为使本发明的目的、优点和特征更加清楚,以下结合附图和具体实施例对本发明作进一步详细说明。需说明的是,附图均采用非常简化的形式且未按比例绘制,仅用以方便、明晰地辅助说明本发明实施例的目的。此外,附图所展示的结构往往是实际结构的一部分。特别的,各附图需要展示的侧重点不同,有时会采用不同的比例。

25.如在本发明中所使用的,单数形式“一”、“一个”以及“该”包括复数对象,术语“或”通常是以包括“和/或”的含义而进行使用的,术语“若干”通常是以包括“至少一个”的含义而进行使用的,术语“至少两个”通常是以包括“两个或两个以上”的含义而进行使用的,此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”、“第三”的特征可以明

示或者隐含地包括一个或者至少两个该特征,除非内容另外明确指出外。

26.图1是本发明一实施例提供的半导体器件的制作方法的流程图。

27.如图1所示,所述半导体器件的制作方法包括以下步骤:s1:提供一衬底,所述衬底上形成有顶层金属层;s2:在所述顶层金属层上形成钝化层,所述钝化层包含依次层叠的第一氧化物层、氮化物层与第二氧化物层。

28.图2至图4是本发明一实施例提供的半导体器件的制作方法的各步骤的结构示意图。接下来,将结合图1与图2~图4对本发明一实施例所提供的半导体器件的制作方法进行详细说明。

29.在步骤s1中,请参照图2所示,提供一衬底10,所述衬底10上形成有顶层金属层243。

30.其中,所述衬底10的材料可以为硅、锗、锗化硅、碳化硅、砷化镓或镓化铟等,也可以是绝缘体上硅,绝缘体上锗;或者还可以为其它的材料,例如砷化镓等iii-v族化合物。在本实施例中,所述衬底10的材料优选为硅。

31.所述衬底10上或所述衬底10内可以形成有多个前道器件(未图示),例如pmos晶体管、nmos晶体管、电阻器、电容器或电感器等。所述衬底10上形成有金属互连结构20,所述金属互连结构20可以与所述前道器件相连通。所述金属互连结构20包含多层金属互连层,每层金属互连层均包含层间介质层、位于所述层间介质层内的金属插塞以及位于所述层间介质层上且与所述金属插塞连接的金属层。位于顶层的金属互连层内的金属层作为顶层金属层。

32.图2中示出了四层金属互连层,分别为依次位于所述衬底10上且彼此连接的第一金属互连层21、第二金属互连层22、第三金属互连层23与第四金属互连层24。所述第一金属互连层21包含位于所述衬底10上的第一层间介质层211、位于所述第一层间介质层211内的第一金属插塞212,位于所述第一层间介质层211上且与所述第一金属插塞212相连接的第一金属层213。所述第二金属互连层22包含覆盖所述第一金属层213和所述第一层间介质层211的第二层间介质层221,位于所述第二层间介质层221内且与所述第一金属层213相连接的第二金属插塞222,位于所述第二层间介质层221上且与所述第二金属插塞222相连接的第二金属层223。同样的,所述第三金属互连层23包含覆盖所述第二金属层223和所述第二层间介质层221的第三层间介质层231,位于所述第三层间介质层231内与所述第二金属层223相连接的第三金属插塞232,位于所述第三层间介质层231上且与所述第三金属插塞232相连接的第三金属层233。所述第四金属互连层24包含覆盖所述第三金属层233与所述第三层间介质层231的第四层间介质层241,位于所述第四层间介质层241内且与所述第三金属层233相连接的第四金属插塞242,位于所述第四层间介质层241上且与所述第四金属插塞242相连接的第四金属层,所述第四金属层即为所述顶层金属层243,是所述金属互连结构20中位于顶层的金属互连层内的金属层。当然,所述金属互连结构20并不仅限于四层所述金属互连层,还可以为两层、三层或更多层。可以理解的是,所述金属互连结构20也不仅限于图2所示的结构,还可以是本领域技术人员已知的其他任意金属互连结构。

33.所述金属互连结构20中的金属层与金属插塞的材质为铜,还可以为铝或铝铜合金等导电材料。所述层间介质层的材料为氧化硅。

34.在步骤s2中,请参照图3所示,在所述顶层金属层243上形成钝化层30,所述钝化层30包含依次层叠的第一氧化物层31、氮化物层32与第二氧化物层33。

35.本实施例中,所述第一氧化物层31的材质优选为氧化硅,所述第二氧化物层33的材质也优选为氧化硅,所述氮化物层32的材质优选为氮化硅或氮氧化硅(sion)。即所述钝化层30包含依次层叠的第一氧化硅层、氮化硅层与第二氧化硅层,或者,所述钝化层30包含依次层叠的第一氧化硅层、氮氧化硅层与第二氧化硅层,当然并不仅限于此。

36.本实施例中,首先形成第一氧化物层31,所述第一氧化物层31覆盖所述顶层金属层243。可以采用sod(spin on dielectric,旋涂电介质)工艺形成所述第一氧化物层31,与teos(正硅酸乙酯)工艺相比,采用sod工艺形成的所述第一氧化物层31应力小,密度高,填充能力比较好,能够减小所述钝化层30中裂纹的产生。当然,也可以采用本领域技术人员已知的其他方法形成所述第一氧化物层31。

37.sod工艺首先形成旋涂电介质层,所述旋涂电介质层的材料为同时包含氮、氢、硅的高分子化合物,示例性的,所述旋涂电介质层的材料可以为全氢聚硅氮烷(perhydropolysilazane,phps),其为一种已存在于实际制作工艺中的材质,特征在于该材质具有流动性,因此有较佳的填洞能力,且该材质经过蒸气加热或紫外光照射后,内部的氮原子将会被移出,而同时与空气中的氧原子进行反应,以转化成绝缘的氧化硅层。需要说明的是,虽然本实施例中以全氢聚硅氮烷为例,但本发明不限于此,其他具有类似功能(具流动性且经过蒸气加热或紫外光照射后可转换成氧化硅层)的材质也可以作为所述旋涂电介质层。接着,对所述旋涂电介质层进行处理,例如通入水蒸气,或者在一含氧环境中进行热处理或紫外光处理等,其中含氧环境包含蒸汽、氧气或臭氧等。所述旋涂电介质层包含有氮、氢、硅等原子,在转换成为氧化硅的过程中,将会与空气中的氧原子进行反应,同时也会消耗所述旋涂电介质层本身的硅原子,最终转化为氧化硅。

38.接着,形成氮化物层32,所述氮化物层32覆盖所述第一氧化物层31。可以采用化学气相沉积法(chemical vapor deposition,cvd)、物理气相沉积法(physical vapor deposition,pvd)、原子层沉积法(atomic layer deposition,ald)等本领域技术人员已知的方法形成所述氮化物层32。

39.之后,形成第二氧化物层33,所述第二氧化物层33覆盖所述氮化物层32。可以采用hdp cvd(high density plasma chemical vapor deposition,高密度等离子体化学气相淀积)工艺形成所述第二氧化物层33,但不限于此。采用hdp cvd工艺形成所述第二氧化物层33,与所述氮化物层32、所述第一氧化物层31相组合能够进一步减小所述钝化层30的应力。

40.本发明通过第一氧化物层31、氮化物层32与第二氧化物层33三层层叠结构来减小所述钝化层30的应力,当所述顶层金属层243的厚度增加导致应力增加时,所述钝化层30的应力减小,抵抗外界应力的能力提高,能够避免在所述钝化层30中产生裂纹,从而提高产品的可靠性。

41.进一步的,采用sod工艺形成第一氧化物层31,由此形成的第一氧化物层31应力小,填充能力比较好,能够进一步减少钝化层30中裂纹的产生。

42.并且,当所述氮化物层32的材质为氮氧化硅时,氮氧化硅层中的硅氧键(si-o)的分子间作用力小于氮化硅中的硅氮键(si-n)的分子间作用力,即与氮化硅层相比,氮氧化

硅层本身的应力比较小,采用氮氧化硅层作为中间层能够减小所述钝化层30的应力,进一步减少所述钝化层30中裂纹的产生。

43.所述第一氧化物层31、所述氮化物层32与所述第二氧化物层33的厚度可以根据实际的工艺条件来决定,本发明对此不作限定。示例性的,由于所述顶层金属层243的形貌呈台阶状,而所述第一氧化物层31首先覆盖所述顶层金属层243,因此,所述第一氧化物层31的厚度可以比较大,而所述氮化物层32与所述第二氧化物层33的厚度则可以比较小,即所述第一氧化物层31的厚度大于所述氮化物层32与所述第二氧化物层33的厚度。而所述氮化物层32与所述第二氧化物层33的厚度可以相等,也可以不相等。

44.请参考图4所示,在形成所述钝化层30之后,所述制作方法还包括:在所述钝化层30内形成开口34,所述开口34暴露出所述顶层金属层243。示例性的,形成所述开口34的方法可以包括:首先在所述钝化层30上形成光刻胶层,对所述光刻胶层进行曝光与显影,形成图形化的光刻胶层,接着,以所述图形化的光刻胶层对所述钝化层30进行刻蚀至暴露出所述顶层金属层243,以形成开口34;最后通过灰化工艺或刻蚀工艺去除所述图形化的光刻胶层。当然也可以采用其他材质的掩膜层为掩膜对所述钝化层30进行刻蚀。后续还可以执行在所述开口34内填充金属,制作焊垫等工艺步骤。

45.本发明提供的半导体器件的制作方法中,在顶层金属层243上形成钝化层30,所述钝化层30包含依次层叠的第一氧化物层31、氮化物层32与第二氧化物层33,通过氧化物、氮化物与氧化物三层层叠的结构来减小所述钝化层30的应力,从而提高所述钝化层30抵抗外界应力的能力,以避免所述顶层金属层243变厚时在所述钝化层30中产生裂纹,从而提高了产品的可靠性。

46.进一步的,采用sod工艺形成第一氧化物层31,由此形成的第一氧化物层31应力小,填充能力比较好,能够进一步减少所述钝化层30中裂纹的产生。

47.进一步的,所述钝化层30包含依次层叠的第一氧化硅层、氮氧化硅层与第二氧化硅层,氮氧化硅层中的硅氧键的分子间作用力小于氮化硅中的硅氮键的分子间作用力,即与氮化硅层相比,氮氧化硅层本身的应力比较小,采用氮氧化硅层作为中间层能够减小了所述钝化层30的应力,进一步减少所述钝化层30中的裂纹。

48.相应的,本发明还提供一种半导体器件,采用如上所述的半导体器件的制作方法制作而成。请参考图4所示,所述半导体器件包括:衬底10;位于所述衬底10上的顶层金属层243;位于所述顶层金属层243上的钝化层30,所述钝化层30包含依次层叠的第一氧化物层31、氮化物层32与第二氧化物层33。

49.进一步的,所述第一氧化物层31的材质包含氧化硅,所述第二氧化物层33的材质包含氧化硅,所述氮化物层32的材质包含氮化硅或氮氧化硅,所述钝化层30包含依次层叠的第一氧化硅层、氮化硅层与第二氧化硅层,或者,所述钝化层30包含依次层叠的第一氧化硅层、氮氧化硅层与第二氧化硅层。

50.当所述钝化层30的材质为氮氧化硅时,与氮化硅相比,氮氧化硅层中的硅氧键的分子间作用力小于氮化硅中的硅氮键的分子间作用力,即氮氧化硅层本身的应力比较小,采用氮氧化硅层作为中间层能够减小了所述钝化层30的应力,减少钝化层30中的裂纹。

51.进一步的,所述衬底10上形成有金属互连结构20,所述顶层金属层243是位于所述金属互连结构20中顶层的金属层。所述金属互连结构20可以包含多层金属互连层,如图4所示,所述金属互连结构20包含第一金属互连层21、第二金属互连层22、第三金属互连层23与第四金属互连层24,所述第四金属互连层24作为顶层的金属互连层,其所包含的第四金属层作为顶层金属层243。当然,所述金属互连结构20并不仅限于包含四层金属互连层,可包含任意层数的金属互连层,可以根据实际的需求来确定。

52.本发明提供的半导体器件中,钝化层30包含依次层叠的第一氧化物层31、氮化物层32与第二氧化物层33,通过氧化物、氮化物与氧化物三层层叠的结构减小所述钝化层30的应力,从而提高所述钝化层30抵抗外界应力的能力,以避免所述顶层金属层243变厚时在所述钝化层30中产生裂纹,从而提高了产品的可靠性。

53.并且,采用如上所述的sod工艺形成的第一氧化物层31,应力小,填充能力比较好,能够进一步减少所述钝化层30中裂纹的产生。

54.另外,所述钝化层30包含依次层叠的第一氧化硅层、氮氧化硅层与第二氧化硅层,氮氧化硅层中的硅氧键的分子间作用力小于氮化硅中的硅氮键的分子间作用力,即与氮化硅层相比,氮氧化硅层本身的应力比较小,采用氮氧化硅层作为中间层能够减小所述钝化层30的应力,进一步减少所述钝化层30中的裂纹。

55.上述描述仅是对本发明较佳实施例的描述,并非对本发明权利范围的任何限定,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。