1.本发明有关于一种半导体装置,特别有关于一种增加电阻元件的耐压以及静电放电保护的半导体装置。

背景技术:

2.随着高压集成电路的发展,特别是对于一些用于高压交流电的交流转直流(ac-dc)电路,部分电阻元件需要承受数百伏的高电压。然而,在数百伏的高电压之前,传统的高压电阻元件就可能会先遇到元件被击穿问题,使得传统的电阻已经无法满足需求。

3.通过在场氧化层(field oxide layer)上制作多晶硅(polysilicon)电阻能够大大提高耐压,而耐压主要取决于场氧化层的厚度,一般工艺的场氧化层的耐压能够达到300~400v。然而对于高压交流电的交流转直流电路而言,电阻元件接受的最高峰值电压可能会高达500~650v,使得多晶硅电阻无法满足需求。因此,有必要针对电阻元件的耐压进行提升。

技术实现要素:

4.本发明提出的半导体装置,除了能够增加电阻元件的耐压程度,更能够提供静电电荷排除的路径,使得多晶硅电阻除了满足高压应用的需求外,更能在多晶硅电阻的一端有静电放电保护的需求时,提供所需的保护功能。

5.有鉴于此,本发明提出一种半导体装置,包括一半导体基板、一第一阱、一第二阱、一场氧化层以及一多晶硅层。上述半导体基板具有一第一导电型。上述第一阱形成于上述半导体基板之中且具有一第二导电型。上述第二阱形成于上述第一阱之中,且具有上述第一导电型。上述场氧化层形成于上述第二阱之上。上述多晶硅层形成于上述场氧化层之上且形成一电阻元件。

6.根据本发明的一实施例,上述半导体装置更包括一第一顶掺杂层以及一第二顶掺杂层。上述第一顶掺杂层形成于上述第一阱中且具有上述第一导电型。上述第二顶掺杂层形成于上述第一阱中且具有上述第一导电型,其中上述第一顶掺杂层以及上述第二顶掺杂层位于上述第二阱的两侧,且分别与上述第二阱相互分离。

7.根据本发明的一实施例,上述半导体装置更包括一第三阱以及一掺杂区。上述第三阱形成于上述半导体基板之中且具有上述第一导电型。上述掺杂区形成于上述第三阱且具有上述第一导电型,其中上述掺杂区耦接至一接地端。

8.本发明更提出一种半导体装置,包括一半导体基板、一第一阱、一第二阱、一第一掺杂区、一场氧化层以及一多晶硅层。上述半导体基板具有一第一导电型。上述第一阱形成于上述半导体基板之中且具有一第二导电型。上述第二阱形成于上述第一阱之中且具有上述第二导电型。上述第一掺杂区形成于上述第二阱之中且具有上述第二导电型。上述场氧化层形成于上述第一阱之上且环绕上述第一掺杂区。上述多晶硅层形成于上述场氧化层之上且形成一电阻元件。

9.根据本发明的一实施例,上述半导体装置更包括一第一顶掺杂层以及一第二顶掺杂层。上述第一顶掺杂层形成于上述第一阱中且具有上述第一导电型。上述第二顶掺杂层形成于上述第一阱中且具有上述第一导电型,其中上述第一顶掺杂层以及上述第二顶掺杂层位于上述第二阱的两侧,其中上述电阻元件更形成于上述第一顶掺杂层以及上述第二顶掺杂层之上。

10.根据本发明的一实施例,上述半导体装置更包括一第三阱以及一第二掺杂区。上述第三阱形成于上述半导体基板之中且具有上述第一导电型。上述第二掺杂区形成于上述第三阱之中且具有上述第一导电型。

11.根据本发明的一实施例,上述电阻元件具有耦接至一高电压电平的一第一端点以及耦接至一低电压电平的一第二端点,其中上述第一掺杂区耦接至上述高电压电平,上述第二掺杂区耦接至一接地端。

12.根据本发明的另一实施例,上述半导体装置更包括一第三掺杂区。上述第三掺杂区形成于上述第三阱、与上述第二掺杂区相邻且具有上述第二导电型,其中上述第三掺杂区耦接至上述接地端,其中上述第一掺杂区、上述第二掺杂区以及上述第三掺杂区形成一寄生双极性晶体管。

13.根据本发明的另一实施例,上述半导体装置更包括一第四掺杂区以及一第五掺杂区。上述第四掺杂区形成于上述第二阱、与上述第一掺杂区相邻且具有上述第一导电型。上述第五掺杂区形成于上述半导体基板之中且具有上述第二导电型。

14.根据本发明的一实施例,上述第四掺杂区耦接至上述高电压电平,上述第五掺杂区耦接至上述接地端,其中上述第五掺杂区与上述第三阱为相互分离,其中上述第一掺杂区、上述第四掺杂区、上述第二掺杂区以及上述第五掺杂区形成一寄生硅控整流器。

附图说明

15.图1显示根据本发明的一实施例所述的半导体装置的剖面图;

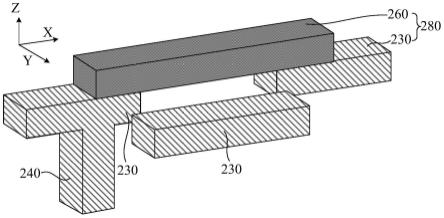

16.图2显示根据本发明的图1所述的多晶硅层的俯视图;

17.图3显示根据本发明的另一实施例所述的半导体装置的剖面图;

18.图4显示根据本发明的图3所述的多晶硅层的俯视图;

19.图5显示根据本发明的另一实施例所述的半导体装置的剖面图;以及

20.图6显示根据本发明的另一实施例所述的半导体装置的剖面图。

21.附图标号

22.100,300,500,600:半导体装置

23.200,400:电阻元件

24.sub:半导体基板

25.w1:第一阱

26.w2:第二阱

27.w3:第三阱

28.top1:第一顶掺杂层

29.top2:第二顶掺杂层

30.fox:场氧化层

31.ply:多晶硅层

32.r:电阻元件

33.g:分布宽度

34.h:阱宽度

35.pad:焊垫

36.n1:第一节点

37.n2:第二节点

38.vh:高电压电平

39.vl:低电压电平

40.gnd:接地端

41.d:掺杂区

42.dp1:第一寄生二极管

43.dp2:第二寄生二极管

44.dp3:第三寄生二极管

45.d1:第一掺杂区

46.d2:第二掺杂区

47.d3:第三掺杂区

48.d4:第四掺杂区

49.d5:第五掺杂区

50.x1:第一宽度

51.x2:第二宽度

52.npn:寄生双极性晶体管

具体实施方式

53.以下针对本发明一些实施例的半导体基板、半导体装置及半导体装置的制造方法作详细说明。应了解的是,以下的叙述提供许多不同的实施例或例子,用以实施本发明一些实施例的不同样态。以下所述特定的元件及排列方式仅为简单清楚描述本发明一些实施例。当然,这些仅用以举例而非本发明的限定。此外,在不同实施例中可能使用重复的标号或标示。这些重复仅为了简单清楚地叙述本发明一些实施例,不代表所讨论的不同实施例及/或结构之间具有任何关连性。再者,当述及一第一材料层位于一第二材料层上或之上时,包括第一材料层与第二材料层直接接触的情形。或者,亦可能间隔有一或更多其它材料层的情形,在此情形中,第一材料层与第二材料层之间可能不直接接触。

54.此外,实施例中可能使用相对性的用语,例如“较低”或“底部”及“较高”或“顶部”,以描述图式的一个元件对于另一元件的相对关系。能理解的是,如果将图式的装置翻转使其上下颠倒,则所叙述在“较低”侧的元件将会成为在“较高”侧的元件。

55.在此,“约”、“大约”、“大抵”的用语通常表示在一给定值或范围的20%之内,较佳是10%之内,且更佳是5%之内,或3%之内,或2%之内,或1%之内,或0.5%之内。在此给定的数量为大约的数量,亦即在没有特定说明“约”、“大约”、“大抵”的情况下,仍可隐含“约”、“大约”、“大抵”的含义。

56.能理解的是,虽然在此可使用用语“第一”、“第二”、“第三”等来叙述各种元件、组成成分、区域、层、及/或部分,这些元件、组成成分、区域、层、及/或部分不应被这些用语限定,且这些用语仅是用来区别不同的元件、组成成分、区域、层、及/或部分。因此,以下讨论的一第一元件、组成成分、区域、层、及/或部分可在不偏离本发明一些实施例的教示的情况下被称为一第二元件、组成成分、区域、层、及/或部分。

57.除非另外定义,在此使用的全部用语(包括技术及科学用语)具有与此篇发明所属的本领域技术人员所通常理解的相同涵义。能理解的是,这些用语,例如在通常使用的字典中定义的用语,应被解读成具有与相关技术及本发明的背景或上下文一致的意思,而不应以一理想化或过度正式的方式解读,除非在本发明实施例有特别定义。

58.本发明一些实施例可配合图式一并理解,本发明实施例的图式亦被视为本发明实施例说明的一部分。需了解的是,本发明实施例的图式并未以实际装置及元件的比例绘示。在图式中可能夸大实施例的形状与厚度以便清楚表现出本发明实施例的特征。此外,图式中的结构及装置以示意的方式绘示,以便清楚表现出本发明实施例的特征。

59.在本发明一些实施例中,相对性的用语例如“下”、“上”、“水平”、“垂直”、“之下”、“之上”、“顶部”、“底部”等等应被理解为该段以及相关图式中所绘示的方位。此相对性的用语仅是为了方便说明之用,其并不代表其所叙述的装置需以特定方位来制造或运作。而关于接合、连接的用语例如“连接”、“互连”等,除非特别定义,否则可指两个结构直接接触,或者亦可指两个结构并非直接接触,其中有其它结构设于此两个结构之间。且此关于接合、连接的用语亦可包括两个结构都可移动,或者两个结构都固定的情况。

60.本发明的实施例发明半导体装置的实施例,且上述实施例可被包含于例如微处理器、存储元件及/或其他元件的集成电路(integrated circuit,ic)中。上述集成电路也可包含不同的被动和主动微电子元件,例如薄膜电阻器(thin-film resistor)、其他类型电容器例如,金属-绝缘体-金属电容(metal-insulator-metal capacitor,mimcap)、电感、二极管、金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistors,mosfets)、互补式mos晶体管、双载子接面晶体管(bipolar junction transistors,bjts)、横向扩散型mos晶体管、高功率mos晶体管或其他类型的晶体管。在本领域技术人员可以了解也可将半导体装置使用于包含其他类型的半导体元件于集成电路之中。

61.图1显示根据本发明的一实施例所述的半导体装置的剖面图。如图1所示,半导体装置100包括半导体基板sub、第一阱w1、第二阱w2、场氧化层fox以及多晶硅层ply。半导体基板sub具有第一导电型。根据本发明的一实施例,半导体基板sub为硅基板。根据本发明的其他实施例,半导体基板sub亦可为具有第一导电型的轻掺杂的半导体基板。

62.第一阱w1形成于半导体基板sub中,且具有第二导电型。根据本发明的一实施例,第一导电型为p型,第二导电型为n型。根据本发明的一实施例,第一阱w1可借由离子注入步骤形成。例如,可于预定第一阱w1的区域注入磷离子或砷离子以形成第一阱w1。

63.第二阱w2形成于第一阱w1中,具有第一导电型。根据本发明的一实施例,第二阱w2可借由离子注入步骤形成。例如,可于预定形成第二阱w2的区域注入硼离子或铟离子以形成第二阱w2。在本实施例中,第二阱w2的掺杂浓度高于半导体基板sub的掺杂浓度。

64.场氧化层fox形成于第一阱w1以及第二阱w2的上方,多晶硅层ply形成于场氧化层

fox以及第二阱w2之上,且用以形成电阻元件r。根据本发明一实施例,电阻元件r形成于场氧化层fox以及第二阱w2之上。根据本发明的另一实施例,电阻元件r可形成于场氧化层fox、第一阱w1以及第二阱w2之上,其中电阻元件r两侧分布的宽度不超过第一阱w1的宽度。如图1所示,电阻元件r的分布宽度g,小于或等于第一阱w1的阱宽度h。

65.图2显示根据本发明的图1所述的多晶硅层的俯视图。如图2所示,电阻元件200为环形结构,包括焊垫pad、第一节点n1以及第二节点n2,其中图2的第一节点n1对应至图1的第一节点n1,图2的第二节点n2对应至图1的第二节点n2。如图1所示,第一节点n1以及焊垫pad耦接至高电压电平vh,第二节点n2耦接至低电压电平vl。根据本发明的一些实施例,低电压电平vl为相对于高电压电平vh的较低电压电平,因此低电压电平vl可为接地端gnd或是介于高电压电平vh以及接地端gnd之间的电压。

66.回到图1,半导体装置100更包括第三阱w3以及掺杂区d。第三阱w3形成于半导体基板sub之中,且具有第一导电型。根据本发明的一实施例,第三阱w3可借由离子注入步骤形成。例如,可于预定形成第三阱w3的区域注入硼离子或铟离子以形成第三阱w3。在本实施例中,第三阱w3的掺杂浓度高于半导体基板sub的掺杂浓度。

67.掺杂区d形成于第三阱w3之中,且具有第一导电型。根据本发明的一实施例,掺杂区d的掺杂浓度高于第三阱w3的掺杂浓度。如图1所示,掺杂区d耦接至接地端gnd。

68.如图1所示,半导体装置100更包括第一顶掺杂层top1以及第二顶掺杂层top2。第一顶掺杂层top1形成于第一阱中w1且具有第一导电型,第二顶掺杂层top2形成于第一阱w1中且具有第一导电型,其中第一顶掺杂层top1以及第二顶掺杂层top2位于第二阱w2的两侧,且分别与第二阱w2相互分离。根据本发明的一实施例,第一顶掺杂层top1以及第二顶掺杂层top2的掺杂浓度低于第二阱w2的掺杂浓度。

69.根据本发明的一实施例,由于第二阱w2以及第一阱w1形成第一寄生二极管dp1,第一阱w1以及半导体基板sub形成第二寄生二极管dp2,使得高电压电平vh至接地端gnd的跨压由场氧化层fox、第一寄生二极管dp1以及第二寄生二极管dp2共同分担,进而提高半导体装置100的电阻元件r的耐压程度。根据本发明的一实施例,第一顶掺杂层top1以及第二顶掺杂层top2用以增加半导体装置100的横向电场的承受能力。

70.图3显示根据本发明的另一实施例所述的半导体装置的剖面图。如图3所示,半导体装置300包括半导体基板sub、第一阱w1、第二阱w2、第一掺杂区d1、场氧化层fox以及多晶硅层ply。半导体基板sub具有第一导电型。根据本发明的一实施例,半导体基板sub为硅基板。根据本发明的其他实施例,半导体基板sub亦可为具有第一导电型的轻掺杂的半导体基板。

71.第一阱w1形成于半导体基板sub中,且具有第二导电型。根据本发明的一实施例,第一导电型为p型,第二导电型为n型。根据本发明的一实施例,第一阱w1可借由离子注入步骤形成。例如,可于预定第一阱w1的区域注入磷离子或砷离子以形成第一阱w1。

72.第二阱w2形成于第一阱w1中,具有第二导电型。根据本发明的一实施例,第二阱w2可借由离子注入步骤形成。例如,可于预定第一阱w1的区域注入磷离子或砷离子以形成第二阱w2。在本实施例中,第二阱w2的掺杂浓度高于第一阱w1的掺杂浓度。

73.第一掺杂区d1形成于第二阱w2之中,且具有第二导电型。根据本发明的一实施例,第一掺杂区d1可借由离子注入步骤形成。例如,可于预定第一掺杂区d1的区域注入磷离子

或砷离子以形成第一掺杂区d1。在本实施例中,第一掺杂区d1的掺杂浓度高于第二阱w2的掺杂浓度。

74.场氧化层fox形成于上述第一阱w1以及上述第二阱w2的上方,且环绕第一掺杂区d1,多晶硅层ply形成于场氧化层fox之上且用以形成电阻元件r。

75.图4显示根据本发明的图3所述的多晶硅层的俯视图。如图4所示,电阻元件400为环形结构,包括第一节点n1以及第二节点n2,其中图4的第一节点n1对应至图3的第一节点n1,图4的第二节点n2对应至图3的第二节点n2。如图4所示,第一掺杂区d1位于电阻元件400的中央位置。将图4的电阻元件400与图2的电阻元件200相比,图4的第一掺杂区d1位于图2的焊垫pad的位置。如图3所示,电阻元件r的第一节点n1以及第一掺杂区d1耦接至高电压电平vh,电阻元件r的第二节点n2耦接至低电压电平vl。

76.回到图3,半导体装置300更包括第三阱w3以及第二掺杂区d2。第三阱w3形成于半导体基板sub之中,且具有第一导电型。根据本发明的一实施例,第三阱w3可借由离子注入步骤形成。例如,可于预定形成第三阱w3的区域注入硼离子或铟离子以形成第三阱w3。在本实施例中,第三阱w3的掺杂浓度高于半导体基板sub的掺杂浓度。

77.第二掺杂区d2形成于第三阱w3之中,且具有第一导电型。根据本发明的一实施例,第二掺杂区d2的掺杂浓度高于第三阱w3的掺杂浓度。如图3所示,第二掺杂区d2耦接至接地端gnd。

78.如图3所示,半导体装置300更包括第一顶掺杂层top1以及第二顶掺杂层top2。第一顶掺杂层top1形成于第一阱中w1且具有第一导电型,第二顶掺杂层top2形成于第一阱w1中且具有第一导电型,其中第一顶掺杂层top1以及第二顶掺杂层top2位于第二阱w2的两侧,且分别与第二阱w2相互分离。根据本发明的一实施例,第一顶掺杂层top1以及第二顶掺杂层top2的掺杂浓度低于第三阱w3的掺杂浓度,且高于半导体基板sub的掺杂浓度。

79.如图3所示,电阻元件r于场氧化层fox上分布的宽度为第一宽度x1,第一顶掺杂区top1或第二掺杂区top2的宽度为第二宽度x2,第二宽度x2为不小于第一宽度x1。

80.根据本发明的一实施例,高电压电平至接地端gnd的跨压,由场氧化层fox、第一顶掺杂区top1(或第二顶掺杂区top2)、第一阱w1以及半导体基板sub共同承担,进而提高半导体装置500的耐压程度。根据本发明的一实施例,由于第一阱w1以及半导体基板sub之间形成第三寄生二极管dp3,第三寄生二极管dp3提供耦接至高电压电平vh第一节点n1一个静电电荷的排除路径。

81.换句话说,当电阻元件r的第一节点n1遭受到静电放电时,由于第一节点n1耦接至第一掺杂区d1,静电电荷将通过第一阱w1以及半导体基板sub所形成的第三寄生二极管dp3,而将静电电荷经第二掺杂区d2放电至接地端gnd。根据本发明的一实施例,第一顶掺杂层top1以及第二顶掺杂层top2不仅用以增加半导体装置300的垂直电场的承受能力,更用以增加半导体装置300的横向电场的承受能力。

82.图5显示根据本发明的另一实施例所述的半导体装置的剖面图。将图5的半导体装置500与图3的半导体装置300相比,半导体装置500更包括第三掺杂区d3。

83.第三掺杂区d3形成于第三阱w3之中,且位于第一掺杂区d1以及第二掺杂区d2之间而与第二掺杂区d2相邻,并具有第二导电型。根据本发明的一实施例,第三掺杂区d3可借由离子注入步骤形成。例如,可于预定第三掺杂区d3的区域注入磷离子或砷离子以形成第三

掺杂区d3。在本实施例中,第三掺杂区d3的掺杂浓度高于第二阱w2的掺杂浓度。如图5所示,第三掺杂区d3更耦接至接地端gnd。

84.根据本发明的一实施例,高电压电平至接地端gnd的跨压,由场氧化层fox、第一顶掺杂区top1(或第二顶掺杂区top2)、第一阱w1以及半导体基板sub共同承担,进而提高半导体装置500的耐压程度。根据本发明的一实施例,由于第一掺杂区d1、第二掺杂区d2以及第三掺杂区d3形成寄生双极性晶体管npn且第一节点n1耦接至第一掺杂区d1,当电阻元件r的第一节点n1遭受到静电放电时,寄生双极性晶体管npn随即导通而将静电电荷快速排放至接地端gnd。根据本发明的一实施例,第一顶掺杂层top1以及第二顶掺杂层top2不仅用以增加半导体装置500的垂直电场的承受能力,更用以增加半导体装置500的横向电场的承受能力。

85.图6显示根据本发明的另一实施例所述的半导体装置的剖面图。将图6的半导体装置600与图3的半导体装置300相比,半导体装置600更包括第四掺杂区d4以及第五掺杂区d5。

86.第四掺杂区d4形成于第二阱w2,与第一掺杂区d1相邻且具有第一导电型。根据本发明的一实施例,第四掺杂区d4可借由离子注入步骤形成。例如,可于预定形成第四掺杂区d4的区域注入硼离子或铟离子以形成第四掺杂区d4。

87.第五掺杂区d5形成于半导体基板sub之中且具有第二导电型。根据本发明的一实施例,第五掺杂区d5可借由离子注入步骤形成。例如,可于预定形成第五掺杂区d5的区域注入硼离子或铟离子以形成第五掺杂区d5。如图6所示,第五掺杂区d5耦接至接地端gnd,且与第三阱w3相互分离。

88.据本发明的一实施例,由于第一掺杂区d1、第四掺杂区d4、第二掺杂区d2以及第五掺杂区d5形成寄生的硅控整流器(silicon controlled rectifier,scr)且第一节点n1与第一掺杂区d1以及第四掺杂区耦接在一起,当电阻元件r的第一节点n1遭受到静电放电时,寄生的硅控整流器随即导通而将第一节点n1接收的静电电荷排放至接地端gnd。

89.本发明提出的半导体装置,除了能够增加电阻元件的耐压程度,更能够提供排除静电电荷的路径,使得多晶硅电阻除了满足高压应用的需求外,更能在多晶硅电阻的一端提供静电放电保护,提供所需的保护功能。

90.虽然本发明的实施例及其优点所述如上,但应该了解的是,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作更动、替代与润饰。此外,本发明的保护范围并未局限于说明书内所述特定实施例中的工艺、机器、制造、物质组成、装置、方法及步骤,任何本领域技术人员可从本发明一些实施例的揭示内容中理解现行或未来所发展出的工艺、机器、制造、物质组成、装置、方法及步骤,只要可以在此处所述实施例中实施大抵相同功能或获得大抵相同结果皆可根据本发明一些实施例使用。因此,本发明的保护范围包括上述工艺、机器、制造、物质组成、装置、方法及步骤。另外,每一权利要求范围构成个别的实施例,且本发明的保护范围也包括各个申请专利范围及实施例的组合。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。