技术特征:

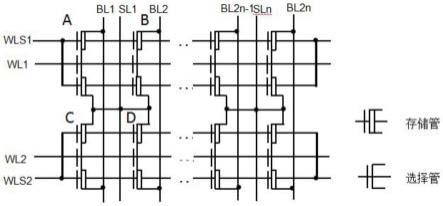

1.一种分栅存储器阵列结构,其特征在于,包括:多个结构相同的存储单元,以在x方向和y方向上分布形成置于阱中的存储阵列,而各所述存储单元均包括以分栅结构形成的一选择管和对称分布在该选择管两侧的两个存储管,且各所述存储单元中的两个存储管的栅极均互联,以使各所述存储单元均作为一个存储位;其中,在所述存储阵列中的y方向上,每相邻的两列中的存储单元采用共源连接,以使该左右相邻的两列中的所有存储单元以共享源极的方式共用一条源线sln,且在所述存储阵列中的每一列,其同一列中的多个存储单元的漏极均与对应列的y方向的位线bln连接;而在所述存储阵列中的x方向上,每一行中的多个存储单元中的两个存储管均与其相邻的存储单元中的同一行位置上的存储管的栅极相连,并且在每一行中位于首和尾的两个存储单元中的各两个存储管的栅极分别连在一起,以接出作为一条存储栅字线wlsn,以及同一行中的多个存储单元中的选择管的栅极均相连,以接出作为一条选择栅字线wln。2.如权利要求1所述的分栅存储器阵列结构,其特征在于,在所述存储阵列的y方向上,其每一列中的每相邻两个存储单元的源极短接。3.如权利要求1所述的分栅存储器阵列结构,其特征在于,所述存储单元中的分栅结构形成的选择管和存储管共享一个沟道,以省去位于中间的选择管的源极、漏极以及其分别对应的往外引出的接触孔。4.如权利要求1所述的分栅存储器阵列结构,其特征在于,所述存储管为sonos存储管。5.如权利要求3所述的分栅存储器阵列结构,其特征在于,所述选择管为包含堆叠的栅氧化层和多晶硅栅极层的mos管器件。6.一种基于权利要求1~5任一所述的分栅存储器阵列结构的操作方法,其特征在于,所述存储阵列在进行数据的读取、擦除以及写入时采用行操作方式,即同一行所包含的存储单元同时进行数据擦除、读取和写入。7.如权利要求6所述的分栅存储器阵列结构的操作方法,其特征在于,在对存储阵列进行数据的擦除、编程或者读出时,对阱分别施加对应的不同的电压值。8.如权利要求7所述的分栅存储器阵列结构的操作方法,其特征在于,对所述存储阵列在进行数据擦除时,给选中的目标存储单元所在的行所对应的存储栅字线wlsn施加负电压vneg,而给所述存储阵列中的本次非选中的存储单元所在的行的存储栅字线wlsn均施加正电压vpos,并将所述存储阵列中所有选择栅字线wln接地,将所述存储阵列中的所有存储单元的漏极所连接的位线bln以及其源极所连接的源线sln均设置为浮空状态。9.如权利要求8所述的分栅存储器阵列结构的操作方法,其特征在于,对所述存储阵列在进行数据写入时,每左右共源相邻的两列中的靠近共源线sln的各存储单元中的存储管始终保持数据“0”状态,而远离共源线sln的各存储单元中的另一存储管可写数据“1”或数据“0”。10.如权利要求9所述的分栅存储器阵列结构的操作方法,其特征在于,对所述存储阵列在进行数据写入时,给选中的目标存储单元所在的行所对应的存储栅字线wlsn施加正电压vpos、其所对应的共源线sln施加正电压vp0,所述存储阵列中的本次非选中的存储单元所在的行的存储栅字线wlsn均施加负电压vneg,所述存储阵列中的所有选择栅字线wln均施加负电压vneg;并在对所述选中的目标存储单元中的远离共源线sln的存储管写入数据

“

1”时,给该目标存储单元的漏极所连接的位线bln施加负电压vneg,或者,在对所述选中的目标存储单元中的远离共源线sln的存储管写入数据“0”时,给该目标存储单元的漏极所连接的位线bln施加正电压所述vp0。11.如权利要求10所述的分栅存储器阵列结构的操作方法,其特征在于,对所述存储阵列在进行数据读取时,给选中的目标存储单元的漏极所连接的位线bln施加正电压vlim,给该选中的目标存储单元所在行的选择栅字线wln施加大于器件开启电压的正电压vpwr,并将该目标存储单元的其余端均接地,以通过读取所述选中的目标存储单元的漏极所连接的位线bln的电流即可获得所述选中的存储单元中所存储的数据的状态。12.如权利要求11所述的分栅存储器阵列结构的操作方法,其特征在于,当对所述选中的目标存储单元进行擦除操作时,对阱施加的电压为正电压vpos;当对所述选中的目标存储单元进行写入操作时,对阱施加的电压为负电压vneg;当对所述选中的目标存储单元进行读取操作时,将阱直接接地vgnd。13.如权利要求12所述的分栅存储器阵列结构的操作方法,其特征在于,所述vneg<vgnd<vlim<vp0<vpos,其中vgnd=0v。14.如权利要求13所述的分栅存储器阵列结构的操作方法,其特征在于,所述vneg=-4v,所述vlim=0.8v,所述vp0=1.6v,所述vpwr=2v,所述vpos=7v。

技术总结

本发明提供了一种分栅存储器阵列及其操作方法,应用于半导体技术领域。其包括多个结构相同的存储单元,以在X方向和Y方向上分布形成置于阱中的存储阵列,而各所述存储单元均包括以分栅结构形成的一选择管和对称分布在该选择管两侧的两个存储管,且各所述存储单元中的两个存储管的栅极均互联,以使各所述存储单元均作为一个存储位。由于在本发明提供的存储阵列中,每左右相邻的两列存储单元均采用共源连接,即相邻两列中的所有存储单元以共享源极的方式共用一条源线SL,从而使得存储单元的结构更加紧凑,整个存储阵列简化,并且比每个存储单元设置一条SL、一条BL的结构更加节省面积,进而有效缩减了存储单元的面积,对存储单元的操作也更加简化。元的操作也更加简化。元的操作也更加简化。

技术研发人员:王宁 张可钢

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:2022.08.30

技术公布日:2022/11/18

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。