1.本发明属于网络芯片仿真技术领域,尤其涉及芯片仿真过程中监测数据流量的方法及系统。

背景技术:

2.eda仿真中,针对网络芯片进行速率、带宽等验证时,无论是模块级别、子系统级别或者系统级别,还是对于某条流的速率或者某个粒度下多条流的带宽分配的验证,目前并没有一个通用的工具来支持这些必要的测量。

3.而如果只进行逻辑检查,则不能从宏观上证明网络芯片速率或者带宽的正确性。

4.在实际芯片测试(与eda仿真相对)时,利用网络分析仪器协助测量,可以比较直观地观测速率的实时状态,从而对调试和测试中出现的问题及其定位有很好的支持。但是eda仿真中,没有比较直观的速率及流量的可视化窗口。

技术实现要素:

5.有鉴于此,本发明提供芯片仿真过程中监测数据流量的方法及系统,以在芯片仿真过程中可视化地监测各端口的数据流量、监测端口的多条流之间的带宽分配比例。

6.第一方面,本技术提供一种芯片仿真过程中监测数据流量的方法,包括:

7.监测仿真芯片的端口以第一传输方式传输的数据;

8.使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数;

9.将所述字节数根据一配置信息生成所述端口的数据流量,所述配置信息包括数据流量的计算方式;

10.以可视化方式展示所述端口的数据流量。

11.进一步地,所述配置信息包括配置的时间窗、配置的所述计算方式为以比特位为单位计算所述数据流量;

12.所述将所述字节数根据一配置信息生成所述端口的数据流量,包括:根据所述时间窗对应的字节数,计算单位时间的字节数作为所述的数据流量。

13.进一步地,所述配置信息包括配置的时间窗、配置的单位包所包含的字节数,配置的所述计算方式为以包为单位计算所述数据流量;

14.所述将所述字节数根据一配置信息生成所述端口的数据流量,包括:根据所述时间窗对应的字节数计算所述时间窗对应的包数,据此计算单位时间的包数作为所述数据流量。

15.进一步地,还包括:

16.监测仿真芯片的端口以第一传输方式传输的数据所包含的流标签;

17.统计各流标签对应的所述数据包含的字节数;

18.分别将各流标签对应的字节数根据一配置信息生成所述端口的各流标签对应的数据流量,所述配置信息包括数据流量的计算方式;

19.以可视化方式展示所述端口的各流标签的数据流量。

20.进一步地,还包括:

21.根据预先配置的数据流量的检查指标,对所述数据流量进行质量检查。

22.进一步地,所述检查指标包括至少以下之一:位速率预期值、位速率预期公差、包速率预期值、包速率预期公差、各流标签对应的预期速率值、各流标签对应的预期速率公差、各流标签对应的预期比例值、各流标签对应的预期比例公差。

23.第二方面,本技术提供一种芯片仿真过程中监测数据流量的装置,包括:

24.监测及统计单元,用于监测仿真芯片的端口以第一传输方式传输的数据;使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数;

25.数据流量计算单元,用于将所述字节数根据一配置信息生成所述端口的数据流量,所述配置信息包括数据流量的计算方式;

26.可视化单元,用于以可视化方式展示所述端口的数据流量。

27.进一步地,所述监测及统计单元还用于监测仿真芯片的端口以第一传输方式传输的数据所包含的流标签;统计各流标签对应的所述数据包含的字节数;

28.所述数据流量计算单元还用于分别将各流标签对应的字节数根据一配置信息生成所述端口的各流标签对应的数据流量,所述配置信息包括数据流量的计算方式;

29.所述可视化单元还用于以可视化方式展示所述端口的各流标签的数据流量。

30.第三方面,本技术提供一种芯片仿真过程中监测数据流量的系统,包括:

31.至少一个适配器,与至少一个仿真芯片的至少一个端口对应地连接;

32.与所述至少一个适配器对应地连接的至少一个流量监测器;

33.与所述至少一个流量监测器连接的可视化设备;

34.其中,各所述适配器被配置为监测各所述仿真芯片的端口以第一传输方式传输的数据,使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数;

35.各流量监测器被配置为将所述字节数根据一配置信息生成所述端口的数据流量,所述配置信息包括数据流量的计算方式;

36.可视化设备被配置为用于以可视化方式展示各所述端口的数据流量。

37.第四方面,本技术提供一种计算设备,包括:处理器,以及存储器,其上存储有程序指令,程序指令当被处理器执行时使得处理器执行如第一方面说明的芯片仿真过程中监测数据流量的方法。

38.本技术的这些和其它方面在以下(多个)实施例的描述中会更加简明易懂。

附图说明

39.下面参照附图来进一步说明本技术的各个技术特征和它们之间的关系。附图为示例性的,一些技术特征并不以实际比例示出,并且一些附图中可能省略了本技术所属技术领域中惯用的且对于理解和实现本技术并非必不可少的技术特征,或是额外示出了对于理解和实现本技术并非必不可少的技术特征,也就是说,附图所示的各个技术特征的组合并不用于限制本技术。另外,在本技术全文中,相同的附图标记所指代的内容也是相同的。具体的附图说明如下:

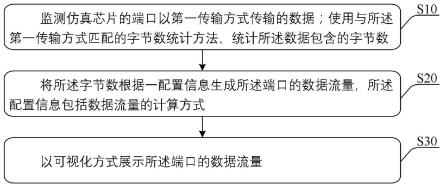

40.图1是本发明实施例的芯片仿真过程中监测数据流量的方法的流程示意图;

41.图2是本发明实施例的芯片仿真过程中监测数据流量的装置的一个组成示意图;

42.图3a是本发明实施例的芯片仿真过程中监测数据流量的系统的一个组成示意图;

43.图3b是本发明实施例的芯片仿真过程中监测数据流量的系统的另一个组成示意图;

44.图4a是本发明实施例生成的多流模式下的数据流量及带宽分配比例值的日志文件的内容示例;

45.图4b是本发明实施例生成的单流模式下的包速率的日志文件的内容示例;

46.图4c是本发明实施例生成的单流模式下的位速率的日志文件的内容示例;

47.图5是本发明实施例生成的单流模式下的位速率在verdi中的展示示例;

48.图6是本发明实施例的计算设备的组成示意图。

具体实施方式

49.下面,参照附图对本发明的具体实施方式进行详细的说明。

50.除非另有定义,本技术全文所使用的所有技术和科学术语与本技术所属技术领域的技术人员通常理解的含义相同。如有不一致,以本技术全文中所说明的含义或者根据本技术全文中记载的内容得出的含义为准。另外,本说明中所使用的术语只是为了描述本发明实施例的目的,不是旨在限制本技术。

51.为了准确地对本技术中的技术内容进行叙述,以及为了准确地理解本技术,在对具体实施方式进行说明之前先对本说明书中所使用的术语给出如下的解释说明或定义。

52.电子设计自动化(electronic design automation,eda)是指利用计算机辅助设计软件,来完成超大规模集成电路(very large scale integration circuit,vlsi)芯片的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

53.目前eda软件(如quartusii8.0、cadence、synopsys、mentor)作为半导体或数字电路芯片研发的底层基础技术平台,在设计环节,可以将芯片涉及的复杂物理问题用数学模型高度精确化表述,在虚拟环境中仿真出芯片预期的控制逻辑。在验证环节,可以实现逻辑功能一致性,也即,在验证环节运行与设计环节一致的控制逻辑。verdi使用情形包括ic验证工程师进行debug或ic设计工程师进行review。

54.网络芯片通常作为源节点或目标节点,与网络中的其他节点传输数据,如设置在路由器(router)中的网络芯片、设置在交换机(switch)中的网络芯片。

55.在计算机网络、互联网数据中心(internet data center,idc)机房中,网络数据传输的速率通常用位速率,单位为比特每秒(bits per second,bps或b/s)。在网络数据传输应用中,宽带速率的单位通常为字节每秒(bytes per second,bps或b/s)。利用1字节=8比特或1byte=8bit,可以换算得到相应场景下使用的速率。如1m带宽,是1mbps或1000kbps或1000/8kbps或125kbps。

56.包速率用于指示在应用层意义上的包转发性能,即网络设备在单位时间内能够处理多少个“包”。单位时间内能够处理的“包”越多,网络设备的转发能力就越强。包速率的单位为包每秒(packet per second,pps或p/s)。

57.根据前述的包速率或位速率,可以确定线速。线速通常与包速率或位速率具有相

似的变化趋势。线速可以用于指示网络设备的交换转发能力,如,交换机或路由器与数据总线间所能吞吐的最大数据量。

58.autbus是一种基于时间敏感(time sensitive,ts)技术的新型宽带工业总线。autbus采用两线非桥接媒介,总线数据带宽达到100mbps,最大传输距离500米,最小循环周期8微秒us,最大节点数256个。

59.双倍速率同步动态随机存储器(double data rate sdram,ddr)的频率可以用工作频率和等效频率两种方式表示,工作频率是内存颗粒实际的工作频率。由于ddr内存可以在脉冲的上升沿和下降沿都传输数据,因此传输数据的等效频率是工作频率的两倍,其传输速度可达667mhz,耗电量更低,散热性能更优良。

60.固态硬盘或固态驱动器(solid state disk,solid state drive,ssd)普遍采用sata-2接口、sata-3接口、sas接口、msata接口、pcie接口、m.2接口、cfast接口、sff-8639接口或nvme/ahci协议。其中,pci express总线是较旧的pci/pci-x总线的高速串行替换。

61.系统时间,通常指真实时间或者cpu时间。仿真时间则是指对芯片的时钟clk计数得到的相对时间。

62.单流模式:仿真芯片的端口传输的数据中不包含流标签,或全部的数据都具有相同的流标签。

63.多流模式;仿真芯片的端口传输的数据中包含多个流标签,各流标签用于标识不同来源的数据、不同含义的数据或不同传输优先级的数据。

64.下面先对现有技术中的方法进行介绍,然后再对本技术的技术方案进行详细介绍。

65.数字电路实现的网络芯片通常设置多个逻辑单元、多个模块、至少一个子系统或至少一个系统。对于模块级、子系统级或者系统级的速率、性能指标、带宽分配调度等进行eda验证,可以概括为微观验证和宏观验证两个方面。微观验证是指实现的代码逻辑或者算法公式映射到代码逻辑的正确性,但是对于这个公式或者说此类实现有没有达到最终的设计的速率、性能指标、及调度带宽分配的是否存在问题,则不能证明其正确性。而为了证明其宏观上的正确性,需要进行宏观验证。宏观验证可以证明此类代码实现可以满足速率、性能指标、及可以满足调度的公平带宽分配等问题。

66.在实际芯片测试(与eda仿真相对)时,利用网络分析仪器协助测量,可以比较直观地观测速率的实时状态,从而对调试和测试中出现的问题及其定位有很好的支持。但是eda仿真中,没有比较直观的速率或流量的可视化窗口。

67.本技术的技术方案包括芯片仿真过程中监测数据流量的方法、装置、系统及计算机设备,实现了在芯片仿真过程中针对仿真芯片的端口进行通用且标准的流量测量及自动检查,可以监测芯片各端口上的数据流量或监测多条流之间的带宽分配。在调试过程中,还可以进行可视化调试。

68.如图1所示,本发明实施例的芯片仿真过程中监测数据流量的方法,包括以下步骤:

69.s10:监测仿真芯片的端口以第一传输方式传输的数据;

70.使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数;

71.s20:将所述字节数根据一配置信息生成所述端口的数据流量,所述配置信息包括

数据流量的计算方式;

72.s30:以可视化方式展示所述端口的数据流量。

73.以上,监测仿真芯片的端口以第一传输方式传输的数据,并使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数;将所述字节数根据一配置信息生成所述端口的数据流量,所述配置信息包括数据流量的计算方式,以可视化方式展示所述端口的数据流量。如此,使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数,配置灵活、通用性强,可以适配不同传输协议的端口。

74.以上,将所述字节数根据一配置信息生成所述端口的数据流量,所述配置信息包括数据流量的计算方式,如此,可以采用不同计算方式得到不同含义的数据流量,配置灵活、通用性强,可以实现不同的传输协议所适合的数据流量计算方法。

75.以上,以可视化方式展示端口的数据流量,如此,不同内容的数据流量的可视化方式可配置、可自定义,配置灵活、通用性强,可以实现不同的传输协议所适合的数据流量可视化方法。

76.综上,该实施例的芯片仿真过程中监测数据流量的方法,可以适配不同仿真芯片的不同端口的传输协议,可以在芯片仿真过程中可视化地监测不同仿真芯片的不同端口的不同含义的数据流量,进行通用的标准测量,配置灵活、适应性强,通用性好。

77.如此,在芯片仿真过程中,可以直观、实时地监测仿真芯片的端口传输的数据流量,进而有利于通过实时观测数据流量的状态,对调试和测试中出现的问题及问题定位提供良好的支持。

78.在一些实施例中,步骤s10中,所述监测仿真芯片的端口以第一传输方式传输的数据,可以是获取仿真芯片的端口以第一传输方式传输数据时信号线上传输的脉冲序列;相应地,使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数,包括:根据以第一传输方式传输数据时信号线上传输的脉冲序列的数据量特征,如,该数据量特征可以是时序模式、脉冲的上升沿使能或下降沿使能等与所述第一传输方式相关联的高低电平特征,以设定的统计窗口(如第二周期)为间隔,连续地统计在各统计窗口内以第一传输方式传输的数据包含的字节数。

79.以上,与仿真芯片的端口以第一传输方式传输数据相对应,统计在各统计窗口内以第一传输方式传输的数据包含的字节数。如此,该监测及统步骤可以监测仿真芯片的端口传输数据时的第一传输方式(如各种传输协议),使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数,配置灵活、通用性强,可以适配不同传输协议的端口。

80.在一些实施例中,以上步骤s10中,所述仿真芯片的端口向其他仿真芯片传输数据(为源(source)端口),或从其他仿真芯片接收数据(为目的(destination)端口)。仿真芯片的端口可以是数据总线(bus)端口,如autbus、pci express总线,可以是以太网的同轴双绞线端口等,不再赘述。

81.通常,芯片的端口经信号线与其他芯片连接,在传输数据时,信号线上承载符合传输协议的高电平信号或低电平信号,这些依次生成的高电平信号或低电平信号形成脉冲序列。在端口被以指定的包长或通过不同的传输方式传输数据时,在指定的统计窗口内,经端口传输的字节数各不相同。如,ddr可以在脉冲的上升沿或下降沿传输数据,也可以在脉冲

的上升沿和下降分别传输数据,如此,在指定的统计窗口内,经ddr的端口传输的字节数后者是前者是两倍。

82.在一些实施例中,基于时间轴,可以将时间窗(如第一周期)切片,得到多个时间片(如,统计窗口,也即第二周期)。

83.在一些实施例中,所述配置信息包括配置的时间窗、配置的所述计算方式为以比特位为单位计算所述数据流量;所述将所述字节数根据一配置信息生成所述端口的数据流量,包括:根据所述时间窗对应的字节数,计算单位时间的字节数作为所述的数据流量。

84.在一些实施例中,所述配置信息包括配置的时间窗(如第一周期)、配置的所述计算方式为以比特位为单位计算所述数据流量。相应地,计算数据流量,包括:获取统计的所述数据包含的字节数,参考前述说明,所述数据包含的字节数以第二周期为间隔地统计得到,其中,第二周期小于第一周期,如第一周期为第二周期的正整数倍;将所述时间窗对应的多个所述数据包含的字节数累加求和,得到该时间窗对应的字节数。根据预先配置的前述芯片的主频,采用下述公式计算单位时间的字节位数作为位速率:

85.bps=bytes*8*frequency/时钟周期数。

86.上式中,bps为位速率,bytes为收集到的在配置的时间窗内该端口传输的字节数;frequency为前述芯片的主频,前述芯片的主频的倒数为时钟周期(clock或clk),则时钟周期数可以根据配置的时间窗(如第一周期)中包括的时钟周期的数量确定。通常,所述时钟周期小于第二周期。

87.如此,可以根据配置信息,方便快速地生成单流模式下仿真芯片的端口以第一传输方式传输的数据对应的位速率。

88.在一些实施例中,所述配置信息包括配置的时间窗、配置的单位包所包含的字节数,配置的所述计算方式为以包为单位计算所述数据流量。所述将所述字节数根据一配置信息生成所述端口的数据流量,包括:根据所述时间窗对应的字节数计算所述时间窗对应的包数,据此计算单位时间的包数作为所述数据流量。

89.在一些实施例中,所述配置信息包括配置的时间窗(如第一周期)、配置的单位包所包含的字节数(如下述的预设包长),配置的所述计算方式为以包为单位计算所述数据流量。相应地,计算数据流量,包括:获取统计的所述数据包含的字节数,参考前述说明,所述数据包含的字节数以第二周期为间隔地统计得到,其中,第二周期小于第一周期,如第一周期为第二周期的正整数倍;将所述时间窗对应的多个所述数据包含的字节数累加求和,得到该时间窗对应的字节数。根据预先配置的前述芯片的主频,采用下述公式以包为单位计算包速率:

90.pps=bytes*8*frequency/时钟周期数/预设包长。

91.上式中,pps为包速率,bytes为收集到的在配置的时间窗内该端口传输的字节数;frequency为前述芯片的主频,前述芯片的主频的倒数为时钟周期(clock或clk),则时钟周期数可以根据配置的时间窗(如第一周期)中包括的时钟周期的数量确定。通常,所述时钟周期小于第二周期。这里,预设包长可以是根据预先配置的最大包长和最小包长计算得到,也可以是预先配置的平均包长。

92.如此,可以根据配置信息,方便快速地单流模式下生成仿真芯片的端口以第一传输方式传输的数据对应的包速率。

93.在一些实施例中,以上步骤s30中,以可视化方式展示所述端口的数据流量,包括:将在各时间窗内分别计算得到的所述包速率或位速率发送至可视化单元verdi或dve或文本式可视化单元,以使得可视化单元verdi或dve或文本式可视化单元可视化地展示实时流量监测页面,如,图5展示了某端口对应的位速率的走势图,其中,位速率(gbps)以第一周期为时间间隔更新。

94.如此,不同内容的数据流量的可视化方式可配置、可自定义,配置灵活、通用性强,可以实现单流模式下不同的传输协议所适合的数据流量可视化方法。

95.在一些实施例中,监测仿真芯片的端口以第一传输方式传输的数据所包含的流标签;统计各流标签对应的所述数据包含的字节数;分别将各流标签对应的字节数根据一配置信息生成所述端口的各流标签对应的数据流量,所述配置信息包括数据流量的计算方式;以可视化方式展示所述端口的各流标签的数据流量。

96.以上,监测仿真芯片的端口以第一传输方式传输的数据所包含的流标签;统计各流标签对应的所述数据包含的字节数;分别将各流标签对应的字节数根据一配置信息生成所述端口的各流标签对应的数据流量,所述配置信息包括数据流量的计算方式;以可视化方式展示所述端口的各流标签的数据流量。如此,使用与所述第一传输方式匹配的字节数统计方法,分别统计多流模式下各流标签对应的所述数据包含的字节数,配置灵活、通用性强,可以适配不同传输协议的端口。可以采用不同计算方式得到各流标签对应的不同含义的数据流量,配置灵活、通用性强,可以实现不同的传输协议所适合的数据流量计算方法,可以实现不同的传输协议所适合的数据流量可视化方法。

97.在一些实施例中,仿真芯片的端口以第一传输方式传输的数据中包含多个流标签。如根据通过该端口传输的数据可以是音频数据、视频数据或电话数据(如语音通话),根据这三类数据分别对应的优先级可以将该多流模式下数据的流标签依次配置为:第一优先级的电话数据对应流标签flow_id_1、第二优先级的音频数据对应流标签flow_id_2、第三优先级的视频数据对应流标签flow_id_3。

98.通常,端口传输的数据为多流模式,并基于任意自定义的流特征来配置流标签。如,流特征可以是报文中的某个字段的值,如监测端口传输的交易请求数据中,交易发起用户为“王二”的数据中包括的字节数时,可以定义流特征为“王二”。如,流特征可以是某些数字,如监测端口传输的学生学籍数据中,学生入学年为“2022”的数据中包括的字节数或学生入学年为“2020”的数据中包括的字节数时,可以定义流特征为“2022”或“2020”。相应地,如在1s内该端口传输了1mbit的数据,其中,针对年份“2022”这个流特征,收集到20k字节,而针对年份“2020”这个流特征,收集到30k字节。

99.在一些实施例中,统计各流标签对应的所述数据包含的字节数,包括:

100.根据获取的多个流标签(如flow_id_list中记载的各flow_id),为所述数据包含的字节数分别关联所述多个流标签中的一个。如,以前述的第二周期,连续地统计各流标签分别对应的所述数据包含的字节数。

101.在一些实施例中,分别将各流标签对应的字节数根据一配置信息生成所述端口的各流标签对应的数据流量,所述配置信息包括数据流量的计算方式,具体包括:

102.所述配置信息还包括配置的时间窗、配置的所述计算方式为以比特位为单位计算所述数据流量;别将各流标签对应的至少一个字节数处理为所述时间窗对应的字节数,分

别计算单位时间的字节数作为各流标签对应的位速率。

103.如此,可以根据配置信息,方便快速地生成多流模式下仿真芯片的端口以第一传输方式传输的数据时,各流标签分别对应的位速率,不再赘述。

104.在一些实施例中,分别将各流标签对应的字节数根据一配置信息生成所述端口的各流标签对应的数据流量,所述配置信息包括数据流量的计算方式,具体包括:

105.所述配置信息还包括配置的时间窗、配置的单位包所包含的字节数,配置的所述计算方式为以包为单位计算所述数据流量;分别将各流标签对应的至少一个字节数处理为所述时间窗对应的字节数,分别计算所述时间窗对应的包数,据此计算单位时间的包数作为各流标签对应的包速率。

106.如此,可以根据配置信息,方便快速地生成多流模式下仿真芯片的端口以第一传输方式传输的数据时,各流标签分别对应的包速率,不再赘述。

107.在一些实施例中,以可视化方式展示所述端口的各流标签的数据流量,包括:

108.将在各时间窗内分别计算得到的各流标签对应的所述包速率或位速率发送至可视化单元verdi或dve或文本式可视化单元,以使得可视化单元verdi或dve或文本式可视化单元可视化地展示实时流量监测页面。

109.如此,不同内容的数据流量的可视化方式可配置、可自定义,配置灵活、通用性强,可以实现多流模式下不同的传输协议所适合的数据流量可视化方法。

110.在一些实施例中,根据预先配置的数据流量的检查指标,对所述数据流量进行质量检查,如线速是否满足要求,如多流模式下各个流标签对应的带宽分配比例是否满足要求。通常,所述检查指标包括至少以下之一:位速率预期值、位速率预期公差、包速率预期值、包速率预期公差、各流标签对应的预期速率值、各流标签对应的预期速率公差、各流标签对应的预期比例值、各流标签对应的预期比例公差。

111.在一些实施例中,根据预先配置的位速率检查指标,对所述数据流量进行质量检查,包括:

112.所述位速率检查指标包括位速率预期值、位速率预期公差;

113.生成所述仿真芯片的端口以第一传输方式传输数据时的位速率;

114.获取预先配置的所述位速率预期值及预先配置的所述位速率公差(如百分数3%);

115.在生成的位速率相对于所述位速率预期值的偏差落入所述位速率公差(如百分数3%)之内时,生成检查通过指示信息;在生成的位速率相对于所述位速率预期值的偏差位于所述位速率公差(如百分数3%)之外时,生成检查失败指示信息。

116.具体地,针对位速率的公差进行自动检查的代码实现时,可以分为位速率预期值大于生成的位速率的情景及位速率预期值小于生成的位速率的情景来分别百分比的计算。

117.如此,实现位速率质量检查。

118.在一些实施例中,根据预先配置的包速率检查指标,对所述数据流量进行质量检查,包括:

119.所述位速率检查指标包括包速率预期值、包速率预期公差;

120.生成所述仿真芯片的端口以第一传输方式传输数据时的包速率;

121.获取预先配置的所述包速率预期值及预先配置的所述包速率公差(如百分数

3%);

122.在生成的包速率相对于所述包速率预期值的偏差落入所述包速率公差(如百分数3%)之内时,生成检查通过指示信息;在生成的包速率相对于所述包速率预期值的偏差位于所述包速率公差(如百分数3%)之外时,生成检查失败指示信息。

123.如此,实现包速率质量检查。

124.在一些实施例中,根据预先配置的带宽分配比例检查指标,对所述数据流量进行质量检查,包括:

125.所述带宽分配比例检查指标包括多个带宽分配比例预期值、多个带宽分配比例预期公差(如百分数3%);

126.生成所述仿真芯片的端口以第一传输方式传输数据时各流量标签对应的带宽分配比例值;

127.获取预先配置的各流量标签对应的所述带宽分配比例预期值及预先配置的各流量标签对应的所述带宽分配比例公差(如百分数3%);

128.在任一流量标签对应的带宽分配比例相对于对应的带宽分配比例预期值的偏差落入所述带宽分配比例预期公差(如百分数3%)之内时,生成带宽分配比检查通过指示信息;在任一流量标签对应的带宽分配比例相对于对应的带宽分配比例预期值的偏差位于所述带宽分配比例预期公差(如百分数3%)之外时,生成带宽分配比检查失败指示信息。

129.在一些实施例中,还可以在各偏差值超过对应的公差时,生成错误提醒,如“rate check is error,please review log.”。

130.应该理解为,确定多流模式下的带宽分配比例时,因为是同一个端口,计算与每个所述流标签对应的字节数对应的包速率或位速率时,采用的芯片的主频、时间窗均相同。因此,可以根据包速率或位速率进而计算得到带宽分配比例值。又或者,可以直接根据与每个所述流标签对应的字节数进而计算得到带宽分配比例值,不再赘述。

131.如此,实现带宽分配比例质量检查。

132.在一些实施例中,以上步骤s30中,还包括:将所述检查通过指示信息或检查失败指示信息发送至文本文件可视化展示单元,以使得所述文本文件可视化展示单元展示所述所述检查通过指示信息(如,rate check result:ok)或检查失败指示信息(如,rate check result:null,如图4a所示)。

133.在一些实施例中,以上步骤s30中,具体包括:在每个第一周期内,将前述的位速率或包速率、与多个流标签分别对应的多个带宽分配比例,或检查通过指示信息或检查失败指示信息等保存至日志文件*.log。图4b、图4c、图4a则分别展示了单流模式下的包速率的日志文件、单流模式下的位速率的日志文件、多流模式下的数据流量及带宽分配比例值的日志文件。

134.具体地,所述文本文件可视化展示单元包括:操作系统中设置的文本文件编辑工具,如windows操作系统设置的文本编辑软件写字板(notepad)或记事本、如linux操作系统设置的文本编辑工具gedit。前述的操作系统还可以运行有前述芯片的仿真实例,如,linux操作系统运行的eda运行有前述芯片的仿真实例及可以展示数据流量波形图的verdi。

135.如图2所示,本发明实施例的芯片仿真过程中监测数据流量的装置,包括:

136.监测及统计单元210,用于监测仿真芯片的端口以第一传输方式传输的数据;使用

与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数;

137.数据流量计算单元220,用于将所述字节数根据一配置信息生成所述端口的数据流量,所述配置信息包括数据流量的计算方式;

138.可视化单元230,用于以可视化方式展示所述端口的数据流量。

139.在一些实施例中,所述监测及统计单元还用于监测仿真芯片的端口以第一传输方式传输的数据所包含的流标签;统计各流标签对应的所述数据包含的字节数;

140.所述数据流量计算单元还用于分别将各流标签对应的字节数根据一配置信息生成所述端口的各流标签对应的数据流量,所述配置信息包括数据流量的计算方式;

141.所述可视化单元还用于以可视化方式展示所述端口的各流标签的数据流量。

142.以上,监测及统计单元210、数据流量计算单元220、可视化单元230具体执行的步骤,可以分别参考前述步骤s10、s20或s30,不再赘述。

143.如图3a所示,本发明实施例的芯片仿真过程中监测数据流量的系统,包括:

144.至少一个适配器adp300,与至少一个仿真芯片500的至少一个端口port400对应地连接;

145.与所述至少一个适配器300对应地连接的至少一个流量监测器monitor200;

146.与所述至少一个流量监测器200连接的可视化设备display100;

147.其中,各所述适配器被配置为监测各所述仿真芯片的端口以第一传输方式传输的数据,使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数;

148.各流量监测器被配置为将所述字节数根据一配置信息生成所述端口的数据流量,所述配置信息包括数据流量的计算方式;

149.可视化设备被配置为用于以可视化方式展示各所述端口的数据流量。

150.如此,本发明实施例的芯片仿真过程中监测数据流量的系统通过配置不同的适配器和流量监测器,针对autbus、ddr、ssd、pcie等芯片分别进行可视化验证或可视化调试。

151.在一些实施例中,该系统可以对任一具有流量或带宽分配监测需求的芯片在其仿真过程中监测其数据流量,这时,针对该具有流量或带宽分配监测需求的芯片的每一个端口分别对应一个适配器和一个流量监测器。如图3b所示,仿真芯片500可以是利用eda实现的具有autbus、ddr、ssd或pcie中任一种或多种的数字电路芯片。

152.在一些实施例中,各流量监测器分别针对指定的端口监测其数据流量,所述流量监测器运行在eda仿真环境中,其中,所述仿真环境中还运行有针对所述芯片的仿真实例。如此,各端口port与适配器一一对应地设置。

153.在一些实施例中,用户(如测试工程师或验证工程师)将所述适配器配置为监测各所述仿真芯片的端口以第一传输方式传输的数据,使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数;如,根据端口对应的信号线上的脉冲序列配置。

154.在一些实施例中,所述适配器从端口获取的脉冲序列为上升沿触发或下降沿触发,所述适配器处理该脉冲序列,如上采样或下采样、将高电平转换为低电平、将低电平转换为高电平等,并使用与所述端口的传输协议匹配的字节数统计方法,统计所述数据包含的字节数。

155.在一些实施例中,为了便于用户使用,还包括:为端口传输的数据分别对应的各优先级适配对应的流标签,并配置到对应的流量监测器和适配器,以便于适配器和流量监测

器根据各流标签分组地采集传输字节或计算数据流量。

156.如此,适配器作为转换器,使用与所述第一传输方式匹配的字节数统计方法,统计所述数据包含的字节数,配置灵活,通用性好。如此,提供向用户开放的配置接口的适配器,可以由用户根据其验证场景进行灵活配置,通用性强。

157.在一些实施例中,为了便于用户使用,所述流量监测器向用户开放的可配置的接口变量或信号包括:数据有效使能。如通过配置该数据有效使能标识量,可以配置当前的流量监测器是否执行前述的生成数据流量的计算。如此,用户可以灵活地控制针对任一端口监测其数据流量。

158.在一些实施例中,为了便于用户使用,所述流量监测器向用户开放的可配置的接口变量或信号包括:统计起止点使能。如通过配置该统计起止点使能,如开始时间及结束时间,可以配置当前的流量监测器在开始时间至结束时间内,执行前述的生成数据流量的计算。如此,用户可以灵活地控制针对任一端口在指定的仿真时段内监测其数据流量。

159.在一些实施例中,为了便于用户使用,所述流量监测器向用户开放的可配置的接口变量或信号包括:速率类型(如rate mode)。如通过配置该速率类型(如rate mode)为pps,可以配置当前的流量监测器计算对应端口的包速率。如通过配置该速率类型(如rate mode)为bps,可以配置当前的流量监测器计算对应端口的位速率。

160.在一些实施例中,为了便于用户使用,所述流量监测器向用户开放的可配置的接口变量或信号包括:多流有效标识(如multi flow为on)。如通过配置该多流有效标识为on或off,可以配置当前的流量监测器工作在多流模式下还是单流模式下。

161.在一些实施例中,为了便于用户使用,所述流量监测器向用户开放的可配置的接口变量或信号包括:比例检查设置值(如,ratio check enable)。如通过配置该比例检查设置值为on或off,可以配置当前的流量监测器是否自动地进行质量检查。

162.在一些实施例中,为了便于用户使用,所述流量监测器向用户开放的可配置的接口变量或信号包括:带宽分配比例预期值(如exp_ratio)、带宽分配比例公差值(如exp_tol)。如通过配置比例检查设置值为on,及配置各流标签对应的带宽分配比例预期值及公差值,可以配置当前的流量监测器执行带宽分配比例检查或报错。

163.在一些实施例中,为了便于用户使用,所述流量监测器向用户开放的可配置的接口变量或信号包括:单独的控制开关,如check enable,使得可以人机交互地配置该控制开关(如check enable)的状态为on或off,可以方便用户(如测试工程师或验证工程师)根据需求,针对当前端口,可以只进行速率统计,不进行公差检查(如展示result:null),或者既进行统计又进行公差检查(如展示result:ok)。如此,用户可以根据实际情况灵活控制各流量监测器执行的流量监测方法,如,只进行流量统计,不进行流量的公差检查。

164.在一些实施例中,前述的带宽分配比例预期值及带宽分配比例公差值、位速率预期值及位速率公差、包速率预期值及包速率公差分别可以人机交互地配置,可以方便用户(如测试工程师或验证工程师)根据对包速率、位速率或者带宽分配比例的测试要求及检查要求灵活地进行相应的预期值及公差的设置。如此,可以通过检查各偏差值是否超过对应的公差,生成速率或带宽分配比例检查结果。

165.在一些实施例中,前述的各设置值可以通过人机交互的接口(interface)或预留的可配置接口(如command指令)获取及设置。

166.如此,可以灵活地通过配置项来配置所述流量监测器的配置信息生及数据流量的计算方式,因此,该芯片仿真过程中监测数据流量的系统使用灵活、调整方便。如此,提供向用户开放的配置接口的流量监测器,可以由用户根据其验证场景进行灵活配置,通用性强。

167.在一些实施例中,针对芯片的各端口,对应地创建一个日志文件*.log。如图4b、图4c、图4a所示,每一个日志文件内,针对端口记录多种流量信息,如bps、pps、bps或针对不同流标签的带宽分配比例等。

168.具体地,日志文件可以为txt格式或其他格式化文本。图4b展示的log文件的名称为:src_port_rate_checker_0_rate.log(/rl;其中,rate check enable:on记录了速率检查设置值;rate mode:bps记录了速率类型设置值。rate report target:src_port_rate_checker_0记录了流量监测器的名称。current freq:80mhz记录了芯片的主频为80mhz。current time:5009270570则记录了芯片仿真过程中记录的仿真时间,也即对芯片clk计数得到的时间,单位通常为皮秒(picosecond,为10-12秒)。

169.具体地,预先创建的各流量监测器具有预设的名称,如src_port_rate_checker_6,其中,“src_port”为芯片的源端口对应的端口的标识,“rate_checker”为针对所述端口的速率类型(如rate check或ratio check)的标识,“6”用于表示流量监测器的附加序号。如此,流量监测器的名称可以由芯片的端口(port)对应的标识、速率类型的标识、流量监测器的附加序号等组合得到,进而具有明确的指示意义,增加易读性。

170.相应地,在一些实施例中,在将前述的保存至日志文件时,可以根据各流量监测器的名称来命名日志文件。如图4b、图4c、图4a分别展示的日志文件的名称为:src_port_rate_checker_0_rate.log、src_port_rate_checker_6_rate.log、prio_sch_checker.log。其中,prio_sch为以优先级为特征调度带宽分配比例的端口。

171.如此,根据端口的标识(可以包括监测接口的标识、设备的标识(如ddr)或模块的标识对各流量监测器进行命名,以及根据各流量监测器的名称对各端口对应的日志文件进行命名,有利于更高效地管理日志文件,有利于避免因不同端口的混杂在同一个或多个公用的文件内而导致后续不容易查找日志文件,有利于根据日志文件的名称方便地查找各端口的。

172.在一些实施例中,所述文本式可视化单元包括文本编辑器,参照前述说明及图4b、图4c和图4a,所述文本编辑器用于滚动展示前述说明的日志文件。

173.在一些实施例中,所述可视化单元包括verdi,所述verdi用于展示所述芯片仿真过程中至少一个端口对应的速率走势。参照前述说明及图5,所述端口对应的速率走势可以是以第一周期更新的位速率或包速率,可以是以第一周期更新的与各所述流标签分别对应的带宽分配比例值。

174.在一些实施例中,在基于verdi展示所述芯片仿真过程中至少一个端口对应的速率走势(如图5所示)时,在代码实现时,可以通过声明的实数类型(real)的变量(如,如,real rate),在不同的时间片(如前述的第一周期)内分别记录生成的位速率或包速率或与各所述流标签分别对应的带宽分配比例值。如此,如图5所示,速率走势在verdi工具中是基于时间片进行变化的。

175.在一些实施例中,还包括:通过解析生成的位速率或包速率的数量级,确定与生成的位速率或包速率对应的包括有数量级的速率单位,以实现以较少的字母或数字更简洁地

显示生成的位速率或包速率。如图4b、图4c、图4a或图5所示,包括有数量级的速率单位可以为以下任一项:bps、kbps、mbps、gbps、pps、kpps、mpps、gpps。其中,k为kilo,用于指示103;m为mega,用于指示106;g为giga,用于指示109,分别用于表示数据的量级。

176.在一些实施例中,设置有多个流量监测器,分别生成前述的位速率、包速率及带宽分配比例或质量检查,用于统计和检查仿真环境中各芯片、模块或系统对外传输数据的端口分别对应的信号线上的位速率、包速率或带宽分配比例值。相应地,各流量监测器分别生成的可以发送给同一个可视化设备100,并由可视化设备100分屏、分页或分tab项地展示。如参照图5左侧部分的列表及右侧部分的窗口所示,在verdi中可以分屏地展示多个端口对应的。

177.在一些实施例中,流量监测器生成的及对应的日志文件可以记载芯片仿真过程中端口的位速率、包速率或带宽分配比例等随时间的变化过程。verdi可以读取端口的位速率、包速率或带宽分配比例等,并在窗口图形化地显示其随时间的变化过程。图5右侧部分的图形窗口中展示的走势图便于直观展示流量信息的变化趋势,其中,横坐标为时间,纵坐标为前述各在各第一周期内分别对应的数值。图5中间部分则对应于右侧部分的走势图中指定时刻的流量信息的数值。

178.如图3b所示,根据左侧端口port401传输数据使用的单流模式或多流模式、使用的第一传输协议(如autbus总线),对应地配置第一适配器adp301,以在芯片500的仿真过程中,监测左侧端口port401以第一传输协议传输的数据,使用与所述第一传输协议匹配的字节数统计方法,统计所述数据包含的字节数b01。

179.相应地,根据左侧端口port401传输数据使用的单流模式或多流模式、使用的第一传输协议(如autbus总线),对应地配置第一流量监测器monitor201,以在芯片500的仿真过程中,将所述字节数b01根据预设的配置信息生成左侧端口port401的数据流量d01,所述配置信息包括数据流量的计算方式c01。

180.以及,根据左侧端口port401传输数据使用的单流模式或多流模式、使用的第一传输协议(如autbus总线),对应地配置可视化设备display100,以在芯片500的仿真过程中,以可视化方式展示所述端口的数据流量d01。

181.如图3b所示,根据右侧端口port402传输数据使用的单流模式或多流模式、使用的第二传输协议(如pcie总线),对应地配置第二适配器adp302,以在芯片500的仿真过程中,监测右侧端口port402以第二传输协议传输的数据,使用与所述第二传输协议匹配的字节数统计方法,统计所述数据包含的字节数b02。

182.相应地,根据右侧端口port402传输数据使用的单流模式或多流模式、使用的第二传输协议(如pcie总线),对应地配置第二流量监测器monitor202,以在芯片500的仿真过程中,将所述字节数b02根据预设的配置信息生成右侧端口port402的数据流量d02,所述配置信息包括数据流量的计算方式c02。

183.以及,根据右侧端口port402传输数据使用的单流模式或多流模式、使用的第二传输协议(如pcie总线),对应地配置可视化设备display100,以在芯片500的仿真过程中,以可视化方式展示所述端口的数据流量d02。

184.如图3a所示,在一些实施例中,芯片为网络芯片switch500。使用eda验证switch500的各个以太网端口的速率是否达到线速或任一端口下的8个优先级的带宽分配

是否符合调度配置。

185.采用如图3a所示的芯片仿真过程中监测数据流量的系统,监测switch500各端口的数据流量。这时,switch500为被监测设备,通过4个以太网端口port400传输数据,由4个适配器300作为监测流量的适配接口。对其中任一个端口,将8个优先级对应的流特征作为流标签适配给一适配器300,以使得该适配器300在芯片仿真过程中监测端口port400经以太网协议传输的数据,使用与所述以太网协议匹配的字节数统计方法,统计所述数据包含的字节数。与该适配器300相对应,配置一流量监测器200,以使得该流量监测器200在芯片仿真过程中,根据配置信息,如,时间窗、主频、单流模式或多流模式、速率预期值以及速率误差、带宽分配比例预期值、及相应的公差值,自动化进行前述的质量检查,或报错,并输出*.log文件,同时将实时走势输出到可视化设备100上。

186.以上,本发明提供的芯片仿真过程中监测数据流量的方法及系统,可以监测芯片各端口在单流模式时的传输速率(如,包速率或位速率),可以在可视化工具中展示各端口的包速率或位速率的走势,进而实现数据流量走势的可视化;针对芯片的各端口,支持灵活分流和调度配置,可以针对端口的多流模式分别统计对应的带宽分配比例。如此,该方法及装置,配置灵活,通用性好,适合各种规模芯片传输速率的自动化监测,使用灵活,自动化程度高。

187.如图6所示,本技术实施例的计算设备700包括:处理器710、存储器720,还可以包括通信接口730。应理解,该图6中所示的计算设备700中的通信接口730可以用于与其他设备之间进行通信。其中,该处理器710可以与存储器720连接。该存储器720可以用于存储该程序代码和数据。因此,该存储器720可以是处理器710内部的存储单元,也可以是与处理器710独立的外部存储单元,还可以是包括处理器710内部的存储单元和与处理器710独立的外部存储单元的部件。

188.可选的,计算设备700还可以包括总线。其中,存储器720、通信接口730可以通过总线与处理器710连接。总线可以是外设部件互连标准(peripheral component interconnect,pci)总线或扩展工业标准结构(extended industry standard architecture,eisa)总线等。总线可以分为地址总线、数据总线、控制总线等。

189.应理解,在本技术实施例中,该处理器710可以采用中央处理单元(central processing unit,cpu)。该处理器还可以是其它通用处理器、数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、现成可编程门矩阵(field programmable gate array,fpga)或者其它可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。或者该处理器710采用一个或多个集成电路,用于执行相关程序,以实现本技术实施例所提供的技术方案。

190.该存储器720可以包括只读存储器和随机存取存储器,并向处理器710提供指令和数据。处理器710的一部分还可以包括非易失性随机存取存储器。例如,处理器710还可以存储设备类型的信息。

191.在计算设备700运行时,处理器710执行存储器720中的计算机执行指令执行前述的芯片仿真过程中监测数据流量的方法的操作步骤。

192.应理解,根据本技术实施例的计算设备700可以对应于执行根据本技术各实施例

的方法中的相应主体,并且计算设备700中的各个模块的上述和其它操作和/或功能分别为了实现本实施例各方法的相应流程,为了简洁,在此不再赘述。

193.以上各装置的功能可以通过由处理器执行程序(软件)来实现,另外,也可以通过lsi(large scale integration,大规模集成电路)和asic(application specific integrated circuit,专用集成电路)等硬件来实现,或者还可以通过软件和硬件的结合来实现。

194.在本技术全文中使用的词语“第一、第二、第三等”或模块a、模块b、模块c等类似用语,仅用于区别类似的对象,不代表针对对象的特定排序,可以理解的是,在允许的情况下可以互换特定的顺序或先后次序。

195.在本技术全文中,所涉及的表示步骤的标号,如s10、s20

……

等,并不表示一定会按此步骤执行,在允许的情况下可以互换前后步骤的顺序,或同时执行。

196.在本技术的全文中使用的术语“包括”不应解释为限制于其后列出的内容;它不排除其它的结构要素或步骤。因此,其应当诠释为指定所提到的所述技术特征、整体、步骤或部件的存在,但并不排除存在或添加一个或更多其它技术特征、整体、步骤或部件及其组群。

197.可以理解,本领域技术人员可以将本技术全文中提到的一个或多个实施例中提到的特征,以任何适当的方式与其他实施例中的特征进行组合来实施本技术。

198.注意,前述仅为本技术的较佳实施例及所运用的技术原理。本领域技术人员会理解,本技术不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本技术的保护范围。因此,虽然通过以上实施例对本技术进行了较为详细的说明,但是本技术不仅仅限于以上实施例,在不脱离本技术的技术构思的情况下,还可以包括更多其他等效实施例,均属于本技术的保护范畴。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。