1.本公开涉及半导体封装技术领域,具体涉及半导体封装装置及其制造方法。

背景技术:

2.目前的硅光子结构中,电子芯片(eic,electronic integrated circuit)与光子芯片(pic,photonic integrated circuit)的连接方式已从传统的并排(side by side)设置演变成为通过重布线层垂直连接电子芯片和光子芯片。

3.如图1所示,光子芯片11通过重布线层垂直连接电子芯片12,图1中,电子芯片12的主动面朝上与光子芯片11进行电性连接,而电子芯片12的非主动面则需要使用粘合层13(例如,裸片附着膜(daf,die attach film))固定到下方重布线层上。但如果电子芯片12中具有贯穿电子芯片12的硅通孔(tsv,through silicon via),则粘合层13会阻挡电子芯片与下方重布线层的电性连接,进而若后续将硅光子结构结合到基板上时,需要额外设计高度较高的导电柱来将电子芯片12的硅通孔从电子芯片12上方连接到额外设计高度较高的导电柱,并通过上述导电柱来连接到基板,从而导致电子芯片12的硅通孔到基板的导电路径较长。

4.同理,若电子芯片12的主动面朝下,则可以采取表面贴装技术(smt,surface mounting technology)方式,例如通过焊料键合(solder bonding)将电子芯片12的主动面与下方的重布线层电性连接,进而后续将硅光子结构键合到基板上时,电子芯片12与下方基板之间电性连接路径较短。然而,由于电子芯片12的主动面朝下,这可能导致需要额外设计高度较高的导电柱来将电子芯片12的朝下的主动面连接到上述额外设计高度较高的导电柱,并通过上述导电柱来连接到光子芯片11,这将导致电子芯片12的主动面到光子芯片11之间的电性路径较长。

技术实现要素:

5.本公开提出了半导体封装装置及其制造方法。

6.第一方面,本公开提供了一种半导体封装装置,包括:

7.第一线路层;

8.电子芯片,设置于所述第一线路层上,所述电子芯片具有相对的第一表面和第二表面,所述第一表面邻近所述第一线路层;

9.至少两个第一导电垫,设置于第一表面;

10.至少两个第二导电垫,设置于所述第二表面,所述至少两个第一导电垫和所述至少两个第二导电垫中存在至少一对水平投影重叠且电性不连接的第一导电垫和对应的第二导电垫。

11.在一些可选的实施方式中,所述至少两个第一导电垫和所述至少两个第二导电垫中存在至少一对电性连接的第一导电垫和对应的第二导电垫。

12.在一些可选的实施方式中,所述电性连接的第一导电垫和对应的第二导电垫通过

贯穿所述电子芯片的硅通孔电连接。

13.在一些可选的实施方式中,所述半导体封装装置还包括:

14.至少两个电连接件,设置于所述第一线路层下,且电连接所述第一线路层。

15.在一些可选的实施方式中,所述半导体封装装置还包括:

16.衬底,设置于所述至少两个电连接件下且接触所述至少两个电连接件,所述至少两个第一导电垫中存在用于将所述电子芯片电连接至所述衬底的第一导电垫和用于将所述电子芯片物理连接至所述衬底的第一导电垫。

17.在一些可选的实施方式中,所述半导体封装装置还包括:

18.第二线路层,设置于所述电子芯片上且电连接所述第二导电垫;

19.光子芯片,设置于所述第二线路层上且电连接所述第二线路层。

20.在一些可选的实施方式中,所述半导体封装装置还包括:

21.至少两个第一导电柱,设置于所述第一线路层和所述第二线路层之间,且电连接所述第一线路层和所述第二线路层;

22.模封层,设置于所述第一线路层和所述第二线路层之间,且包覆各所述第一导电柱和所述电子芯片。

23.在一些可选的实施方式中,所述第一导电垫的电阻率大于第二导电垫的电阻率。

24.在一些可选的实施方式中,所述第一导电垫为焊料或导电胶,所述第二导电垫为金属导电垫或金属导电柱。

25.在一些可选的实施方式中,所述半导体封装装置包括至少两个所述电子芯片。

26.第二方面,本公开提供了一种制造半导体封装装置的方法,包括:

27.在载板上形成第一线路层;

28.提供电子芯片,所述电子芯片具有相对的第一表面和第二表面,所述第一表面设置有至少两个第一导电垫,所述第二表面设置有至少两个第二导电垫,所述至少两个第一导电垫和所述至少两个第二导电垫中存在至少一对水平投影重叠且电性不连接的第一导电垫和对应的第二导电垫;

29.将所述电子芯片设置于所述第一线路层,且所述第一表面邻近所述第一线路层。

30.在一些可选的实施方式中,所述方法还包括:

31.在所述电子芯片上方形成第二线路层,以使所述第二线路层电连接各所述第二导电垫和各所述导电柱;

32.提供光子芯片,以及将所述光子芯片设置于所述第二线路层上,以使所述光子芯片电连接所述第二线路层。

33.在一些可选的实施方式中,在所述在载板上形成第一线路层之后,所述方法还包括:

34.在所述第一线路层上形成至少两个第一导电柱,以使各所述第一导电柱电连接所述第一线路层;以及

35.在所述电子芯片上方形成第二线路层之前,所述方法还包括:

36.在所述第一线路层上模封以形成包覆各所述第一导电柱和所述电子芯片的模封层;

37.研磨所述模封层的上表面以露出各所述第二导电垫和各所述第一导电柱。

38.在一些可选的实施方式中,所述方法还包括:

39.翻转所述半导体封装装置,以及在所述第一线路层的表面形成至少两个电连接件后再次翻转;

40.提供衬底,以及将所述半导体封装装置设置于所述衬底上,以使所述至少两个电连接件下接触所述衬底。

41.为了解决现有硅光子结构中电子芯片与上方光子芯片或者与下方衬底之间电性路径较长的问题,本公开提供的半导体封装装置和及其制造方法,通过在电子芯片两个相对表面分别设置第一导电垫和第二导电垫,可同时降低硅光子结构中电子芯片与上方光子芯片以及与下方衬底之间的电性路径长度。

附图说明

42.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本公开的其它特征、目的和优点将会变得更明显:

43.图1是现有技术中包括光子芯片的半导体封装装置的一个实施例的纵向截面结构示意图;

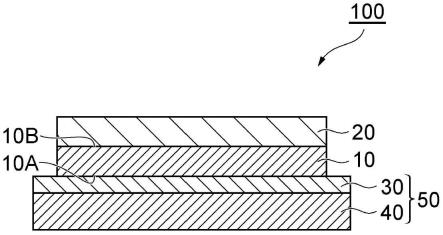

44.图2a和图2b分别是根据本公开的半导体封装装置2a和2b的一个实施例的纵向截面结构示意图;

45.图3a、3b、3c、3d、3e、3f、3g、3h和3i是根据本公开的半导体封装装置的不同实施例3a、3b、3c、3d、3e、3f、3g、3h和3i的纵向截面结构示意图。

46.符号说明:

47.11-光子芯片;12-电子芯片;13-粘合层;21-第一线路层;22-电子芯片;22a-第一表面;22b-第二表面;23-第一导电垫;24-第二导电垫;231&241-水平投影重叠且电性不连接的第一导电垫和对应的第二导电垫;232&242电性连接的第一导电垫和对应的第二导电垫;221-硅通孔;25-第二线路层;26-光子芯片;27-电连接件;231-用于将电子芯片物理连接至衬底的第一导电垫;232-用于将电子芯片电连接至衬底的第一导电垫;28-第一导电柱;29-模封层;30-衬底。

具体实施方式

48.下面结合附图和实施例对说明本发明的具体实施方式,通过本说明书记载的内容本领域技术人员可以轻易了解本发明所解决的技术问题以及所产生的技术效果。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外,为了便于描述,附图中仅示出了与有关发明相关的部分。

49.需要说明的是,说明书附图中所绘示的结构、比例、大小等,仅用于配合说明书所记载的内容,以供本领域技术人员的了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等用语,也仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本发明可实施的范畴。

50.还需要说明的是,本公开的实施例对应的纵向截面可以为对应前视图方向截面,横向截面可以为对应右视图方向截面,而水平截面可以为对应上视图方向截面。

51.另外,在不冲突的情况下,本公开中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本公开。

52.参考图2a,图2a示出了根据本公开的半导体封装装置的一个实施例2a的纵向截面结构示意图。

53.如图2a所示,半导体封装装置2a包括:第一线路层21、电子芯片22、至少两个第一导电垫23、至少两个第二导电垫24。其中:

54.电子芯片22设置于第一线路层21上。电子芯片22具有相对的第一表面22a和第二表面22b,第一表面22a邻近第一线路层21,第二表面22b远离第一线路层21。

55.第一导电垫23设置于第一表面22a,第二导电垫24设置于第二表面22b。

56.至少两个第一导电垫23中和至少两个第二导电垫24中存在至少一对水平投影重叠且电性不连接的第一导电垫231和对应的第二导电垫241。如图2a中所示。

57.在一些可选的实施方式中,如图2a所示,半导体封装装置2a还可以包括:第二线路层25和光子芯片26。其中:

58.第二线路层25设置于电子芯片22上且电连接第二导电垫24。即,第二导电垫24用于实现电子芯片22与第二线路层25的电性连接。

59.光子芯片26设置于第二线路层25上且电连接第二线路层25。由于电子芯片22通过第二导电垫24电连接第二线路层25,进而电子芯片22和光子芯片26仅通过第二导电垫24和第二线路层25即实现电性连接,二者之间电性路径较短。即,电子芯片22向上与光子芯片26之间的电性路径较短。

60.至少两个第一导电垫23中存在电连接第一线路层21的第一导电垫23,进而电子芯片22向下仅通过第一导电垫23与第一线路层21之间即实现电性连接,二者之间电性路径较短。后续再将半导体封装装置2a通过第一线路层21键合到衬底上时,电子芯片22与衬底之间的电性路径也较短。

61.这里,第一线路层21和第二线路层25可以是由导电材料和介电材料(dielectric)组成的重布线层。需要说明的是,制程上可以采用当前已知或未来开发的重布线层形成技术,本公开对此不做具体限定,例如可采用包括但不限于光刻、电镀(plating),化学镀(electroless plating)等形成重布线层。这里,介电材料可包括有机物和/或无机物,其中有机物例如可以是:聚酰胺纤维(polyamide,pa)、聚酰亚胺(polyimide,pi)、环氧树脂(epoxy)、聚对苯撑苯并二噁唑(poly-p-phenylene benzobisoxazole,pbo)纤维、fr-4环氧玻璃布层压板、pp(prepreg,预浸材料或称为半固化树脂、半固化片)、abf(ajinomoto build-up film)等,而无机物例如可以是硅(si),玻璃(glass),陶瓷(ceramic),氧化硅,氮化硅,氧化钽等。导电材料可包括种子层和金属层。这里,种子层例如可以是钛(ti),钨(w),镍(ni)等,而金属层例如可以是金(au)、银(ag)、铝(al)、镍(ni)、钯(pd)、铜(cu)或其合金。

62.在一些可选的实施方式中,如图2a所示,至少两个第一导电垫23和至少两个第二导电垫24中存在至少一对电性连接的第一导电垫232和对应的第二导电垫242。可选地,第二导电垫242可以是设置在电子芯片22的第二表面22b(即,主动面)的负责电源和接地信号的导电垫,进而可以将电子芯片22的第二表面22b(即,主动面)的电源和接地信号通过第一

导电垫232延伸至第一线路层21,进而在后续将半导体封装装置2a通过第一线路层21键合至衬底时,可以将电子芯片22的第二表面22b(即,主动面)的电源和接地信号通过第二导电垫242、第一导电垫232和第一线路层21延伸至衬底。如此,相对于现有技术中中电子芯片主动面朝上的设计而言,不需额外设计粘合层连接电子芯片和下方重布线层,也就不需要设计高度较高的导电柱,即通过电子芯片22两表面设置的电性连接的第一导电垫232和对应的第二导电垫242,可实现电子芯片22与下方第一线路层21以至后续衬底之间的电性连接,减少了电性连接路径。

63.基于上述可选实施方式,可选地,电性连接的第一导电垫232和对应的第二导电垫242通过贯穿电子芯片22的硅通孔221电连接。通过硅通孔221可以进一步缩短电子芯片22的第二表面22b(即,主动面)与电子芯片22下方第一线路层21以至后续衬底之间的电性连接路径。

64.在一些可选的实施方式中,如图2a所示,半导体封装装置2a还可以包括:至少两个电连接件27。电连接件27设置于第一线路层21下,且电连接件27电连接第一线路层21。这里,电连接件27用于实现半导体封装装置2a与外部的电连接。

65.作为示例,电连接27可以是导线(conductive trace)、焊球(solder ball)、焊垫(solder pad)、焊料凸块(solder bump)等。

66.基于上述可选实施方式,可选地,如图2a所示,半导体封装装置2a还可以包括:衬底30。衬底30设置于至少两个电连接件27下且接触至少两个电连接件27。进而,半导体封装装置2a可以通过衬底30实现与外部的电连接。

67.这里,衬底30可以是各种类型的衬底,本公开对此不做具体限定。

68.衬底30可包括有机物和/或无机物,其中有机物例如可以是:聚酰胺纤维(polyamide,pa)、聚酰亚胺(polyimide,pi)、环氧树脂(epoxy)、聚对苯撑苯并二噁唑(poly-p-phenylene benzobisoxazole,pbo)纤维、fr-4环氧玻璃布层压板、pp(prepreg,预浸材料或称为半固化树脂、半固化片)、abf(ajinomoto build-up film)等,而无机物例如可以是硅(si),玻璃(glass),陶瓷(ceramic),氧化硅,氮化硅,氧化钽等。

69.衬底30还可以是例如印刷电路板,比如纸基铜箔层合物、复合铜箔层合物或聚合物浸渍的玻璃纤维基铜箔层合物等。

70.衬底30还可包括互连结构(interconnection),比如导电迹线(conductive trace)、导电导孔(conductive via)等。这里,导电导孔可以是通孔、埋孔或盲孔,且通孔、埋孔或盲孔中可以填充例如金属或金属合金的导电材料,这里,金属例如可以是金(au)、银(ag)、铝(al)、镍(ni)、钯(pd)、铜(cu)或其合金。

71.在一些可选的实施方式中,如图2a所示,至少两个第一导电垫23中存在用于将电子芯片22电连接至衬底30的第一导电垫232和用于将电子芯片22物理连接至衬底30的第一导电垫231。也可以理解为,第一导电垫232是真正的导电垫,而第一导电垫231为虚设导电垫(dummy conductive pad)。通过设计虚设导电垫,可以在后续模封过程中起到固定电子芯片21防止电子芯片21产生位移(shift)的作用,进而达到提高产品良率的效果。

72.在一些可选的实施方式中,如图2a所示,第一导电垫23的电阻率大于第二导电垫24的电阻率。这样,第二导电垫24的导电性更佳,可提供与第二线路层25之间更优良的电连接性能。作为示例,第一导电垫23可以为锡、锡银等,第二导电垫24可以为铜、金、银等。

73.在一些可选的实施方式中,如图2a所示,第一导电垫23可以为焊料(solder),第二导电垫24可以为金属导电垫(metal pad)或金属导电柱(metal pillar)。

74.在一些可选的实施方式中,如图2a所示,半导体封装装置2a还可以包括:至少两个第一导电柱28和模封层29。其中:

75.第一导电柱28设置于第一线路层21和第二线路层25之间,且第一导电柱28电连接第一线路层21和第二线路层25。

76.模封层29设置于第一线路层21和第二线路层25之间,且模封层29包覆各个第一导电柱28和电子芯片22。

77.模封层29可以是由各种模封材料(molding compound)形成。例如,模封材料可包括环氧树脂(epoxy resin)、填充物(filler)、催化剂(catalyst)、颜料(pigment)、脱模剂(release agent)、阻燃剂(flame retardant)、耦合剂(coupling agent)、硬化剂(hardener)、低应力吸收剂(low stress absorber)、粘合促进剂(adhesion promoter)、离子捕获剂(ion trapping agent)等。

78.采用上述可选实施方式,可以对半导体封装装置2a提供支撑,其中,第一导电柱28除了可以提供第一线路层21和第二线路层25之间的电性连接以外,还可以提供第一线路层21和第二线路层25之间的物理支撑。另外,通过设计导电柱28和第二线路层25,后续可以在第二线路层25上根据实际产品需要设置电子元件,例如可以是有源元件或者无源元件。其中,有源元件例如可以是电源管理集成电路(pmic,power management integrated circuit)芯片,无源元件例如可以是集成无源器件(ipd,integrated passive device)。

79.在一些可选的实施方式中,如图2a所示,半导体封装装置2a可以包括一个或两个电子芯片22。

80.下面参考图2b,图2b是根据本公开的半导体封装装置的一个实施例2b的纵向截面结构示意图。图2b所示的半导体封装装置2b类似于图2b中所示的半导体封装装置2b,不同之处在于:半导体封装装置2b还包括:衬底30。衬底30设置于至少两个电连接件27下且接触至少两个电连接件27。

81.图3a、3b、3c、3d、3e、3f、3g、3h和3i是根据本公开的半导体封装装置的不同实施例3a、3b、3c、3d、3e、3f、3g、3h和3i的纵向截面结构示意图。为了更好地理解本公开的各方面,已简化各图。

82.参考图3a,在载板31上形成第一线路层21。

83.制程上可以采用当前已知或未来开发的重布线层形成技术形成第一线路层21,本公开对此不做具体限定。例如可采用包括但不限于光刻、电镀(plating),化学镀(electroless plating)等形成第一线路层21。

84.例如可以首先在载板31上设置介电层,再形成种子层(例如,可采用物理气象沉积方法),再涂覆光刻胶,然后使用光刻机对光刻胶进行曝光显影,接着进行电镀金属(例如,铜),最后剥离光刻胶并蚀刻掉种子层后得到第一层的线路。如需多层线路可重复上述步骤以得到包括多层线路的第一线路层21。

85.参考图3b,在第一线路层21上形成至少两个第一导电柱28,以使各第一导电柱28电连接第一线路层21。

86.这里,第一导电柱28除了可以用于电性连接电子芯片22的第二表面22b设置的第

二导电垫24和第一线路层21外,还可以在后续是3c中将电子芯片22取放到第一线路层21的过程中作为电子芯片22的对准标记(alignment mark),以方便将电子芯片22设置在指定位置。

87.制程上,可以采用例如在第一线路层21上涂覆厚度较厚的光刻胶,然后使用光刻机对光刻胶进行曝光显影,接着进行电镀得到第一导电柱28(例如,铜柱),最后剥离光刻胶得到第一导电柱28。

88.参考图3c,提供电子芯片22,以及将电子芯片22设置于第一线路层21,且第一表面22a邻近第一线路层21。

89.这里,电子芯片22具有相对的第一表面22a和第二表面22b。

90.第一表面22a设置有至少两个第一导电垫23。第二表面22b设置有至少两个第二导电垫24。至少两个第一导电垫23和至少两个第二导电垫24中存在至少一对水平投影重叠且电性不连接的第一导电垫231和对应的第二导电垫241。可选地,至少两个第一导电垫23和至少两个第二导电垫24中还可以存在至少一对电性连接的第一导电垫232和对应的第二导电垫242。另外,由于在前述步骤3b中在第一线路层21上形成了至少两个第一导电柱28,这里在将电子芯片22设置到第一线路层21的过程中,可以以第一导电柱28作为电子芯片22的对准标记(alignment mark),以方便将电子芯片22设置在指定位置。

91.制程上,可以采用例如倒装芯片键合(fcb,flip-chip bonding)或者热压键合(tcb,thermal compression bonding)等技术将电子芯片22设置于第一线路层21。

92.参考图3d,在第一线路层21上模封以形成包覆各第一导电柱28和电子芯片22的模封层29,以及研磨模封层29表面以露出各第二导电垫24和各第一导电柱28。

93.模封制程例如可以选以下至少一项:自由转注成型(transfer molding)、注入成型(injection molding)、压模成型(compression molding)、液态成型(liquid molding)和喷涂射成型(spray molding)。

94.参考图3e,在电子芯片22上方形成第二线路层25,以使第二线路层25电连接各第二导电垫24和各第一导电柱28。

95.制程上可以采用与前述形成第一线路层21的类似技术在电子芯片22上方形成第二线路层25,在此不再赘述。

96.参考图3f,提供光子芯片26,以及将光子芯片26设置于第二线路层25上,以使光子芯片26电连接第二线路层。

97.参考图3g,剥离载板31。

98.制程上例如可采用激光剥离。

99.参考图3h,翻转半导体封装装置,以及在第一线路层21的表面形成至少两个电连接件27后再次翻转;

100.参考图3i,提供衬底30,以及将半导体封装装置设置于衬底30上,以使至少两个电连接件27接触衬底30。

101.制程上,可以采用例如倒装芯片键合或者热压键合等技术将半导体封装装置设置于衬底30上。

102.尽管已参考本公开的特定实施例描述并说明本公开,但这些描述和说明并不限制本公开。所属领域的技术人员可清楚地理解,可进行各种改变,且可在实施例内替代等效元

件而不脱离如由所附权利要求书限定的本公开的真实精神和范围。图示可能未必按比例绘制。归因于制造过程中的变量等等,本公开中的技术再现与实际实施之间可能存在区别。可存在未特定说明的本公开的其它实施例。应将说明书和图示视为说明性的,而非限制性的。可作出修改,以使特定情况、材料、物质组成、方法或过程适应于本公开的目标、精神以及范围。所有此些修改都落入在此所附权利要求书的范围内。虽然已参考按特定次序执行的特定操作描述本文中所公开的方法,但应理解,可在不脱离本公开的教示的情况下组合、细分或重新排序这些操作以形成等效方法。因此,除非本文中特别指示,否则操作的次序和分组并不限制本公开。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。