技术特征:

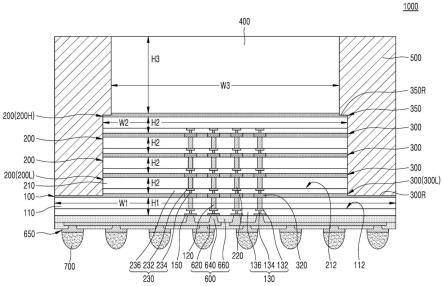

1.一种半导体封装,包括:第一半导体芯片,包括具有彼此相反的有源表面和无源表面的第一半导体基板,所述第一半导体芯片包括穿透所述第一半导体基板的至少一部分的多个第一贯通电极;多个第二半导体芯片,包括具有彼此相反的有源表面和无源表面的第二半导体基板,所述第二半导体基板的所述有源表面面对所述第一半导体基板的所述无源表面,所述多个第二半导体芯片堆叠在所述第一半导体芯片上;多个接合焊盘,布置在所述第一半导体芯片和所述多个第二半导体芯片之间;芯片接合绝缘层,被配置为围绕所述多个接合焊盘并布置在所述第一半导体芯片和所述多个第二半导体芯片之间;以及至少一个支撑虚设基板,堆叠在所述多个第二半导体芯片上并具有布置在其下表面上的支撑接合绝缘层,其中所述多个第二半导体芯片中的至少一些包括穿透所述第二半导体基板的至少一部分的多个第二贯通电极,其中所述多个接合焊盘将所述多个第一贯通电极电连接到所述多个第二贯通电极,其中所述至少一个支撑虚设基板的总垂直高度大于所述第一半导体芯片和所述多个第二半导体芯片中每个的各自的垂直高度。2.根据权利要求1所述的半导体封装,其中所述至少一个支撑虚设基板包括堆叠在所述多个第二半导体芯片上的多个支撑虚设基板,以及所述多个支撑虚设基板中的至少一些的各自的垂直高度等于或小于所述第一半导体芯片和所述多个第二半导体芯片中每个的各自的垂直高度。3.根据权利要求2所述的半导体封装,其中所述多个支撑虚设基板当中的最上面的支撑虚设基板的垂直高度小于所述多个支撑虚设基板当中的剩余的支撑虚设基板的每个的垂直高度。4.根据权利要求2所述的半导体封装,其中所述多个支撑虚设基板当中的最上面的支撑虚设基板的垂直高度大于所述多个支撑虚设基板当中的剩余的支撑虚设基板、所述第一半导体芯片和所述多个第二半导体芯片中每个的各自的垂直高度。5.根据权利要求1所述的半导体封装,其中仅一个支撑虚设基板堆叠在所述多个第二半导体芯片上,所述一个支撑虚设基板具有比所述第一半导体芯片和所述多个第二半导体芯片中每个的各自的垂直高度大的垂直高度。6.根据权利要求1所述的半导体封装,其中所述多个第二半导体芯片的水平宽度小于所述第一半导体芯片的水平宽度,其中所述至少一个支撑虚设基板的水平宽度小于所述多个第二半导体芯片的所述水平宽度。7.根据权利要求1所述的半导体封装,其中,在覆盖所述多个第二半导体芯片当中的最上面的第二半导体芯片的上表面的所述支撑接合绝缘层中,与所述至少一个支撑虚设基板垂直重叠的部分的厚度大于不与所述至少一个支撑虚设基板垂直重叠的部分的厚度。8.根据权利要求1所述的半导体封装,其中,在覆盖所述第一半导体芯片的上表面的芯片接合绝缘层中,在垂直方向上与所述多个第二半导体芯片重叠的部分的厚度具有比不与

所述多个第二半导体芯片垂直重叠的部分大的值。9.根据权利要求1所述的半导体封装,其中所述至少一个支撑虚设基板是裸晶片的一部分,其中所述多个第二半导体芯片当中的最上面的第二半导体芯片不具有所述第二贯通电极,其中所述支撑接合绝缘层的上表面和下表面仅与半导体材料接触。10.根据权利要求1所述的半导体封装,其中所述多个接合焊盘、所述芯片接合绝缘层和所述支撑接合绝缘层中的每个被扩散接合以各自形成一个整体。11.一种半导体封装,包括:高带宽存储器(hbm)控制器管芯,包括具有彼此相反的有源表面和无源表面的第一半导体基板,所述hbm控制器管芯包括穿透所述第一半导体基板的至少一部分的多个第一贯通电极;多个动态随机存取存储器(dram)管芯,包括具有彼此相反的有源表面和无源表面的第二半导体基板,所述第二半导体基板的所述有源表面面对所述第一半导体基板的所述无源表面,所述多个dram管芯堆叠在所述第一半导体基板上;多个接合焊盘,布置在所述hbm控制器管芯和所述多个dram管芯之间;芯片接合绝缘层,被配置为围绕所述多个接合焊盘并布置在所述hbm控制器管芯和所述多个dram管芯之间;以及多个支撑虚设基板,依次堆叠在所述多个dram管芯上并具有附接到其每个下表面的支撑接合绝缘层,其中所述多个dram管芯当中的除了最上面的dram管芯以外的剩余的dram管芯包括多个第二贯通电极,所述多个第二贯通电极穿透所述第二半导体基板的至少一部分并通过所述多个接合焊盘电连接到所述多个第一贯通电极,其中所述多个支撑虚设基板中的每个的垂直高度等于或小于所述第一半导体基板和所述多个dram管芯中每个的各自的垂直高度,其中所述多个支撑虚设基板的总垂直高度大于所述第一半导体基板和所述多个dram管芯中每个的各自的垂直高度。12.根据权利要求11所述的半导体封装,还包括:在所述hbm控制器管芯上的封装模制层,所述封装模制层覆盖所述hbm控制器管芯的上表面、所述多个dram管芯的侧表面和所述多个支撑虚设基板的侧表面,但暴露所述多个支撑虚设基板当中的最上面的支撑虚设基板的上表面而不覆盖所述最上面的支撑虚设基板的所述上表面。13.根据权利要求11所述的半导体封装,其中所述多个支撑虚设基板的垂直高度彼此相等。14.根据权利要求11所述的半导体封装,其中所述多个支撑虚设基板当中的最上面的支撑虚设基板的垂直高度小于所述多个支撑虚设基板当中的所述剩余的支撑虚设基板中的每个的垂直高度,其中所述多个支撑虚设基板当中的除了所述最上面的支撑虚设基板以外的所述剩余的支撑虚设基板的垂直高度彼此相等。

15.根据权利要求11所述的半导体封装,其中所述支撑接合绝缘层与所述多个第二贯通电极间隔开而不接触。16.根据权利要求11所述的半导体封装,其中所述多个支撑虚设基板中的每个具有彼此相同的水平宽度,该水平宽度小于所述多个dram管芯的水平宽度。17.根据权利要求11所述的半导体封装,其中填充在所述多个dram管芯当中的所述最上面的dram管芯的上表面和所述多个支撑虚设基板当中的最下面的支撑虚设基板之间的所述支撑接合绝缘层具有突出高过边缘部分的中心部分并具有平坦的下表面。18.一种半导体封装,包括:高带宽存储器(hbm)控制器管芯,包括具有彼此相反的有源表面和无源表面的第一半导体基板,所述hbm控制器管芯包括穿透所述第一半导体基板的至少一部分的多个第一贯通电极,所述hbm控制器管芯具有第一水平宽度和第一垂直高度;多个动态随机存取存储器(dram)管芯,包括具有彼此相反的有源表面和无源表面的第二半导体基板,所述第二半导体基板的所述有源表面面对所述第一半导体基板的所述无源表面并堆叠在第一半导体芯片上,所述多个dram管芯每个具有小于所述第一水平宽度的第二水平宽度、和第二垂直高度;多个接合焊盘,布置在所述hbm控制器管芯和所述多个dram管芯之间;芯片接合绝缘层,被配置为围绕所述多个接合焊盘并布置在所述hbm控制器管芯和所述多个dram管芯之间;多个支撑虚设基板,具有附接到其每个下表面的支撑接合绝缘层并依次堆叠在所述多个dram管芯上,并且每个支撑虚设基板具有小于所述第二水平宽度的第三水平宽度、以及等于或小于所述第一垂直高度和所述第二垂直高度的第三垂直高度;以及封装模制层,覆盖所述hbm控制器管芯的上表面、所述多个dram管芯的侧表面和所述多个支撑虚设基板的侧表面,但暴露所述多个支撑虚设基板当中最上面的支撑虚设基板的上表面而不覆盖所述最上面的支撑虚设基板的所述上表面,其中所述多个支撑虚设基板的总垂直高度大于所述第一垂直高度和所述第二垂直高度。19.根据权利要求18所述的半导体封装,其中所述第三垂直高度为约50μm至约90μm,其中所述多个支撑虚设基板的所述总垂直高度为约100μm至约500μm。20.根据权利要求18所述的半导体封装,其中所述多个接合焊盘包括含有cu的材料,其中所述芯片接合绝缘层和所述支撑接合绝缘层中的每个包括硅氧化物。

技术总结

一种半导体封装包括第一半导体芯片,第一半导体芯片包括第一半导体基板和穿透第一半导体基板的至少一部分的多个第一贯通电极。多个第二半导体包括第二半导体基板,所述多个第二半导体芯片堆叠在第一半导体芯片上。多个接合焊盘布置在第一半导体芯片和所述多个第二半导体芯片之间。芯片接合绝缘层布置在第一半导体芯片和所述多个第二半导体芯片之间。至少一个支撑虚设基板堆叠在所述多个第二半导体芯片上并具有布置在其下表面上的支撑接合绝缘层。缘层。缘层。

技术研发人员:池永根 姜芸炳 李相勋 李忠善

受保护的技术使用者:三星电子株式会社

技术研发日:2022.08.03

技术公布日:2023/3/10

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。