技术特征:

1.一种系统,包括:半导体器件单元,设置在碳化硅(sic)半导体层的表面,其中所述半导体器件单元包括:漂移区,具有第一导电类型;阱区,具有第二导电类型,设置成与所述漂移区相邻;源区,具有所述第一导电类型,设置成与所述阱区相邻;沟道区,具有所述第二导电类型,设置成包围所述源区并且接近所述表面;以及体接触件区,具有所述第二导电类型,设置在所述阱区的一部分之上,其中所述体接触件区没有在所述半导体器件单元中居中;以及分段源和体接触件(ssbc),设置在所述表面的一部分之上,其中所述ssbc包括:体接触件部分,设置在所述体接触件区之上;以及源接触件部分,设置成与所述体接触件区相邻并且在所述源区的一部分之上,其中所述源接触件部分沿所述ssbc的所述体接触件部分的仅一侧或仅两侧设置。2.如权利要求1所述的系统,其中,所述ssbc具有少于与所述表面垂直的对称的两个不同镜平面。3.如权利要求1所述的系统,其中,所述源接触件部分的第一节段和第二节段设置在所述体接触件部分的相对侧上。4.如权利要求1所述的系统,其中,所述ssbc的所述体接触件部分的至少一侧设置成接近没有设置在所述ssbc之下的所述源区的一部分。5.如权利要求1所述的系统,其中,所述体接触件区基本上是菱形形状。6.如权利要求1所述的系统,其中,所述体接触件区基本上是方形形状。7.如权利要求1所述的系统,其中,所述半导体器件单元包括场晶体管、绝缘栅双极晶体管(igbt)、绝缘基mos控制晶闸管(ibmct)、结型场效应晶体管(jfet)或者金属半导体场效应晶体管(mesfet)。8.一种系统,包括:蜂窝半导体器件布局,包括设置在碳化硅(sic)半导体层的表面的多个半导体器件单元,其中所述多个蜂窝半导体器件单元各包括:漂移区,具有第一导电类型;阱区,具有第二导电类型,设置成与所述漂移区相邻,其中所述阱区包括设置成接近所述表面的体接触件区;源区,具有所述第一导电类型,设置成与所述阱区相邻,其中所述源区包括设置成接近所述表面并且接近所述体接触件区的源接触件区;沟道区,具有所述第二导电类型,设置成包围所述源区并且接近所述表面;以及不对称分段源和体接触件(ssbc),设置在所述表面的一部分之上,其中所述不对称ssbc包括:体接触件部分,设置在所述半导体器件单元的所述体接触件区之上;以及源接触件部分,设置成与所述体接触件部分相邻并且在所述半导体器件单元的所述源接触件区之上,其中所述不对称ssbc的所述源接触件部分沿所述不对称ssbc的所述体接触件部分的仅一侧或仅两侧设置。

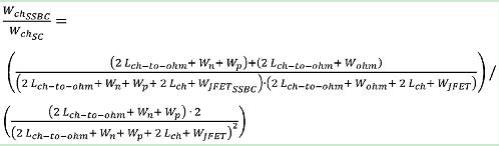

9.如权利要求8所述的系统,其中,所述蜂窝半导体器件布局配置成使得(2l

ch-to-ohm

w

ohm

)大于(2l

ch

w

jfet

)或者使得(2l

ch

2l

ch-to-ohm

w

ohm

)大于w

jfet

或者使得(2l

ch-to-ohm

w

ohm

)大于(2l

ch

w

jfet

)并且(2l

ch

2l

ch-to-ohm

w

ohm

)大于w

jfet

,其中l

ch

是沟道长度,l

ch-to-ohm

是欧姆区的长度,w

ohm

是所述欧姆区的宽度,以及w

jfet

是所述多个蜂窝半导体器件单元的jfet区的宽度。10.如权利要求8所述的系统,其中,所述蜂窝半导体器件布局配置成使得((4l

ch-to-ohm

w

n

w

p

w

ohm

)

·

(2l

ch

2l

ch-to-ohm

w

n

w

p

w

jfet

))大于(2

·

(2l

ch-to-ohm

w

n

w

p

)

·

(2l

ch

2l

ch-to-ohm

w

ohm

w

jfet

))或者使得((4l

ch

4l

ch-to-ohm

w

n

w

p

w

ohm

)

·

(2l

ch

2l

ch-to-ohm

w

n

w

p

w

jfet

)) 大于(2(2l

ch

2l

ch-to-ohm

w

n

w

p

)

·

(2l

ch

2l

ch-to-ohm

w

ohm

w

jfet

))或者使得((4l

ch-to-ohm

w

n

w

p

w

ohm

)

·

(2l

ch

2l

ch-to-ohm

w

n

w

p

w

jfet

))大于(2

·

(2l

ch-to-ohm

w

n

w

p

)

·

(2l

ch

2l

ch-to-ohm

w

ohm

w

jfet

))并且((4l

ch

4l

ch-to-ohm

w

n

w

p

w

ohm

)

·

(2l

ch

2l

ch-to-ohm

w

n

w

p

w

jfet

)) 大于(2(2l

ch

2l

ch-to-ohm

w

n

w

p

)

·

(2l

ch

2l

ch-to-ohm

w

ohm

w

jfet

)),其中l

ch

是沟道长度,l

ch-to-ohm

是欧姆区的长度,w

ohm

是所述欧姆区的宽度,w

n

是所述源接触件区的宽度,w

p

是所述体接触件区的宽度,以及w

jfet

是所述多个蜂窝半导体器件单元的jfet区的宽度。11.如权利要求8所述的系统,其中,所述蜂窝半导体器件布局包括布置成行、成列或者两者的所述多个半导体器件单元,并且所述行或列相互偏离。12.如权利要求8所述的系统,其中,各不对称ssbc没有与其相应半导体器件单元的中心对齐。13.一种在碳化硅(sic)半导体层的表面处制作半导体器件单元的方法,包括:在所述sic半导体层的所述表面之上形成半导体器件单元的分段源和体接触件(ssbc),其中所述ssbc包括:体接触件部分,设置在所述半导体层的所述表面之上并且接近所述半导体器件单元的体接触件区,其中所述体接触件部分没有与所述半导体器件单元的中心对齐;以及源接触件部分,设置在所述半导体层的所述表面之上并且接近所述半导体器件单元的源接触件区,其中所述源接触件部分沿所述ssbc的所述体接触件部分的仅一侧或仅两侧设置,其中,所述半导体器件单元包括具有第一导电类型的源区和具有第二导电类型的沟道区,所述沟道区设置成包围所述源区并且接近所述表面。14.如权利要求13所述的方法,其中,所述ssbc具有少于与所述表面垂直的对称的两个平面。15.如权利要求13所述的方法,其中,所述ssbc没有与所述表面垂直的对称的两个平面。

技术总结

本发明题为半导体器件的蜂窝布局。一种制作在碳化硅(SiC)半导体层的表面的半导体器件单元的方法包括在SiC半导体层的表面之上形成半导体器件单元的分段源和体接触件(SSBC)。SSBC包括体接触件部分,其设置在半导体层的表面之上并且接近半导体器件单元的体接触件区,其中体接触件部分没有设置在半导体器件单元的中心之上。SSBC还包括源接触件部分,其设置在半导体层的表面之上并且接近半导体器件单元的源接触件区,其中至少一个源接触件部分仅部分包围SSBC的体接触件部分。部分包围SSBC的体接触件部分。部分包围SSBC的体接触件部分。

技术研发人员:A.V.博罗特尼科夫 P.A.罗西

受保护的技术使用者:通用电气公司

技术研发日:2015.06.24

技术公布日:2023/1/31

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。