1.本发明涉及一种布线电路基板的制造方法。

背景技术:

2.以往,公开了如下的布线电路基板的制造方法:通过溅镀或电镀在金属支承基板之上形成金属薄膜,通过电镀在该金属薄膜之上形成金属箔,在金属箔和金属支承基板之上依次形成基底绝缘层、导体图案以及覆盖绝缘层(例如,参照下述专利文献1)。

3.在布线电路基板的制造方法中,为了提高金属箔与金属支承基板的密合性,在金属箔与金属支承基板之间形成有金属薄膜。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开2006-245220号公报

技术实现要素:

7.发明要解决的问题

8.在专利文献1所述那样的布线电路基板的制造方法中,在金属箔与金属薄膜的界面、以及金属薄膜与金属支承基板的界面产生电阻,难以降低金属箔与金属支承基板之间的电阻。

9.例如,存在希望将导体图案的局部经由金属箔接地的情况等、希望实现金属箔与金属支承基板之间的电阻的降低的情况。

10.本发明提供一种在相对于绝缘层而言与导体图案相反的一侧具有导体层和金属层的布线电路基板中,能够实现导体层与金属层之间的电阻的降低的布线电路基板的制造方法。

11.用于解决问题的方案

12.本发明[1]包括一种布线电路基板的制造方法,其包括:第1准备工序,在该工序中,准备具有绝缘层和配置于所述绝缘层的一侧的面上的导体层的第1基材;第2准备工序,在该工序中,准备具有金属层的第2基材;接合工序,在该工序中,以所述导体层与所述金属层接触的方式层叠所述第1基材与所述第2基材,对所述导体层和所述金属层进行金属接合;以及图案形成工序,在该工序中,在所述绝缘层的另一侧的面上形成导体图案,在所述接合工序之后执行所述图案形成工序,或者在所述图案形成工序之后执行所述接合工序。

[0013]

根据这样的方法,能够得到对导体层与金属层进行了金属接合的布线电路基板。

[0014]

因此,能够实现导体层与金属层之间的电阻的降低。

[0015]

本发明[2]在上述[1]的布线电路基板的制造方法的基础上,在所述接合工序中,通过界面接合将所述导体层与所述金属层接合。

[0016]

根据这样的方法,能够进一步实现导体层与金属层之间的电阻的降低。

[0017]

本发明[3]在上述[2]的布线电路基板的制造方法的基础上,在所述接合工序中,

通过固相接合将所述导体层与所述金属层接合。

[0018]

根据这样的方法,能够进一步实现导体层与金属层之间的电阻的降低。

[0019]

本发明[4]在上述[3]的布线电路基板的制造方法的基础上,在所述接合工序中,在真空下执行第1工序和第2工序,在第1工序中,使所述导体层的表面和所述金属层的表面活化,在第2工序中,将所述导体层的活化了的表面与所述金属层的活化了的表面接合。

[0020]

根据这样的方法,通过在真空下执行第1工序和第2工序,能够在抑制氧化和气体分子的吸附的同时使导体层的表面与金属层的表面活化并接合。

[0021]

因此,能够进一步实现导体层与金属层的界面处的电阻的降低。

[0022]

本发明[5]在上述[1]~[4]中任一项的布线电路基板的制造方法的基础上,在所述第1准备工序中,准备所述第1基材的卷材即第1卷材,在所述第2准备工序中,准备所述第2基材的卷材即第2卷材,在所述接合工序中,将从所述第1卷材送出的所述第1基材与从所述第2卷材送出的所述第2基材层叠。

[0023]

根据这样的方法,能够通过卷对卷方式将导体层与金属层接合,能够实现生产效率的提高。

[0024]

本发明[6]在上述[5]的布线电路基板的制造方法的基础上,在所述接合工序之后执行所述图案形成工序。

[0025]

根据这样的方法,与在图案形成工序之后执行接合工序的情况相比,在接合工序中不必考虑导体图案的变形等,能够将导体层与金属层可靠地接合。

[0026]

本发明[7]在上述[1]~[6]中任一项的布线电路基板的制造方法的基础上,所述导体层包括铜,所述金属层包括铜合金。

[0027]

根据这样的方法,能够实现包括铜的导体层与包括铜合金的金属层之间的电阻的降低。

[0028]

本发明[8]在上述[1]~[7]中任一项的布线电路基板的制造方法的基础上,所述导体图案具有:接地图案,其与所述导体层电连接;以及布线图案,其与所述导体层绝缘。

[0029]

根据这样的方法,能够实现金属层与连接有接地图案的导体层之间的电阻的降低。

[0030]

发明的效果

[0031]

根据本发明的布线电路基板的制造方法,能够实现导体层与金属层之间的电阻的降低。

附图说明

[0032]

图1是表示布线电路基板的一例的俯视图。

[0033]

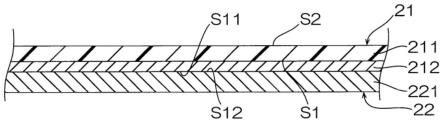

图2是图1的a-a剖视图。

[0034]

图3a~图3f是用于说明布线电路基板的制造方法的第1实施方式的说明图,图3a表示准备第1基材和第2基材的工序(第1准备工序和第2准备工序),图3b表示将第1基材的导体层与第2基材的金属层接合的工序(接合工序),图3c表示在绝缘层形成通孔的工序,图3d表示形成导体图案的工序(图案形成工序),图3e表示形成覆盖绝缘层的工序,图3f表示对金属层和导体层进行蚀刻的工序(蚀刻工序)。

[0035]

图4是用于说明接合工序的详细情况的说明图。

[0036]

图5a~图5f是用于说明布线电路基板的制造方法的第2实施方式的说明图,图5a表示准备第1基材的工序(第1准备工序),图5b表示在绝缘层形成通孔的工序,图5c表示形成导体图案的工序(图案形成工序),图5d表示形成覆盖绝缘层的工序,图5e表示准备第2基材(第2准备工序)并将第1基材的导体层与第2基材的金属层接合的工序(接合工序),图5f表示对金属层和导体层进行蚀刻的工序(蚀刻工序)。

[0037]

图6a~图6d是用于说明布线电路基板的制造方法的第3实施方式的说明图,图6a接着图5d表示对导体层进行蚀刻的工序(第1蚀刻工序),图6b表示准备第2基材的工序(第2准备工序),图6c表示对金属层进行蚀刻的工序(第2蚀刻工序),图6d表示将第1基材的导体层与第2基材的金属层接合的工序(接合工序)。

[0038]

附图标记说明

[0039]

1、布线电路基板;12、导体图案;12a、布线图案;12b、布线图案;12c、布线图案;12d、布线图案;12e、接地图案;21、第1基材;22、第2基材;211、绝缘层;212、导体层;221、金属层;r1、第1卷材;r2、第2卷材;s1、绝缘层的一侧的面;s2、绝缘层的另一侧的面;s11、导体层的表面;s12、金属层的表面。

具体实施方式

[0040]

1.布线电路基板

[0041]

如图1所示,布线电路基板1沿第1方向和第2方向延伸。在本实施方式中,布线电路基板1具有大致矩形形状。另外,布线电路基板1的形状没有限定。

[0042]

如图2所示,布线电路基板1具有基底绝缘层11、导体图案12、多个导体层13a、13b、13c、13d、13e、多个金属层14a、14b、14c、14d、14e以及覆盖绝缘层15。

[0043]

(1)基底绝缘层

[0044]

基底绝缘层11在厚度方向上配置于导体图案12与导体层13a、13b、13c、13d、13e之间。厚度方向与第1方向以及第2方向正交。基底绝缘层11将布线图案12a、12b、12c、12d与导体层13a、13b、13c、13d绝缘。关于布线图案12a、12b、12c、12d的说明见后述。基底绝缘层11由树脂形成。作为树脂,能够举出例如聚酰亚胺、马来酰亚胺、环氧树脂、聚苯并噁唑以及聚酯。基底绝缘层11在厚度方向上具有一侧的面s1和另一侧的面s2。

[0045]

(2)导体图案

[0046]

导体图案12在厚度方向上配置在基底绝缘层11的另一侧的面s2上。导体图案12由金属构成。作为金属,能够举出例如铜、银、金、铁、铝、铬以及它们的合金。从得到良好的电特性的观点出发,优选举出铜。导体图案12的形状没有限定。

[0047]

如图1所示,导体图案12具有多个布线图案12a、12b、12c、12d和接地图案12e。

[0048]

(2-1)布线图案

[0049]

布线图案12a具有端子121a、端子122a以及布线123a。布线图案12a将连接于端子121a的电子部件与连接于端子122a的电子部件电连接。

[0050]

端子121a配置于布线电路基板1的第1方向上的一端部。端子121a具有方形焊盘形状。

[0051]

端子122a配置于布线电路基板1的第1方向上的另一端部。端子122a具有方形焊盘形状。

[0052]

布线123a的一端与端子121a连接。布线123a的另一端与端子122a连接。布线123a将端子121a与端子122a电连接。

[0053]

对于布线图案12b、12c、12d,都能够与布线图案12a同样地进行说明。因此,省略关于布线图案12b、12c、12d各自的说明。

[0054]

(2-2)接地图案

[0055]

接地图案12e具有接地端子121e和接地布线122e。接地图案12e将连接于接地端子121e的电子部件经由导体层13e接地。

[0056]

接地端子121e配置于布线电路基板1的第1方向上的一端部。接地端子121e具有方形焊盘形状。端子121a、121b、121c、121d以及接地端子121e彼此隔有间隔地在第2方向上排列。

[0057]

接地布线122e的一端与接地端子121e连接。接地布线122e的另一端经过基底绝缘层11的通孔11a(参照图2)与导体层13e连接。

[0058]

(3)导体层

[0059]

如图2所示,导体层13a、13b、13c、13d、13e在厚度方向上配置在基底绝缘层11的一侧的面s1上。导体层13a、13b、13c、13d、13e由金属构成。作为金属,能够举出例如铜、银、金、铁、铝、铬以及它们的合金。从得到良好的电特性的观点出发,优选举出铜。导体层13a、13b、13c、13d、13e与布线图案12a、12b、12c、12d以及接地图案12e相对应地,彼此隔有间隔地在第2方向上排列。

[0060]

详细而言,导体层13a在厚度方向上配置于相对于基底绝缘层11而言与布线图案12a相反的一侧。导体层13a沿着布线图案12a延伸。导体层13a减少布线图案12a的传输损失。

[0061]

导体层13b在厚度方向上配置于相对于基底绝缘层11而言与布线图案12b相反的一侧。导体层13b沿着布线图案12b延伸。导体层13b减少布线图案12b的传输损失。

[0062]

导体层13c在厚度方向上配置于相对于基底绝缘层11而言与布线图案12c相反的一侧。导体层13c沿着布线图案12c延伸。导体层13c减少布线图案12c的传输损失。

[0063]

导体层13d在厚度方向上配置于相对于基底绝缘层11而言与布线图案12d相反的一侧。导体层13d沿着布线图案12d延伸。导体层13d减少布线图案12d的传输损失。

[0064]

导体层13e与接地图案12e电连接。如图1所示,导体层13e具有布线部131e和端子部132e。布线部131e的一端与接地布线122e连接。布线部131e的另一端与端子部132e连接。端子部132e配置于布线电路基板1的第1方向上的一端部。端子部132e具有方形焊盘形状。

[0065]

(4)金属层

[0066]

如图2所示,金属层14a、14b、14c、14d、14e与导体层13a、13b、13c、13d、13e相对应地,彼此隔有间隔地在第2方向上排列。金属层14a、14b、14c、14d、14e由金属构成。作为金属,能够举出例如不锈钢和铜合金。

[0067]

详细而言,金属层14a在厚度方向上配置于相对于导体层13a而言与布线图案12a相反的一侧。金属层14a与导体层13a接合。金属层14a支承导体层13a和布线图案12a。

[0068]

金属层14b在厚度方向上配置于相对于导体层13b而言与布线图案12b相反的一侧。金属层14b与导体层13b接合。金属层14b支承导体层13b和布线图案12b。

[0069]

金属层14c在厚度方向上配置于相对于导体层13c而言与布线图案12c相反的一

侧。金属层14c与导体层13c接合。金属层14c支承导体层13c和布线图案12c。

[0070]

金属层14d在厚度方向上配置于相对于导体层13d而言与布线图案12d相反的一侧。金属层14d与导体层13d接合。金属层14d支承导体层13d和布线图案12d。

[0071]

金属层14e在厚度方向上配置于相对于导体层13e而言与接地图案12e相反的一侧。金属层14e与导体层13e接合。金属层14e支承导体层13e和接地图案12e。

[0072]

(5)覆盖绝缘层

[0073]

如图1所示,覆盖绝缘层15覆盖布线123a、123b、123c、123d以及接地布线122e。覆盖绝缘层15在厚度方向上配置在基底绝缘层11的另一侧的面s2上。此外,覆盖绝缘层15不覆盖端子121a、121b、121c、121d、端子122a、122b、122c、122d以及接地端子121e。覆盖绝缘层15由树脂构成。作为树脂,能够举出例如聚酰亚胺、马来酰亚胺、环氧树脂、聚苯并噁唑以及聚酯。

[0074]

2.布线电路基板的制造方法

[0075]

接下来,对布线电路基板1的制造方法的第1实施方式进行说明。

[0076]

如图3a~图3f所示,布线电路基板1的制造方法包括第1准备工序(参照图3a)、第2准备工序(参照图3a)、接合工序(参照图3b)、图案形成工序(参照图3d)、蚀刻工序(参照图3f)以及外形加工工序。

[0077]

(1)第1准备工序

[0078]

如图3a所示,在第1准备工序中,准备第1基材21。在本实施方式中,在第1准备工序中,准备第1基材21的卷材即第1卷材r1(参照图4)。第1基材21具有绝缘层211和导体层212。

[0079]

绝缘层211是上述的基底绝缘层11的材料。绝缘层211由树脂构成。作为树脂,能够举出例如聚酰亚胺、马来酰亚胺、环氧树脂、聚苯并噁唑以及聚酯。绝缘层211在厚度方向上具有一侧的面s1和另一侧的面s2。

[0080]

导体层212是上述的导体层13a、13b、13c、13d、13e的材料。导体层212配置在绝缘层211的一侧的面s1上。导体层212由金属构成。作为金属,能够举出例如铜、银、金、铁、铝、铬以及它们的合金。从得到良好的电特性的观点出发,导体层212优选包括铜。即,第1基材21优选为覆铜层叠板。

[0081]

(2)第2准备工序

[0082]

在第2准备工序中,准备第2基材22。在本实施方式中,在第2准备工序中,准备第2基材22的卷材即第2卷材r2(参照图4)。第2基材22具有金属层221。在本实施方式中,第2基材22仅由金属层221构成。

[0083]

金属层221是上述的金属层14a、14b、14c、14d、14e的材料。金属层221由金属构成。作为金属,能够举出例如不锈钢和铜合金。金属层221优选包括铜合金。

[0084]

(3)接合工序

[0085]

接着,如图3b所示,在接合工序中,以导体层212与金属层221接触的方式层叠第1基材21和第2基材22,对导体层212与金属层221进行金属接合。在接合工序中,优选通过界面接合、更优选通过固相接合来接合导体层212与金属层221。

[0086]

在本实施方式中,如图4所示,在接合工序中,将从第1卷材r1送出的第1基材21与从第2卷材r2送出的第2基材22层叠(卷对卷方式)。详细而言,在接合工序中,在真空下执行以下说明的第1工序和第2工序。

[0087]

另外,“真空”是指,由比通常的大气压低的压力的气体充满的空间内的状态(jis z 8126-1:1999)。更详细而言,“真空”是指,由比标准气压低的压力的气体充满的空间内的状态。从抑制导体层212和金属层221的氧化、以及气体分子向导体层212和金属层221的吸附的观点出发,真空度越高越优选。

[0088]

第1工序和第2工序例如在高真空(10-1

~10-5

pa)下执行,优选在超高真空(10-5

pa以下)下执行。

[0089]

在第1工序中,使导体层212的表面s11(参照图3a)和金属层221的表面s12(参照图3a)活化。

[0090]

为了使导体层212的表面s11活化,利用第1离子蚀刻装置31对从第1卷材r1送出的第1基材21的导体层212的表面s11进行离子蚀刻。例如,利用第1离子蚀刻装置31对从第1卷材r1送出的第1基材21的导体层212的表面s11照射氩离子束。由此,导体层212的表面s11上的氧化物、吸附物被去除,导体层212的表面s11活化。

[0091]

为了使金属层221的表面s12活化,利用第2离子蚀刻装置32对从第2卷材r2送出的第2基材22的金属层221的表面s12进行离子蚀刻。由此,金属层221的表面s12上的氧化物、吸附物被去除,金属层221的表面s12活化。

[0092]

接着,在第2工序中,将导体层212的活化了的表面s11与金属层221的活化了的表面s12接合。

[0093]

具体而言,以导体层212的活化了的表面s11与金属层221的活化了的表面s12接触的方式将第1基材21与第2基材22合在一起,利用压制装置33进行压制。

[0094]

于是,如图3b所示,导体层212的表面s11与金属层221的表面s12接合。

[0095]

通过在真空下执行第1工序和第2工序,从导体层212的表面s11和金属层221的表面s12去除氧化物、吸附物,因此,能够进一步实现导体层212与金属层221的界面处的电阻的降低。另外,能够进一步实现导体层212与金属层221的密合性的提高。

[0096]

(4)图案形成工序

[0097]

接着,在本实施方式中,在接合工序之后执行图案形成工序。由此,与如后述的第2实施方式以及第3实施方式那样在图案形成工序之后执行接合工序的情况相比,在接合工序中不必考虑导体图案12的变形等,能够将导体层212与金属层221可靠地接合。特别适合于以卷对卷方式执行接合工序的情况。

[0098]

在图案形成工序中,在绝缘层211的另一侧的面s2上形成导体图案12。

[0099]

具体而言,如图3c所示,首先,根据需要在绝缘层211形成通孔11a。在本实施方式中,形成通孔11a以便连接接地图案12e(参照图2)与导体层13e(参照图2)。

[0100]

接着,在本实施方式中,如图3d所示,通过化学镀在绝缘层211的另一侧的面s2上形成导体图案12。即,通过加成法形成导体图案12。导体图案12具有与导体层212电连接的接地图案12e以及与导体层212绝缘的布线图案12a、12b、12c、12d。此外,导体图案12也可以通过减成法形成。

[0101]

接着,如图3e所示,在绝缘层211的另一侧的面s2上形成上述的覆盖绝缘层15。

[0102]

(5)蚀刻工序

[0103]

接下来,如图3f所示,对金属层221和导体层212进行蚀刻,形成上述的导体层13a、13b、13c、13d、13e以及金属层14a、14b、14c、14d、14e。

[0104]

(6)外形加工工序

[0105]

接着,如图2所示,将绝缘层211外形加工成预定的形状,得到上述的布线电路基板1。外形加工的方法没有限定。作为外形加工的方法,能够举出例如蚀刻和切断。

[0106]

3.作用效果

[0107]

(1)根据布线电路基板1的制造方法,如图2所示,能够得到对导体层13a、13b、13c、13d、13e与金属层14a、14b、14c、14d、14e进行了金属接合的布线电路基板1。

[0108]

因此,能够实现导体层13a、13b、13c、13d、13e与金属层14a、14b、14c、14d、14e之间的电阻的降低。

[0109]

(2)根据布线电路基板1的制造方法,在接合工序(参照图3b)中,通过界面接合将导体层212与金属层221接合。

[0110]

因此,能够进一步实现导体层13a、13b、13c、13d、13e与金属层14a、14b、14c、14d、14e之间的电阻的降低。

[0111]

(3)根据布线电路基板1的制造方法,在接合工序(参照图3b)中,通过固相接合将导体层212与金属层221接合。

[0112]

因此,能够进一步实现导体层13a、13b、13c、13d、13e与金属层14a、14b、14c、14d、14e之间的电阻的降低。

[0113]

(4)根据布线电路基板1的制造方法,如图4所示,在接合工序中,在真空下执行第1工序和第2工序,在该第1工序中,利用第1离子蚀刻装置31使导体层212的表面s11活化,利用第2离子蚀刻装置32使金属层221的表面s12活化,在该第2工序中,利用压制装置33将导体层212的活化了的表面s11与金属层221的活化了的表面s12接合。

[0114]

通过在真空下执行第1工序和第2工序,能够在抑制氧化和气体分子的吸附的同时使导体层212的表面s11与金属层221的表面s12活化并接合。

[0115]

其结果是,能够进一步实现导体层212与金属层221的界面处的电阻的降低。

[0116]

(5)根据布线电路基板1的制造方法,如图4所示,在接合工序中,将从第1卷材r1送出的第1基材21与从第2卷材r2送出的第2基材22层叠。

[0117]

因此,能够通过卷对卷方式将导体层212与金属层221接合,能够实现生产效率的提高。

[0118]

(6)根据布线电路基板1的制造方法,如图3d所示,在接合工序(参照图3b)之后,执行图案形成工序。

[0119]

因此,与在图案形成工序之后执行接合工序的情况相比,在接合工序中不必考虑导体图案12的变形等,能够将导体层212与金属层221可靠地接合。

[0120]

(7)根据布线电路基板1的制造方法,如图2所示,在导体层212包括铜、金属层221包括铜合金的情况下,能够实现包括铜的导体层13a、13b、13c、13d、13e与包括铜合金的金属层14a、14b、14c、14d、14e之间的电阻的降低。

[0121]

(8)根据布线电路基板1的制造方法,如图2所示,能够实现金属层14e与连接有接地图案12e的导体层13e之间的电阻的降低。

[0122]

4.第2实施方式

[0123]

接着,对第2实施方式进行说明。在第2实施方式中,对与第1实施方式相同的构件标注相同的附图标记,并省略说明。

[0124]

如图5a~图5f所示,在第2实施方式中,在图案形成工序(参照图5c)之后,执行接合工序(参照图5e)。

[0125]

详细而言,首先,如图5a所示,准备具有绝缘层211和导体层212的第1基材21(第1准备工序)。

[0126]

接下来,在绝缘层211的另一侧的面s2上形成导体图案12。

[0127]

详细而言,如图5b所示,根据需要,在绝缘层211形成通孔11a。

[0128]

接着,如图5c所示,通过加成法或减成法在绝缘层211的另一侧的面s2上形成导体图案12(图案形成工序)。

[0129]

接下来,如图5d所示,在绝缘层211的另一侧的面s2上形成上述的覆盖绝缘层15。

[0130]

接着,如图5e所示,准备具有金属层221的第2基材22(第2准备工序),以导体层212与金属层221接触的方式层叠第1基材21与第2基材22,将导体层212与金属层221接合(接合工序)。

[0131]

接下来,如图5f所示,对金属层221和导体层212进行蚀刻,形成上述的导体层13a、13b、13c、13d、13e以及金属层14a、14b、14c、14d、14e(蚀刻工序)。

[0132]

然后,如图2所示,将绝缘层211外形加工成预定的形状(外形加工工序),得到上述的布线电路基板1。

[0133]

在第2实施方式中,也能够得到与上述的第1实施方式相同的作用效果。

[0134]

5.第3实施方式

[0135]

接着,对第3实施方式进行说明。在第3实施方式中,对与第2实施方式相同的构件标注相同的附图标记,并省略说明。

[0136]

在第3实施方式中,如图5a~图5d所示,与第2实施方式同样地,在执行了包括第1准备工序(参照图5a)和图案形成工序(参照图5c)的工序之后,如图6a所示,对导体层212进行蚀刻,形成上述的导体层13a、13b、13c、13d、13e(第1蚀刻工序)。

[0137]

接着,如图6b所示,准备具有金属层221的第2基材22(第2准备工序),如图6c所示,对金属层221进行蚀刻,形成上述的金属层14a、14b、14c、14d、14e(第2蚀刻工序)。

[0138]

然后,如图6d所示,以导体层13a、13b、13c、13d、13e与金属层14a、14b、14c、14d、14e接触的方式层叠第1基材21和第2基材22,将导体层13a、13b、13c、13d、13e与金属层14a、14b、14c、14d、14e接合(接合工序)。

[0139]

在第3实施方式中,也能够得到与上述的第1实施方式相同的作用效果。

[0140]

6.变形例

[0141]

(1)在上述的各实施方式中,准备了仅在绝缘层211的一侧的面s1具有导体层212的第1基材21,但第1基材21也可以在绝缘层211的一侧的面s1和另一侧的面s2分别具有导体层212。在该情况下,在图案形成工序中,通过减成法将另一侧的面s2上的导体层212图案化为导体图案12。

[0142]

(2)在上述的各实施方式中,通过卷对卷方式将第1基材21与第2基材22接合,但也可以将第1基材21的片与第2基材22的片接合。

[0143]

另外,上述发明是作为本发明的例示的实施方式而提供的,但这仅是例示,不能进行限定性的解释。对于该技术领域的技术人员而言显而易见的本发明的变形例包含在上述权利要求书中。

[0144]

产业上的可利用性

[0145]

本发明的布线电路基板的制造方法用于布线电路基板的制造。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。