磁存储设备

1.相关申请的交叉引用

2.本技术基于并且要求于2021年9月8日提交的日本专利申请号2021-146187和于2022年2月28日提交的美国专利申请号17/682667的优先权的权益,其整体内容通过引用并入本文。

技术领域

3.本文所描述的实施例一般涉及磁存储设备。

背景技术:

4.使用磁阻效应元件作为存储元件的磁存储设备是已知的。已经提出了用于将数据写入磁阻效应元件的各种方法。

技术实现要素:

5.各实施例提供了一种可以减小存储单元的大小的磁存储设备。

6.一般地,根据一个实施例,磁存储设备包括第一导体层、第二导体层、第三导体层和连接到第一导体层、第二导体层和第三导体层的三端式第一存储单元。第一存储单元包括第四导体层、第一磁阻效应元件、两端式第一开关元件和两端式第二开关元件。第四导体层包括连接到第一导体层的第一部分、连接到第二导体层的第二部分、以及连接到第三导体层的第三部分。第一磁阻效应元件被连接在第三导体层与第四导体层之间。第一开关元件被连接在第二导体层与第四导体层之间。第二开关元件被连接在第一导体层与第三导体层之间。

附图说明

7.图1是根据第一实施例的磁存储设备的框图。

8.图2是根据第一实施例的存储单元阵列的电路图。

9.图3是根据第一实施例的存储单元阵列的平面图。

10.图4是根据第一实施例的存储单元阵列的剖视图。

11.图5是根据第一实施例的磁阻效应元件和外围布线的剖视图。

12.图6是示出根据第一实施例的磁存储设备的开关元件的特性的示例的图。

13.图7是示出根据第一实施例的磁存储设备的开关元件的特性的示例的图。

14.图8是与根据第一实施例的磁存储设备中的写操作有关的电路图。

15.图9是与根据第一实施例的磁存储设备中的写操作有关的剖视图。

16.图10是与根据第一实施例的磁存储设备中的写操作有关的剖视图。

17.图11是与根据第一实施例的磁存储设备中的读操作有关的电路图。

18.图12是与根据第一实施例的磁存储设备中的读操作有关的剖视图。

19.图13是根据第一实施例的第一修改例的磁阻效应元件和外围布线的剖视图。

20.图14是与根据第一实施例的第一修改例的磁存储设备中的写操作有关的电路图。

21.图15是与根据第一实施例的第一修改例的磁存储设备中的写操作有关的电路图。

22.图16是与根据第一实施例的第一修改例的磁存储设备中的写操作有关的剖视图。

23.图17是根据第一实施例的第二修改例的磁阻效应元件和外围布线的剖视图。

24.图18是与根据第一实施例的第二修改例的磁存储设备中的写操作有关的电路图。

25.图19是与根据第一实施例的第二修改例的磁存储设备中的写操作有关的剖视图。

26.图20是根据第一实施例的第三修改例的存储单元阵列的平面图。

27.图21是根据第一实施例的第三修改例的磁阻效应元件和外围布线的剖视图。

28.图22是与根据第一实施例的第三修改例的磁存储设备中的写操作有关的电路图。

29.图23是与根据第一实施例的第三修改例的磁存储设备中的写操作有关的剖视图。

30.图24是根据第二实施例的存储单元阵列的电路图。

31.图25是根据第二实施例的存储单元阵列的平面图。

32.图26是根据第二实施例的存储单元阵列的剖视图。

33.图27是根据第三实施例的存储单元阵列的电路图。

34.图28是根据第三实施例的存储单元阵列的平面图。

35.图29是根据第三实施例的存储单元阵列的剖视图。

36.图30是根据第三实施例的存储单元阵列的剖视图。

37.图31是根据第四实施例的存储单元阵列的平面图。

38.图32是根据第五实施例的存储单元阵列的平面图。

39.图33是根据第六实施例的存储单元阵列的电路图。

40.图34是根据第六实施例的存储单元阵列的平面图。

具体实施方式

41.在下文中,参考附图描述某些示例实施例。在以下描述中,具有相同功能和配置的组件由共同的参考标记表示。当要相互区分具有共同参考标记的多个组件时,后缀被添加到共同参考标记上。当不需要区分这种组件时,仅使用共同参考标记,而不添加后缀。后缀并不限于下标和上标,并且包括例如小写字母、符号和索引,其意味着数组被添加到参考标记的末尾。

42.在本说明书中,磁存储设备是例如磁阻随机存取存储器(mram)。磁存储设备包括磁阻效应元件作为存储元件。磁阻效应元件是具有磁性隧道结(mtj)的磁阻效应的可变电阻元件。磁阻效应元件也被称为mtj元件。

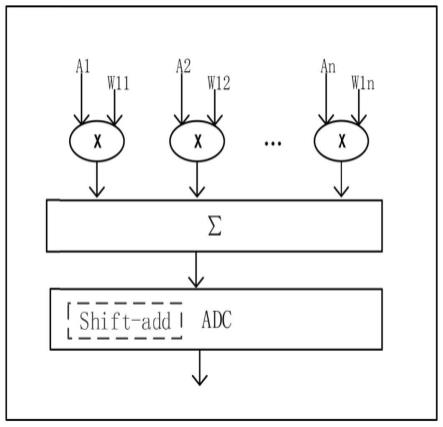

43.1.第一实施例

44.描述了第一实施例。

45.1.1配置

46.首先,描述根据第一实施例的磁存储设备的配置。

47.1.1.1磁存储设备

48.图1是示出根据第一实施例的磁存储设备的配置的示例的框图。磁存储设备1包括存储单元阵列10、行选择电路11、列选择电路12、解码电路13、写电路14、读电路15、电压产生电路16、输入/输出电路17和控制电路18。

49.存储单元阵列10是用于磁存储设备1中的数据的存储单元。存储单元阵列10包括多个存储单元mc。存储单元mc可以与包括行或列的组相关联。在相同行中的存储单元mc被连接到相同的字线wl,并且在相同列中的存储单元mc被连接到相同的读取位线rbl和相同的写入位线wbl。

50.行选择电路11用于选择存储单元阵列10的行。行控制电路11经由字线wl被连接到存储单元阵列10。来自解码电路13的地址add的解码结果(行地址)被提供给行选择电路11。行选择电路11基于地址add的解码结果来选择字线wl。除了选择字线wl之外的字线wl被称为非选择字线wl。

51.列选择电路12用于选择存储单元阵列10的列。列选择电路12经由读取位线rbl和写入位线wbl被连接到存储单元阵列10。来自解码电路13的地址add的解码结果(列地址)被提供给列选择电路12。列选择电路12基于地址add的解码结果来选择读取位线rbl和写入位线wbl。除了选择位线rbl之外的读取位线rbl被称为非选择位线rbl。除了选择写入位线wbl之外的写入位线wbl被称为非选择位线wbl。

52.解码电路13是对来自输入/输出电路17的地址add进行解码的解码器。解码电路13将来自地址add的解码结果提供给行选择电路11和列选择电路12。地址add包括所选择的列地址和所选择的行地址。

53.写电路14包括例如写入驱动器。写电路14将数据写入存储单元mc。

54.读电路15包括例如感测放大器。读电路15从存储单元mc读取数据。

55.电压产生电路16使用从磁存储设备1的外部提供的电源电压来产生用于存储单元阵列10的各种操作的电压。例如,电压产生电路16产生在写操作期间所需的各种电压,并将电压输出到写电路14。电压产生电路16产生在读操作期间所需的各种电压,并将这些电压输出到读电路15。

56.输入/输出电路17控制与磁存储设备1的外部的通信。输入/输出电路17将来自磁存储设备1的外部的地址add发送到解码电路13。输入/输出电路17将来自磁存储设备1的外部的命令cmd发送到控制电路18。输入/输出电路17在磁存储设备1的外部与控制电路18之间发送和接收各种控制信号cnt。输入/输出电路17将来自磁存储设备1的外部的数据dat发送到写电路14,并将从读电路15发送的数据dat输出到磁存储设备1的外部。

57.例如,控制电路18包括处理器(诸如中央处理单元(cpu))和只读存储器(rom)。控制电路18基于控制信号cnt和命令cmd来控制行选择电路11、列选择电路12、解码电路13、写电路14、读电路15、电压产生电路16和输入/输出电路17的操作。

58.1.1.2存储单元阵列

59.描述根据第一实施例的磁存储设备的存储单元阵列。

60.(电路配置)

61.图2是示出根据第一实施例的存储单元阵列的电路配置的示例的电路图。在图2中,字线wl、读取位线rbl和写入位线wbl通过被包括索引(“《》”)的后缀分类来描述。

62.存储单元阵列10包括多个存储单元mc、多个字线wl、多个读取位线rbl和多个写入位线wbl。在图2的示例中,多个存储单元mc包括(m 1)

×

(n 1)个存储单元mc《0,0》、mc《0,1》、...mc《0,n》、mc《1,0》、...和mc《m,n》(m和n是2或更大的整数)。在图2的示例中,提供了其中m和n是2或更大的整数的情况,但是实施例并不限于此。m和n可以是0或1。多个字线wl包

括(m 1)个字线wl《0》、wl《1》、...以及wl《m》。多个读取位线rbl包括(n 1)个读取位线rbl《0》、rbl《1》、...以及rbl《n》。多个写入位线wbl包括(n 1)个写入位线wbl《0》、wbl《1》、...以及wbl《n》。

63.多个存储单元mc在存储单元阵列10中被布置成矩阵配置。存储单元mc与包括多个字线wl之一和包括多个读取位线rbl和多个写入位线wbl之中的读取位线rbl和写入位线wbl的一个组的组相关联。也就是说,存储单元mc《i,j》(0≤i≤m,0≤j≤n)被连接到字线wl《i》、读取位线rbl《j》和写入位线wbl《j》。

64.存储单元mc《i,j》是三端式存储单元,其具有被连接到字线wl《i》的第一端、被连接到写入位线wbl《j》的第二端和被连接到读取位线rbl《j》的第三端。存储单元mc《i,j》包括开关元件sel1《i,j》和sel2《i,j》、磁阻效应元件mtj《i,j》和布线sotl《i,j》。

65.布线sotl《i,j》包括第一部分、第二部分以及在第一部分与第二部分之间的第三部分。布线sotl《i,j》的第一部分被连接到字线wl《i》。布线sotl《i,j》的第二部分被连接到写入位线wbl《j》。布线sotl《i,j》的第三部分被连接到读取位线rbl《j》。开关元件sel1《i,j》被连接在布线sotl《i,j》的第二部分与写入位线wbl《j》之间。磁阻效应元件mtj《i,j》被连接在布线sotl《i,j》的第三部分与读取位线rbl《j》之间。开关元件sel2《i,j》被连接在磁阻效应元件mtj《i,j》与读取位线rbl《j》之间。

66.开关元件sel1和sel2是两端式开关元件。两端式开关元件与诸如晶体管的三端式开关元件的不同之处在于,两端式开关元件不包括第三端子。当施加在两个端子之间的电压分别低于阈值电压vth1和vth2时,开关元件sel1和sel2处于“高电阻”状态或“关闭”状态,例如,非导电状态。当施加在两个端子之间的电压分别是阈值电压vth1和vth2或更高时,开关元件sel1和sel2改变到“低电阻”状态或“开启”状态,例如,导电状态。更具体地,例如,当施加到对应的存储单元mc的电压低于阈值电压vth1和vth2时,开关元件sel1和sel2作为具有大电阻值的绝缘体而切断电流(进入关闭状态)。当施加到对应的存储单元mc的电压高于阈值电压vth1和vth2时,开关元件sel1和sel2作为具有小电阻值的导体而允许电流流动(进入开启状态)。开关元件sel1和sel2根据被施加到对应的存储单元mc的电压的幅度来切换是切断还是使电流流动,而不管施加在两个端子之间的电压的极性如何(不管流动的电流的方向)。

67.布线sotl是存储单元mc中的电流路径。例如,当开关元件sel1处于开启状态并且开关元件sel2处于关闭状态时,布线sotl用作字线wl与写入位线wbl之间的电流路径。例如,当开关元件sel1处于关闭状态并且开关元件sel2处于开启状态时,布线sotl的一部分用作字线wl与读取位线rbl之间的电流路径。

68.磁阻效应元件mtj是可变电阻元件。磁阻效应元件mtj可以基于由开关元件sel1和sel2控制的路径的电流而将电阻值切换到低电阻状态和高电阻状态。磁阻效应元件mtj用作根据电阻状态的变化而非自愿存储数据的存储元件。

69.(平面布局)

70.描述根据第一实施例的存储单元阵列的平面布局。

71.图3是示出根据第一实施例的存储单元阵列的平面布局的示例的平面图。在图3中,省略了绝缘体层等的结构。

72.存储单元阵列10还包括多个垂直结构v1、多个垂直结构v2、以及多个垂直结构v3。

多个垂直结构v1中的每一个包括开关元件sel1。多个垂直结构v2中的每一个包括磁阻效应元件mtj和开关元件sel2。

73.多个写入位线wbl被布置在x方向上。多个写入位线wbl中的每一个在y方向上延伸。

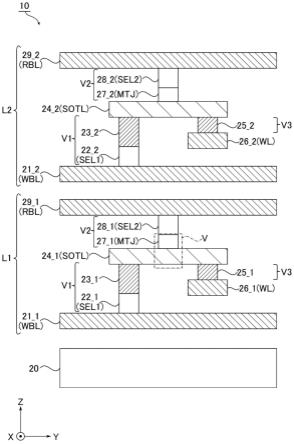

74.多个字线wl被提供在多个写入位线wbl的上方。多个字线wl被布置在y方向上。多个字线wl中的每一个在x方向上延伸。

75.多个布线sotl被提供在多个字线wl的上方。在平面图中,多个布线sotl中的每一个具有相对于x方向在y方向上延长的矩形形状。多个布线sotl中的每一个在y方向上延伸。在平面图中,多个布线sotl中的每一个对应于一个字线wl和一个写入位线wbl彼此重叠的位置,并且被提供为矩阵配置。

76.多个读取位线rbl被提供在多个布线sotl的上方。多个读取位线rbl被布置在x方向上。多个读取位线rbl中的每一个在y方向上延伸。在平面图中,多个读取位线rbl被分别提供在与多个写入位线wbl重叠的位置处。

77.多个垂直结构v1在z方向上延伸。在平面图中,多个垂直结构v1的每一个具有圆形形状。多个垂直结构v1中的每一个被连接在一个对应的写入位线wbl与一个对应的布线sotl之间。

78.多个垂直结构v2在z方向上延伸。在平面图中,垂直结构v2每一个具有圆形形状。每一个垂直结构v2被连接到一个对应的读取位线rbl和一个对应的布线sotl。

79.垂直结构v3在z方向上延伸。在平面图中,垂直结构v3每一个具有圆形形状。每一个垂直结构v3被连接到一个对应的字线wl和一个对应的布线sotl。

80.在如上所述的配置中,包括一个布线sotl以及连接到一个对应的布线sotl的一个垂直结构v1、一个垂直结构v2和一个垂直结构v3的组用作一个存储单元mc。

81.(剖面结构)

82.描述根据第一实施例的存储单元阵列的剖面结构。

83.图4是示出根据第一实施例的存储单元阵列的剖面结构的示例的剖视图,该剖视图沿着图3的线iv-iv取得。存储单元阵列10包括半导体衬底20和层级结构l1、l2。层级结构l1包括导体层21_1、23_1、24_1、25_1、26_1和29_1以及元件层22_1、27_1和28_1。层级结构l2包括导体层21_2、23_2、24_2、25_2、26_2和29_2以及元件层22_2、27_2和28_2。添加了后缀“_x”的配置指示属于层级结构lx(x是1或更大的整数)的配置。

84.层级结构l1和l2在半导体衬底20之上在z方向上按此顺序堆叠。层级结构l1和l2中的每一个对应于图3所示的平面布局。

85.诸如行选择电路11和列选择电路12的外围电路可以被提供在半导体衬底20与层级结构l1之间。在半导体衬底20与层级结构l1之间可以不形成电路。当在半导体衬底20与层级结构l1之间没有形成电路时,可以在半导体衬底20上位于层级结构l1的下方的部分中形成浅沟槽隔离(sti)。

86.描述层级结构l1。

87.导体层21_1被提供在半导体衬底20的上方。导体层21_1用作写入位线wbl。导体层21_1在y方向上延伸。

88.元件层22_1被提供在导体层21_1的上表面上。元件层22_1用作开关元件sel1。

89.导体层23_1被提供在元件层22_1的上表面上。导体层23_1用作接触。元件层22_1和导体层23_1配置垂直结构v1。

90.导体层24_1被提供在导体层23_1的上表面上。导体层24_1用作布线sotl。导体层24_1在y方向上延伸。

91.导体层25_1被提供在导体层24_1的下表面的与提供导体层23_1的部分不同的部分中。导体层25_1用作接触。导体层25_1配置垂直结构v3。

92.导体层26_1被提供在导体层25_1的下表面上。导体层26_1用作字线wl。导体层26_1在x方向上延伸。

93.元件层27_1被提供在导体层24_1的上表面的提供导体层23_1的部分与提供导体层25_1的部分之间的部分中。元件层27_1用作磁阻效应元件mtj。

94.元件层28_1被提供在元件层27_1的上表面上。元件层28_1用作开关元件sel2。元件层27_1和28_1配置垂直结构v2。

95.导体层29_1被提供在元件层28_1的上表面上。导体层29_1用作读取位线rbl。导体层29_1在y方向上延伸。

96.在如上所述的配置中,层级结构l1中的包括导体层24_1和垂直结构v1、v2和v3的一个组用作具有分别连接到导体层21_1、26_1和29_1的三个端子的一个存储单元mc。

97.层级结构l2具有与层级结构l1相同的配置。也就是说,导体层21_2、23_2、24_2、25_2、26_2和29_2以及元件层22_2、27_2和28_2分别具有与导体层21_1、23_1、24_1、25_1、26_1和29_1以及元件层22_1、27_1和28_1相同的结构和功能。因此,层级结构l2中的包括导体层24_2和垂直结构v1、v2和v3的一个组用作具有分别连接到导体层21_2、26_2和29_2的三个端子的一个存储单元mc。

98.1.1.3磁阻效应元件和外围布线

99.图5是图4的区域v的剖视图,其示出了根据第一实施例的磁阻效应元件和外围布线的剖面结构的示例。导体层24包括反铁磁层24a、铁磁层24b和非磁性层24c。元件层27包括铁磁层27a、非磁性层27b、铁磁层27c、非磁性层27d和铁磁层27e。

100.首先,描述导体层24的结构的细节。

101.反铁磁层24a是具有反铁磁性的导电膜。反铁磁层24a通过与铁磁层24b的交换耦合来稳定铁磁层24b的磁化方向。反铁磁层24a包含例如铂锰(ptmn)。

102.铁磁层24b被提供在反铁磁层24a的上表面上。铁磁层24b是具有铁磁性的导电膜。铁磁层24b在铁磁层24b延伸的方向(y方向)上包括易磁化轴向。除了形状各向异性之外,通过与反铁磁层24a的交换耦合来沿着y方向稳定铁磁层24b的磁化方向。根据在铁磁层24b中流动的电流的方向反转铁磁层24b的磁化方向。铁磁层24b包含例如钴铁(cofe)。

103.非磁性层24c被提供在铁磁层24b的上表面上。非磁性层24c是非磁性重金属导电膜。非磁性层24c通过流过非磁性层24c的电流来产生自旋轨道矩(sot)。自旋轨道矩被注入铁磁层27a。非磁性层24c还使得铁磁层24b和铁磁层27a经受层间交换耦合。非磁性层24c包含例如选自铂(pt)、钯(pd)、金(au)和银(ag)中的至少一种元素。

104.铁磁层27a被提供在非磁性层24c的上表面上。铁磁层27a是具有铁磁性的导电膜。铁磁层27a用作存储层sl。铁磁层27a在与膜表面垂直的方向(z方向)上包括易磁化轴向。通过在与非磁性层24c的界面上经由非磁性层24c与铁磁层24b的层间交换耦合,向铁磁层27a

施加y方向上的偏置磁场。在非磁性层24c上产生的自旋轨道矩被注入铁磁层27a。铁磁层27a的磁化方向被配置为基于y方向上的偏置磁场和自旋轨道矩来反转。

105.铁磁层27a包含铁(fe)。铁磁层27a还可包含钴(co)和镍(ni)中的至少一种元素。铁磁层27a还可包含硼(b)。更具体地,例如,铁磁层27a包含铁钴硼(fecob)或硼化铁(feb)。

106.非磁性层27b被提供在铁磁层27a的上表面上。非磁性层27b是非磁性绝缘膜。非磁性层27b用作隧道势垒层tb。非磁性层27b被提供在铁磁层27a与铁磁层27c之间,并且连同这两个铁磁层一起形成磁性隧道结。非磁性层27b用作种子材料以作为用于在铁磁层27a的结晶化过程中从与铁磁层27a的界面生长结晶膜的核。非磁性层27b具有其中膜表面朝着(001)平面取向的nacl晶体结构。非磁性层27b包含例如氧化镁(mgo)。

107.铁磁层27c被提供在非磁性层27b的上表面上。铁磁层27c是具有铁磁性的导电膜。铁磁层27c用作参考层rl。铁磁层27c在与膜表面垂直的方向(z方向)上具有易磁化轴向。铁磁层27c的磁化方向是固定的。在图5的示例中,铁磁层27c的磁化方向指向铁磁层27a。在该上下文中,表达“磁化方向是固定的”意味着磁化方向不被使铁磁层27a的磁化方向反转的幅度的转矩改变。铁磁层27c包含选自钴铂(copt)、钴镍(coni)、和钴钯(copd)中的至少一种化合物。

108.非磁性层27d被提供在铁磁层27c的上表面上。非磁性层27d是非磁性导电膜。非磁性层27d用作间隔层。非磁性层27d包含选自钌(ru)、锇(os)、铑(rh)、铱(ir)、钒(v)和铬(cr)中的至少一种元素。

109.铁磁层27e被提供在非磁性层27d的上表面上。铁磁层27e是具有铁磁性的导电膜。铁磁层27e用作移位消除层。铁磁层27e在与膜表面垂直的方向(z方向)上具有易磁化轴向。铁磁层27e包括例如选自钴铂(copt)、钴镍(coni)和钴钯(copd)中的至少一种化合物。

110.铁磁层27c和27e通过非磁层27d反铁磁地耦合。也就是说,铁磁层27c和27e被耦合以具有彼此反平行的磁化方向。铁磁层27c、非磁性层27d和铁磁层27e的这种耦合结构被称为合成反铁磁(saf)结构。通过saf结构,铁磁层27e可以抵消铁磁层27c的漏磁场在铁磁层27a的磁化方向上的影响。

111.取决于存储层sl和参考层rl的磁化方向的相对关系是平行还是反平行,磁阻效应元件mtj可以采取低电阻状态或高电阻状态。根据第一实施例,在不允许写入电流流过该磁阻效应元件mtj的情况下,控制存储层sl的磁化方向到参考层rl的磁化方向。具体地,采用了使用通过允许电流流经布线sotl而产生的自旋轨道矩的写入方法。

112.当在y方向上具有特定幅度的写入电流ic0流到布线sotl时,存储层sl和参考层rl在磁化方向上的相对关系变为平行。在该平行状态的情况下,磁阻效应元件mtj的电阻值最低,因此,磁阻效应元件mtj被设置为低电阻状态。该低电阻状态被称为“平行(p)状态”,并且在该示例中,对应于数据值“0”状态。

113.当大于写入电流ic0的写入电流ic1在与写入电流ic0相反的方向上流到布线sotl时,存储层sl和参考层rl在磁化方向上的相对关系变为反平行。在该反平行状态中,磁阻效应元件mtj的电阻值最高,并且磁阻效应元件mtj被设置为高电阻状态。该高电阻状态被称为“反平行(ap)状态”,并且在该示例中,对应于数据值“1”状态。

114.以下描述是根据上文所描述的数据值约定进行的,但本发明不限于该约定。例如,p状态可以是数据值“1”状态,ap状态可以是数据值“0”状态。

115.1.1.4开关元件

116.开关元件sel1主要在写操作期间从关闭状态切换到开启状态。相反,开关元件sel2主要在读操作期间从关闭状态切换到开启状态。以这种方式,对于开关元件sel1和sel2,从关闭状态到开启状态的切换定时是不同的。因此,开关元件sel1和sel2的适合的电流电压特性是彼此不同的。具体地,例如,开关元件sel1优选地具有带有折回(snapback)的电流电压特性。相反,开关元件sel2优选地具有无折回的电流电压特性。

117.图6和图7是示出根据第一实施例的开关元件的特性的示例的图。图6是具有带有折回的电流电压特性的开关元件sel1的电流电压特性的示例。图7是具有无折回的电流电压特性的开关元件sel2的电流电压特性的示例。

118.首先,参考图6描述带有折回的电流电压特性。

119.当施加到开关元件sel1的两端的电压(施加电压v1)从0v变为阈值电压vth1时,流过开关元件sel1的电流(电流i1)变为阈值电流ith1。阈值电流ith1是大约1μa,是可忽略地小。因此,在施加电压v1是0v到阈值电压vth1的范围内,开关元件sel1进入关闭状态。

120.当电流i1超过阈值电流ith1时,开关元件sel1进入开启状态,并且同时发生折回。折回是电压下降量从阈值电压vth1降低并且大于阈值电流ith1的电流流动的现象。当电流i1达到保持电流ihold1(》ith1)时,开关元件sel1的电压下降量变为保持电压vhold1(《vth1)。

121.当电压通过折回达到保持电压vhold1时,开关元件sel1的电压下降量处于几乎不被电流i1的增加而改变的状态。

122.以这种方式,在开关元件sel1中,进入开启状态时的电阻变为低于阈值电压vth1的保持电压vhold1。因此,当开关元件sel1进入开启状态时,容易允许更大的电流流动。

123.参考图7描述无折回的电流电压特性。

124.当施加到开关元件sel2的两端的电压(施加电压v2)从0v变为阈值电压vth2时,流过开关元件sel2的电流(电流i2)变为阈值电流ith2。阈值电流ith2变为大约1μa,是可忽略地小。因此,在施加电压v2从0v到阈值电压vth2的范围内,开关元件sel2进入关闭状态。

125.当电流i2超过阈值电流ith2时,开关元件sel2进入开启状态而不发生折回。因此,开关元件sel2的电压下降量进入几乎不被电流i2的增加而改变的状态。

126.以这种方式,当开关元件sel2进入开启状态时,电压下降量不会瞬时改变。因此,当开关元件sel2进入开启状态时,可以防止对串联连接到开关元件sel2的元件(例如,磁阻效应元件mtj)瞬时施加高电压。

127.1.2操作

128.描述根据第一实施例的磁存储设备的操作。

129.1.2.1写操作

130.图8是示出根据第一实施例的磁存储设备中的写操作的示例的电路图。在图8的示例中,示出了数据被写入多个存储单元mc之中的存储单元mc《m,n》(0《m《m,并且0《n《n)的情况。

131.当数据被写入存储单元mc《m,n》时,电压vdd或vss被施加到字线wl《m》和写入位线wbl《n》的每一个。当电压vdd被施加到字线wl《m》时,电压vss被施加到写入位线wbl《n》。当电压vss被施加到字线wl《m》时,电压vdd被施加到写入位线wbl《n》。电压vdd/2被施加到除

了字线wl《m》之外的所有字线wl、除了写入位线wbl《n》之外的所有写入位线wbl、以及所有读取位线rbl。

132.电压vss是参考电位。电压vss是例如0v。电压vdd(电位差vdd)到电压vss是使开关元件sel1和sel2进入开启状态的电压。电位差vdd是可以允许用于改变磁阻效应元件mtj的电阻状态的电流流动的电压。电位差vdd/2是使开关元件sel1和sel2进入关闭状态的电压。

133.因此,在字线wl《m》与写入位线wbl《n》之间出现电位差vdd。在字线wl《m》与除了写入位线wbl《n》之外的写入位线wbl之间产生电位差vdd/2。在字线wl《m》与读取位线rbl之间出现电位差vdd/2。

134.在除了字线wl《m》之外的字线wl与写入位线wbl《n》之间出现电位差vdd/2。

135.在写入位线wbl《n》与读取位线rbl《n》之间出现电位差vdd/2。

136.因此,开关元件sel1《m,n》进入开启状态。除了开关元件sel1《m,n》之外的开关元件sel1进入关闭状态。开关元件sel2《m,n》也进入关闭状态。

137.因此,可以允许电流流经布线sotl《m,n》,而不使电流流经除了布线sotl《m,n》之外的任何布线sotl。

138.在上文所描述的写操作中,存储单元mc《m,n》的状态可以被称为选择状态。存储单元mc《0,n》至mc《m-1,n》、mc《m 1,n》至mc《m,n》、mc《m,0》至mc《m,n-1》、以及mc《m,n 1》至mc《m,n》的状态可以被称为半选择状态。不是选择状态或半选择状态的存储器单元mc的状态可以被称为非选择状态。

139.图9和图10是示出根据第一实施例的磁存储设备中的写操作的示例的剖视图。在图9和图10中,示意性地示出了流到处于选择状态的存储单元mc的电流和磁阻效应元件mtj的磁化方向。图9对应于在写入数据“1”时的写操作。图10对应于在写入数据“0”时的写操作。

140.首先,参考图9描述数据“1”的写操作。在图9的示例中,示出了写入电流ic1从右侧的字线wl流向左侧的写入位线wbl的情况。

141.如上文所描述的,使开关元件sel1进入开启状态的电位差vdd在导体层24的两端出现。通过控制电位差vdd,写入电流ic1流入导体层24。通过使写入电流ic1流入导体层24,特别是流入非磁性层24c,产生使得铁磁层27a的磁化方向与铁磁层27c的磁化方向反平行的自旋轨道矩。自旋轨道矩被注入靠近非磁性层24c的铁磁层27a。

142.另外,铁磁层24b的磁化方向与写入电流ic1流动的方向匹配。因此,通过经由非磁性层24c与铁磁层24b的层间交换耦合产生的y方向上的偏置磁场被施加到铁磁层27a。

143.因此,通过自旋轨道矩和由交换耦合产生的y方向上的偏置磁场的辅助,铁磁层27a的磁化方向被反转到与铁磁层27c的磁化方向反平行的方向。

144.参考图10描述数据“0”的写操作。在图10的示例中,示出了写入电流ic0从写入位线wbl(在左侧)流向字线wl(在右侧)的情况。

145.如上文所描述的,使开关元件sel1进入开启状态的电位差vdd在导体层24的两端都产生。通过控制电位差vdd,写入电流ic0流入导体层24。通过写入电流ic0流入导体层24,特别是流入非磁性层24c,产生使得铁磁层27a的磁化方与铁磁层27c的磁化方向平行的自旋轨道矩。自旋轨道矩被注入靠近非磁性层24c的铁磁层27a中。

146.另外,铁磁层24b的磁化方向与写入电流ic0流动的方向匹配。因此,通过经由非磁

性层24c与铁磁层24b的层间交换耦合产生的y方向上的偏置磁场被施加到铁磁层27a。

147.因此,通过自旋轨道矩和由交换耦合产生的y方向上的偏置磁场的辅助,铁磁层27a的磁化方向被反转到与铁磁层27c的磁化方向平行的方向。

148.1.2.2读操作

149.图11是示出根据第一实施例的磁存储设备中的读操作的示例的电路图。在图11的示例中,与图8的情况一样,示出了从存储单元mc《m,n》读取数据的情况。

150.当从存储单元mc《m,n》读取数据时,电压vdd和vss被分别施加到读取位线rbl《n》和字线wl《m》。电压vdd/2被施加到除了字线wl《m》之外的所有字线wl、除了读取位线rbl《n》之外的所有读取位线rbl、以及所有写入位线wbl。

151.因此,在字线wl《m》与读取位线rbl《n》之间产生电位差vdd。在字线wl《m》与除了读取位线rbl《n》之外的读取位线rbl之间出现电位差vdd/2。在字线wl《m》与任何写入位线wbl之间出现电位差vdd/2。

152.在除了字线wl《m》之外的字线wl与读取位线rbl《n》之间出现电位差vdd/2。

153.在写入位线wbl《n》与读取位线rbl《n》之间出现电位差vdd/2。在(除了写入位线wbl《n》之外的)写入位线wbl与对应的读取位线rbl之间不会出现该电位差。

154.因此,开关元件sel2《m,n》进入开启状态。除了开关元件sel2《m,n》之外的所有开关元件sel2进入关闭状态。所有开关元件sel1《m,n》进入关闭状态。

155.因此,可以使电流流经磁阻效应元件mtj《m,n》,而不使电流流经除了磁阻效应元件mtj《m,n》之外的任何磁阻效应元件mtj。

156.在上文所描述的读操作中,存储单元mc《m,n》的状态也被称为选择状态。存储单元mc《0,n》至mc《m-1,n》、mc《m 1,n》至mc《m,n》、mc《m,0》至mc《m,n-1》、以及mc《m,n 1》至mc《m,n》的状态也被称为半选择状态。不是选择状态或半选择状态的存储器单元mc的状态被称为非选择状态。

157.图12是示出根据第一实施例的磁存储设备中的读操作的示例的剖视图。在图12中,示意性地示出了流到处于选择状态的存储单元mc的电流和磁阻效应元件mtj的磁化方向。在图12的示例中,示出了读取电流ir从磁阻效应元件mtj流向字线wl的情况。

158.如上文所描述的,使开关元件sel2进入开启状态的电位差vdd在元件层27的上端和导体层24的右端出现。通过控制电位差vdd,读取电流ir从元件层27的上端流向导体层24的右端。读取电流ir流入元件层27,因此,读电路15可以基于读取电流ir来确定元件层27是处于高电阻状态还是低电阻状态。另外,读取电流ir被控制为小于写入电流ic0和ic1。因此,可以防止非磁性层27b的介电击穿。

159.1.3.根据第一实施例的效果

160.根据第一实施例,布线sotl包括连接到字线wl的第一部分、连接到写入位线wbl的第二部分和连接到读取位线rbl的第三部分。磁阻效应元件mtj被连接在布线sotl的第三部分与读取位线rbl之间。开关元件sel1被连接在布线sotl的第二部分与写入位线wbl之间。开关元件sel2被连接在磁阻效应元件mtj与读取位线rbl之间。开关元件sel1和sel2中的每一个是两端式开关元件。因此,在不使用晶体管等三端式开关元件的情况下,可以形成对其应用使用自旋轨道矩的写入方法的存储单元mc。

161.具体地,在平面图中,布线sotl具有在y方向上延伸的矩形形状。开关元件sel1在z

方向上与布线sotl的第二部分重叠。磁阻效应元件mtj和开关元件sel1按该顺序堆叠,以便在z方向上与布线sotl的第三部分重叠。因此,与存储单元包括三端式开关元件的情况相比,可以减小存储单元的大小。

162.开关元件sel1具有带有折回的电流电压特性。因此,与具有无折回的电流电压特性的开关元件被用于开关元件sel1的情况相比,在写操作期间,容易允许更大的写入电流在处于选择状态的存储单元mc中流动。因此,可以减少写操作的负载。

163.开关元件sel2具有无折回的电流电压特性。因此,与具有带有折回的电流电压特性的开关元件被用于开关元件sel2的情况相比,可以防止在读操作期间无意将高电压施加到磁阻效应元件mtj。因此,可以防止磁阻效应元件mtj的耐久性的劣化。

164.用作布线sotl的导体层24包括铁磁层24b和非磁性层24c。非磁性层24c被提供在铁磁层24b与用作存储层sl的铁磁层27a之间。非磁性层24c包含选自铂(pt)、钯(pd)、金(au)和银(ag)中的至少一种元素。因此,非磁性层24c可以对铁磁层24b和27a执行层间交换耦合。因此,沿着写入电流方向的偏置磁场可以被施加到铁磁层27a。另外,通过允许写入电流流到非磁性层24c,非磁性层24c可以将自旋轨道矩注入铁磁性层27a。因此,即使当磁阻效应元件mtj的磁化方向与膜表面垂直时,在不施加外部磁场并且不允许写入电流流到磁阻效应元件mtj的情况下,也可以反转铁磁层27a的磁化方向。

165.1.4修改例

166.第一实施例不限于上文所描述的示例,并且可以应用各种修改。

167.1.4.1第一修改例

168.在上文所描述的第一实施例中,描述了在不允许写入电流流入磁阻效应元件mtj的情况下反转存储层sl的磁化方向的情况,但该实施例不限于此。例如,磁存储设备可以被操作以通过允许写入电流流到磁阻效应元件mtj来辅助存储层sl的磁化方向的反转。在以下描述中,主要描述与第一实施例不同的配置和操作。可以省略与第一实施例相同的配置和操作的描述。

169.1.4.1.1磁阻效应元件和外围布线

170.图13是示出根据第一实施例的第一修改例的磁阻效应元件和外围布线的剖面结构的示例的剖视图。图13对应于第一实施例中的图5。在第一实施例的第一修改例中,导体层24包括非磁性层24c',代替反铁磁层24a、铁磁层24b和非磁性层24c。

171.非磁性层24c'是非磁性重金属导电膜。非磁性层24c'通过流经非磁性层24c'的电流产生自旋轨道矩。自旋轨道矩被注入铁磁层27a。非磁性层24c'包含例如选自铂(pt)、钯(pd)、金(au)、银(ag)、铪(hf)、钽(ta)和钨(w)中的至少一种元素。非磁性层24c'可以是包括选自铂(pt)、钯(pd)、金(au)、银(ag)、铪(hf)、钽(ta)和钨(w)中的至少一种元素的合金。非磁性层24c'可进一步包含硼(b)、碳(c)、砷(as)、锑(sb)和铋(bi)。

172.元件层27被提供在非磁性层24c'的上表面上。元件层27的配置与第一实施例中的元件层27的配置相同。

173.1.4.1.2写操作

174.图14是示出根据第一实施例的第一修改例的磁存储设备中的写操作的示例的电路图。图14对应于根据第一实施例的图8。

175.当数据被写入存储单元mc《m,n》时,电压vdd或vss被施加到字线wl《m》和写入位线

wbl《n》中的每一个。电压vdd/2 α或vdd/2-α被施加到读取位线rbl《n》。当电压vdd被施加到字线wl《m》时,电压vss和vdd/2 α被分别施加到写入位线wbl《n》和读取位线rbl《n》。当电压vss被施加到字线wl《m》时,电压vdd和vdd/2-α被分别施加到写入位线wbl《n》和读取位线rbl《n》。电压vdd/2被施加到除了字线wl《m》之外的所有字线wl、除了写入位线wbl《n》之外的所有写入位线wbl以及除了读取位线rbl《n》的所有读取位线rbl。

176.电位差vdd/2 α是使开关元件sel1和sel2进入开启状态的电压。电位差vdd/2-α是使开关元件sel1和sel2进入关闭状态的电压。电位差α是使开关元件sel1和sel2进入关闭状态的电压。

177.在字线wl《m》与写入位线wbl《n》之间出现电位差vdd。在字线wl《m》与读取位线rbl《n》之间出现电位差vdd/2-α。在字线wl《m》与除了写入位线wbl《n》之外的写入位线wbl之间出现电位差vdd/2。在字线wl《m》与除了读取位线rbl《n》之外的读取位线rbl之间出现电位差vdd/2。

178.在除了字线wl《m》之外的字线wl与写入位线wbl《n》之间出现电位差vdd/2。在除了字线wl《m》之外的字线wl与读取位线rbl《n》之间出现电位差α。

179.在写入位线wbl《n》与读取位线rbl《n》之间出现电位差vdd/2 α。

180.因此,开关元件sel1《m,n》和sel2《m,n》进入开启状态。除了开关元件sel1《m,n》之外的所有开关元件sel1进入关闭状态。所有开关元件sel2《m,n》进入关闭状态。

181.因此,可以允许电流流到布线sotl《m,n》和磁阻效应元件mtj《m,n》,而不允许电流流经除了布线sotl《m,n》之外的任何布线sotl或者除了磁阻效应元件mtj《m,n》之外的任何磁阻效应元件mtj。

182.图15和图16是示出根据第一实施例的第一修改例的磁存储设备中的写操作的示例的剖视图。图15和图16分别对应于根据第一实施例的图9和图10。

183.首先,参考图15描述数据“1”的写操作。在图15的示例中,示出了写入电流ic1从字线wl(在右侧)流向写入位线wbl(在左侧)并且电流iw1从磁阻效应元件mtj流向写入位线wbl的情况。

184.如上文所描述的,使开关元件sel1进入开启状态的电位差vdd在导体层24的两端出现。通过控制电位差vdd,写入电流ic1流入导体层24。由于写入电流ic1流入导体层24中的非磁性层24c',因此,产生使得铁磁层27a的磁化方向与铁磁层27c的磁化方向反平行的自旋轨道矩。自旋轨道矩被注入靠近非磁性层24c'的铁磁层27a。

185.另外,使开关元件sel2进入开启状态的电位差vdd/2 α在元件层27的上端和导体层24的左端出现。通过控制电位差vdd/2 α,电流iw1从元件层27的上端流向导体层24的左端。由于电流iw1流入元件层27,因此,产生使得铁磁层27a的磁化方向与铁磁层27c的磁化方向反平行的自旋转移矩。

186.因此,通过自旋轨道矩以及自旋转移矩的辅助,铁磁层27a的磁化方向被反转到与铁磁层27c的磁化方向反平行的方向。

187.电流iw1被控制为小于写入电流ic1且大于读取电流ir的值(ir《iw1《ic1)。因此,防止非磁性层27b的介电击穿,并且可以有效地反转铁磁层27a的磁化方向。

188.参考图16描述数据“0”的写操作。在图16的示例中,示出了写入电流ic0从写入位线wbl(在左侧)流向字线wl(在右侧)并且小于电流iw1的电流iw0从写入位线wbl流向磁阻

效应元件mtj的情况。

189.如上文所描述的,使开关元件sel1进入开启状态的电位差vdd在导体层24的两端出现。通过控制电位差vdd,写入电流ic0流入导体层24。由于写入电流ic0流入导体层24中的非磁性层24c',因此,产生使得铁磁层27a的磁化方向与铁磁层27c的磁化方向平行的自旋轨道矩。自旋轨道矩被注入靠近非磁性层24c'的铁磁层27a。

190.另外,使开关元件sel2进入开启状态的电位差vdd/2 α在元件层27的上端和导体层24的左端出现。通过控制电位差vdd/2 α,电流iw0从导体层24的左端流向元件层27的上端。由于电流iw0流入元件层27,因此,产生使得铁磁层27a的磁化方向与铁磁层27c的磁化方向平行的自旋转移矩。

191.因此,通过自旋轨道矩以及自旋转移矩的辅助,铁磁层27a的磁化方向被反转到与铁磁层27c的磁化方向平行的方向。

192.电流iw0被控制为小于写入电流ic0且大于读取电流ir的值(ir《iw0《ic0)。因此,防止非磁性层27b的介电击穿,并且可以有效地反转铁磁层27a的磁化方向。

193.1.4.1.3根据第一实施例的第一修改例的效果

194.根据第一实施例的第一修改例,非磁性层24c'可以是例如包含选自铂(pt)、钯(pd)、金(au)、银(ag)、铪(hf)、钽(ta)和钨(w)中的至少一种元素的合金,并且可进一步包含例如硼(b)、碳(c)、砷(as)、锑(sb)和铋(bi)。因此,非磁性层24c'可以将更大的自旋轨道矩注入铁磁层27a。

195.在写操作中,磁存储设备1被配置为允许电流iw流到处于选择状态的磁阻效应元件mtj。因此,磁阻效应元件mtj可以产生自旋转移矩。因此,即使当磁阻效应元件mtj的磁化方向与膜表面垂直时,也可以在不施加外部磁场的情况下反转铁磁层27a的磁化方向。

196.1.4.2第二修改例

197.在上文所描述的第一实施例和第一实施例的第一修改例中,描述了分别使用通过层间交换耦合的偏置磁场和自旋转移矩以用于辅助自旋轨道矩的情况,但实施例不限于此。例如,磁存储设备可以使用由电流产生的磁场来辅助自旋轨道矩。在以下的描述中,主要描述了与第一实施例或第一实施例的第一修改例不同的配置和操作。可以适当省略与第一实施例或第一实施例的第一修改例相同的配置和操作的描述。

198.1.4.2.1磁阻效应元件和外围布线

199.图17是示出根据第一实施例的第二修改例的磁阻效应元件和外围布线的剖面结构的示例的剖视图。图17对应于根据第一实施例的第一修改例的图13。在第一实施例的第二修改例中,存储单元阵列10进一步包括导体层30。导体层24和元件层27的配置与根据第一实施例的第一修改例的导体层24和元件层27的配置相同。

200.导体层30被提供在非磁性层24c'的下方。导体层30是用于产生要被施加到磁阻效应元件mtj的磁场的导电膜。导体层30在与导体层24的长边方向正交的方向(x方向)上延伸。导体层30例如与存储单元mc中的所有其他配置(导体层21、23、24、25、26和29以及元件层22、27和28)电绝缘。导体层30被配置为能够允许电流沿着x方向从第一端流向第二端。

201.在图17的示例中,示出了导体层30被提供在非磁性层24c'的下方的情况,但实施例不限于此。例如,导体层30可以被提供在非磁性层24c'的上方(例如,在导体层29的上方)。

202.1.4.2.2写操作

203.在根据第一实施例的第二修改例的磁存储设备中的写操作期间被施加到存储单元mc中的各种布线的电压与根据第一实施例的图8的情况中的电压相同。

204.图18和图19是示出根据第一实施例的第二修改例的磁存储设备中的写操作的示例的剖视图。图18和图19对应于根据第一实施例的图9和图10。

205.首先,参考图18描述数据“1”的写操作。在图18的示例中,示出写入电流ic1从字线wl(在右侧)流向写入位线wbl(在左侧)并且电流ia在导体层30中在 x方向(离开页面方向)上流动的情况。

206.如上文所描述的,使开关元件sel1进入开启状态的电位差vdd在导体层24的两端出现。通过控制电位差vdd,写入电流ic1流入导体层24。由于写入电流ic1流入导体层24中的非磁性层24c',产生使得铁磁层27a的磁化方向与铁磁层27c的磁化方向反平行的自旋轨道矩。自旋轨道矩被注入靠近非磁性层24c'的铁磁层27a。

207.另外,电流ia流入导体层30。由于电流ia是在x方向上流动的线性电流,因此,在yz平面内产生以电流ia为中心的圆形磁场。对应的圆形磁场的方向在与铁磁层27a相交的部分中指向-y方向。

208.因此,通过自旋轨道矩以及由电流ia产生的磁场的辅助,铁磁层27a的磁化方向被反转到与铁磁层27c的磁化方向反平行的方向。

209.参考图19描述数据“0”的写操作。在图19的示例中,示出写入电流ic0从写入位线wbl(在左侧)流向字线wl(在右侧)并且电流ia在导体层30中在-x方向(进入页面)上流动的情况。

210.如上文所描述的,使开关元件sel1进入开启状态的电位差vdd在导体层24的两端出现。通过控制电位差vdd,写入电流ic0流入导体层24。由于写入电流ic0流入导体层24中的非磁性层24c',产生使得铁磁层27a的磁化方向与铁磁层27c的磁化方向平行的自旋轨道矩。自旋轨道矩被注入靠近非磁性层24c'的铁磁层27a。

211.另外,电流ia流入导体层30。由于电流ia是在-x方向上流动的线性电流,因此,在yz平面内产生以电流ia为中心的圆形磁场。对应的圆形磁场的方向在与铁磁层27a相交的部分中指向y方向。

212.因此,通过自旋轨道矩以及由电流ia产生的磁场的辅助,铁磁层27a的磁化方向被反转到与铁磁层27c的磁化方向平行的方向。

213.1.4.2.3根据第一实施例的第二修改例的效果

214.根据第一实施例的第二修改例,导体层30在与布线sotl正交的方向上延伸。磁存储设备1被配置为在写操作期间允许电流ia流到导体层30。因此,导体层30可以将与写入电流平行的磁场施加到铁磁层27a。因此,即使当磁阻效应元件mtj的磁化方向与膜表面垂直时,也可以在不施加外部磁场或者不允许写入电流流到磁阻效应元件mtj的情况下反转铁磁层27a的磁化方向。

215.在第一实施例的第二修改例中,描述了磁阻效应元件mtj的磁化方向与膜表面垂直的情况,但实施例不限于此。例如,磁阻效应元件mtj的磁化方向可以与膜表面平行。具体地,当磁阻效应元件mtj的磁化方向指向x方向时,需要与z方向上的外部磁场对应的辅助以用于反转铁磁层27a的磁化方向,而不允许写入电流流到磁阻效应元件mtj。在这种情况下,

提供导体层30以便例如在y方向上与磁阻效应元件mtj对齐。因此,可以使得由电流ia产生的磁场的方向在与铁磁层27a相交的部分中指向z方向。因此,即使当磁阻效应元件mtj的磁化方向与膜表面平行时,也可以在不施加外部磁场或者不允许写入电流流到磁阻效应元件mtj的情况下反转铁磁层27a的磁化方向。

216.1.4.3第一实施例的第三修改例

217.在上文所描述的第一实施例以及第一实施例的第一修改例和第二修改例中,描述了磁阻效应元件mtj具有与膜表面垂直的磁化方向的情况,但实施例不限于此。例如,磁阻效应元件可以具有与膜表面平行的磁化方向。在以下的描述中,主要描述了与第一实施例以及第一实施例的第一修改例和第二修改例不同的配置和操作。可以适当省略与第一实施例以及第一实施例的第一修改例和第二修改例相同的配置和操作的描述。

218.1.4.3.1存储单元阵列的平面布局

219.图20是示出根据第一实施例的第三修改例的存储单元阵列的平面布局的示例的平面图。图20对应于第一实施例中的图3。

220.存储单元阵列10包括多个垂直结构v2',代替多个垂直结构v2。每一个垂直结构v2'包括磁阻效应元件mtj和开关元件sel2。

221.垂直结构v2'在z方向上延伸。在平面图中,垂直结构v2'每一个具有椭圆形状。垂直结构v2'被设置为使得椭圆形状的长轴方向与布线sotl的短边方向(即,x方向)平行。每一个垂直结构v2'被连接在一个对应的读取位线rbl与一个对应的布线sotl之间。

222.1.4.3.2磁阻效应元件和外围布线

223.图21是示出根据第一实施例的第三修改例的磁阻效应元件和外围布线的剖面结构的示例的剖视图。图21对应于根据第一实施例的第一修改例的图13。根据第一实施例的第三修改例的导体层24的配置与根据第一实施例的第一修改例的包括非磁性层24c'的导体层24的配置相同。元件层27包括铁磁层27a'、非磁性层27b、铁磁层27c'、非磁性层27d和铁磁层27e'。

224.铁磁层27a'被提供在非磁性层24c'的上表面上。非磁性层27b被提供在铁磁层27a'的上表面上。铁磁层27c'被提供在非磁性层27b的上表面上。非磁性层27d被提供在铁磁层27c'的上表面上。铁磁层27e'被提供在非磁性层27d的上表面上。

225.除了铁磁层27a'、27c'和27e'在平面图中的垂直结构v2'的椭圆形状的长轴方向(x方向)上具有易磁化轴向之外,铁磁层27a'、27c'和27e'分别与根据第一实施例的铁磁层27a、27c和27e相同。在图21的示例中,铁磁层27a'具有在 x方向(离开页面)或-x方向(进入页面)上的磁化方向。铁磁层27c'具有在 x方向上的磁化方向。铁磁层27e'具有在-x方向上的磁化方向。也就是说,元件层27用作面内磁化型磁阻效应元件mtj。

226.1.4.3.3写操作

227.在根据第一实施例的第三修改例的磁存储设备中的写操作期间被施加到存储单元mc中的各种布线的电压与根据第一实施例的图8的情况中的电压相同。

228.图22和图23是示出根据第一实施例的第三修改例的磁存储设备中的写操作的示例的剖视图。图22和图23分别对应于根据第一实施例的图9和图10。

229.首先,参考图22描述数据“1”的写操作。在图22的示例中,示出写入电流ic1从字线wl(在右侧)流向写入位线wbl(在左侧)的情况。

230.如上文所描述的,使开关元件sel1进入开启状态的电位差vdd在导体层24的两端出现。通过控制电位差vdd,写入电流ic1流入导体层24。由于写入电流ic1流入导体层24中的非磁性层24c',产生使得铁磁层27a的磁化方向与铁磁层27c的磁化方向反平行的自旋轨道矩。自旋轨道矩被注入靠近非磁性层24c'的铁磁层27a。

231.因此,通过自旋轨道矩,铁磁层27a的磁化方向被反转到与铁磁层27c的磁化方向反平行的方向。

232.参考图23描述数据“0”的写操作。在图23的示例中,示出写入电流ic0从写入位线wbl(在左侧)流向字线wl(在右侧)的情况。

233.如上文所描述的,使开关元件sel1进入开启状态的电位差vdd在导体层24的两端出现。通过控制电位差vdd,写入电流ic0流入导体层24。由于写入电流ic0流入导体层24中的非磁性层24c',产生使得铁磁层27a的磁化方向与铁磁层27c的磁化方向平行的自旋轨道矩。自旋轨道矩被注入靠近非磁性层24c'的铁磁层27a。

234.因此,通过自旋轨道矩,铁磁层27a的磁化方向被反转到与铁磁层27c的磁化方向平行的方向。

235.1.4.3.4根据第一实施例的第三修改例的效果

236.根据第一实施例的第三修改例,包括元件层27的垂直结构v2'在平面图中具有椭圆形状。椭圆形状的长轴方向与布线sotl的短边方向(x方向)平行。因此,磁阻效应元件mtj被配置为在x方向上具有易磁化轴向。因此,磁阻效应元件mtj可以仅通过自旋轨道矩来反转铁磁层27a'的磁化方向,而无需施加外部磁场,也无需应用替代外部磁场的方法。

237.2.第二实施例

238.根据第二实施例,形成开关元件sel2的位置与第一实施例不同。在以下的描述中,主要描述了与第一实施例不同的配置和操作。可以省略与第一实施例相同的配置和操作的描述。

239.2.1存储单元阵列的电路配置

240.图24是示出根据第二实施例的存储单元阵列的电路配置的示例的电路图。图24对应于根据第一实施例的图2。

241.开关元件sel2《i,j》被连接在布线sotl《i,j》的第一部分与字线wl《i》之间。开关元件sel1《i,j》被连接在布线sotl《i,j》的第二部分与写入位线wbl《j》之间。磁阻效应元件mtj《i,j》被连接在布线sotl《i,j》的第三部分与读取位线rbl《j》之间。

242.2.2存储单元阵列的平面布局

243.图25是示出根据第二实施例的存储单元阵列的平面布局的示例的平面图。图25对应于根据第一实施例的图3。

244.在存储单元阵列10中,每一个垂直结构v1包括开关元件sel1。每一个垂直结构v2包括磁阻效应元件mtj。每一个垂直结构v3包括开关元件sel2。

245.在如上的配置中,包括一个布线sotl以及连接到一个对应的布线sotl的一个垂直结构v1、一个垂直结构v2和一个垂直结构v3的组用作一个存储单元mc。

246.2.3存储单元阵列的剖面结构

247.图26是示出根据第二实施例的存储单元阵列的剖面结构的示例的剖视图,其沿着图25的线xxvi-xxvi取得。图26对应于根据第一实施例的图4。层级结构l1包括导体层31_1、

32_1、34_1、36_1和38_1以及元件层33_1、35_1和37_1。层级结构l2包括导体层31_2、32_2、34_2、36_2和38_2以及元件层33_2、35_2和37_2。

248.首先,描述层级结构l1。

249.导体层31_1被提供在半导体衬底20的上方。导体层31_1用作写入位线wbl。导体层31_1在y方向上延伸。

250.导体层32_1被提供在导体层31_1的上表面上。导体层32_1用作接触。

251.元件层33_1提被供在导体层32_1的上表面上。元件层33_1用作开关元件sel1。导体层32_1和元件层33_1配置垂直结构v1。

252.导体层34_1被提供在元件层33_1的上表面上。导体层34_1用作布线sotl。导体层34_1在y方向上延伸。

253.元件层35_1被提供在导体层34_1的下表面的与提供元件层33_1的部分不同的部分中。元件层35_1用作开关元件sel2。元件层35_1配置垂直结构v3。

254.元件层33_1和35_1由相同的工艺形成。在这种情况下,元件层33_1和35_1被提供在相同的高度处。也就是说,元件层33_1的下表面位于与元件层35_1的下表面相同的xy平面上。而且,元件层33_1和35_1被形成为具有相同的电流电压特性。例如,所有元件层33_1和35_1具有带有折回的电流电压特性。

255.导体层36_1被提供在元件层35_1的下表面上。导体层36_1用作字线wl。导体层36_1在x方向上延伸。

256.元件层37_1被提供在导体层34_1的上表面的提供元件层33_1的部分与提供元件层35_1的部分之间的部分中。元件层37_1用作磁阻效应元件mtj。

257.导体层38_1被提供在元件层37_1的上表面上。导体层38_1用作读取位线rbl。导体层38_1在y方向上延伸。

258.在如上的配置中,层级结构l1中的包括导体层34_1和垂直结构v1、v2和v3的一个组用作具有分别连接到导体层31_1、36_1和38_1的三个端子的一个存储单元mc。

259.层级结构l2具有与层级结构l1相同的配置。也就是说,导体层31_2、32_2、34_2、36_2和38_2以及元件层33_2、35_2和37_2分别具有与导体层31_1、32_1、34_1、36_1和38_1以及元件层33_1、35_1和37_1相同的结构和相同的功能。因此,层级结构l2中的包括导体层34_2和垂直结构v1、v2和v3的一个组用作具有分别连接到导体层31_2、36_2和38_2的三个端子的一个存储单元mc。

260.2.4第二实施例的效果

261.根据第二实施例,开关元件sel2被连接在布线sotl与字线wl之间。用作开关元件sel1的元件层33和用作开关元件sel2的元件层35被提供在相同的高度处。因此,可以在相同的工艺中形成元件层33和35。因此,可以减少存储单元阵列10的制造负载。当在相同的工艺中形成元件层33和35时,元件层35以与元件层33相同的方式被形成为具有带有折回的电流电压特性。因此,可以维持在写操作期间容易在处于选择状态的存储单元mc中流动更大的写入电流的效果。

262.在根据第二实施例的磁存储设备中,可以应用根据第一实施例的第一修改例、第一实施例的第二修改例和第一实施例的第三修改例的配置和操作。在这种情况下,根据第二实施例的磁存储器设备可以展现出与第一实施例的第一修改例、第一实施例的第二修改

例和第一实施例的第三修改例相同的效果。

263.3.第三实施例

264.描述了根据第三实施例的磁存储设备。第三实施例与第一实施例和第二实施例的不同之处在于,字线wl由多个存储单元mc共享。在以下的描述中,主要描述与第一实施例不同的配置和操作。可以省略与第一实施例相同的配置和操作的描述。

265.3.1存储单元阵列的电路配置

266.图27是示出根据第三实施例的存储单元阵列的电路配置的示例的电路图。

267.存储单元阵列10包括多个存储单元mc、多个字线wla和wlb、多个读取位线rbl和多个写入位线wbl。在图27的示例中,在多个存储单元mc中,示出了八个存储单元mc《m,n-1》、mc《m,n》、mc《m,n 1》、mc《m,n 2》、mc《m 1,n-2》、mc《m 1,n-1》、mc《m 1,n》和mc《m 1,n 1》。在多个字线wla和wlb中,示出了两个字线wla《m》和wla《m 1》以及两个字线wlb《m》和wlb《m 1》。在多个读取位线rbl中,示出了五个读取位线rbl《n-2》、rbl《n-1》、rbl《n》、rbl《n 1》和rbl《n 2》。在多个写入位线wbl中,示出了六个写入位线wbl《n-2》、wbl《n-1》、wbl《n》、wbl《n 1》、wbl《n 2》和wbl《n 3》。

268.存储单元mc《m,n-1》包括被连接到字线wla《m》的第一端、被连接到写入位线wbl《n-1》的第二端和被连接到读取位线rbl《n-1》的第三端。存储单元mc《m,n》包括被连接到字线wla《m》的第一端、被连接到写入位线wbl《n 1》的第二端和被连接到读取位线rbl《n》的第三端。存储单元mc《m,n-1》的第一端和存储单元mc《m,n》的第一端由彼此共享。

269.存储单元mc《m,n 1》包括被连接到字线wlb《m》的第一端、被连接到写入位线wbl《n 1》的第二端和被连接到读取位线rbl《n 1》的第三端。存储单元mc《m,n 2》包括被连接到字线wlb《m》的第一端、被连接到写入位线wbl《n 3》的第二端和被连接到读取位线rbl《n 2》的第三端。存储单元mc《m,n 1》的第一端和存储单元mc《m,n 2》的第一端由彼此共享。

270.存储单元mc《m 1,n-2》包括被连接到字线wla《m 1》的第一端、被连接到写入位线wbl《n-2》的第二端和被连接到读取位线rbl《n-2》的第三端。存储单元mc《m 1,n-1》包括被连接到字线wla《m 1》的第一端、被连接到写入位线wbl《n》的第二端和被连接到读取位线rbl《n-1》的第三端。存储单元mc《m 1,n-2》的第一端和存储单元mc《m 1,n-1》的第一端由彼此共享。

271.存储单元mc《m 1,n》包括被连接到字线wlb《m 1》的第一端、被连接到写入位线wbl《n》的第二端和被连接到读取位线rbl《n》的第三端。存储单元mc《m 1,n 1》包括被连接到字线wlb《m 1》的第一端、被连接到写入位线wbl《n 2》的第二端和被连接到读取位线rbl《n 1》的第三端。存储单元mc《m 1,n》的第一端和存储单元mc《m 1,n 1》的第一端由彼此共享。

272.包括八个存储单元mc《m,n-1》、mc《m,n》、mc《m,n 1》、mc《m,n 2》、mc《m 1,n-2》、mc《m 1,n-1》、mc《m 1,n》和mc《m 1,n 1》的该组在行方向和列方向上重复以形成存储单元阵列10。也就是说,在同一行中(例如,第m行),连接到字线wla并且在列方向上彼此相邻的两个存储单元mc(例如,mc《m,n-1》和mc《m,n》)和连接到字线wlb《m》并且在列方向上彼此相邻的两个存储单元mc(例如,mc《m,n 1》和mc《m,n 2》)在列方向上被交替地布置。

273.在如上文所描述的存储单元阵列10中的多个存储单元mc中,描述连接到相同字线wla并且在列方向上彼此相邻的两个存储单元mc《m,n-1》和mc《m,n》的配置。存储单元mc《m,n-1》包括开关元件sel1《m,n-1》和sel2《m,n-1》以及磁阻效应元件mtj《m,n-1》。存储单元mc

《m,n》包括开关元件sel1《m,n》和sel2《m,n》以及磁阻效应元件mtj《m,n》。存储单元mc《m,n-1》和mc《m,n》共享布线sotl《m,n-1^n》。在该上下文中的符号“n-1^n”指示在列(n-1)与列(n)之间的该布线sotl桥接/跨接/交叉。

274.布线sotl《m,n-1^n》的第一部分被连接到字线wla《m》。布线sotl《m,n-1^n》的第二部分被连接到写入位线wbl《n-1》。布线sotl《m,n-1^n》的第三部分被连接到读取位线rbl《n-1》。布线sotl《m,n-1^n》的第四部分被连接到写入位线wbl《n 1》。布线sotl《m,n-1^n》的第五部分被连接到读取位线rbl《n》。

275.开关元件sel1《m,n-1》被连接在布线sotl《m,n-1^n》的第二部分与写入位线wbl《n-1》之间。磁阻效应元件mtj《m,n-1》被连接在布线sotl《m,n-1^n》的第三部分与读取位线rbl《n-1》之间。开关元件sel2《m,n-1》被连接在磁阻效应元件mtj《m,n-1》与读取位线rbl《n-1》之间。

276.开关元件sel1《m,n》被连接在布线sotl《m,n-1^n》的第四部分与写入位线wbl《n 1》之间。磁阻效应元件mtj《m,n》被连接在布线sotl《m,n-1^n》的第五部分与读取位线rbl《n》之间。开关元件sel2《m,n》被连接在磁阻效应元件mtj《m,n》与读取位线rbl《n》之间。

277.3.2存储单元阵列的平面布局

278.图28是示出根据第三实施例的存储单元阵列的平面布局的示例的平面图。

279.存储单元阵列10包括垂直结构v1、垂直结构v2、多个垂直结构v3a和多个垂直结构v3b。每一个垂直结构v1包括开关元件sel1。每一个垂直结构v2包括磁阻效应元件mtj和开关元件sel2。

280.多个写入位线wbl被布置在x方向上。每一个写入位线wbl在y方向上延伸。

281.多个字线wlb被提供在多个写入位线wbl的上方。多个字线wlb被布置在y方向上。每一个字线wlb在x方向上延伸。

282.多个布线sotl被提供在多个字线wlb的上方。在平面图中,每一个布线sotl具有矩形形状。布线sotl的长边方向和短边方向分别与xy平面中的x方向和y方向相交。在以下的描述中,布线sotl的长边方向和短边方向分别被称为p方向和q方向。由y方向和p方向形成的角度θ是例如(90-atan(1/3))度。在平面图中,每一个布线sotl被提供在与一个字线wlb(或wla)和三个相邻的写入位线wbl重叠的位置处。

283.多个读取位线rbl被提供在多个布线sotl的上方。多个读取位线rbl被布置在x方向上。每一个读取位线rbl在y方向上延伸。在平面图中,每一个读取位线rbl被提供在相邻的两个写入位线wbl之间。

284.多个字线wla被提供在多个读取位线rbl的上方。多个字线wla被布置在y方向上。每一个字线wla在x方向上延伸。在平面图中,在重叠位置处提供彼此对应的一个字线wla和一个字线wlb。

285.垂直结构v1在z方向上延伸。在平面图中,垂直结构v1每一个具有圆形形状。每一个垂直结构v1被连接在一个对应的写入位线wbl与一个对应的布线sotl之间。

286.垂直结构v2在z方向上延伸。在平面图中,垂直结构v2每一个具有圆形形状。每一个垂直结构v2被连接在一个对应的读取位线rbl与一个对应的布线sotl之间。

287.垂直结构v3a在z方向上延伸。在平面图中,垂直结构v3a每一个具有圆形形状。每一个垂直结构v3a被连接在一个对应的字线wla与一个对应的布线sotl之间。

288.垂直结构v3b在z方向上延伸。在平面图中,垂直结构v3b每一个具有圆形形状。每一个垂直结构v3b被连接在一个对应的字线wlb与一个对应的布线sotl之间。

289.在如上的配置中,包括一个布线sotl以及连接到一个对应的布线sotl的一个垂直结构v1、一个垂直结构v2和一个垂直结构v3a或v3b的组用作一个存储单元mc。而且,布线sotl和垂直结构v3a由两个存储单元mc共享。布线sotl和垂直结构v3b由两个存储单元mc共享。

290.分别为共享相同布线sotl的两个存储单元mc提供的两个垂直结构v2被布置在p方向上。而且,在平面图中,每个垂直结构v2的中心位于布线sotl的沿着p方向的对称轴上。也就是说,分别为共享对应布线sotl的两个存储单元mc提供的布线sotl和两个垂直结构v2沿着p方向被提供在相同的轴上。两个垂直结构v2可以说是彼此“同轴”。在该上下文中,“相同”包括基本上相同,诸如在正常制造公差等内的图案/位置对齐。

291.3.3存储单元阵列的剖面结构

292.图29是示出根据第三实施例的存储单元阵列的剖面结构的示例的剖视图,其沿着图28的线xxix-xxix取得。在图29中,示出被连接到字线wla的配置。

293.层级结构l1包括导体层41_1、42_1、43_1、46_1、47_1、48_1、49_1、54_1、55_1和56_1以及元件层44_1、45_1、50_1、51_1、52_1和53_1。层级结构l2包括导体层41_2、42_2、43_2、46_2、47_2、48_2、49_2、54_2、55_2和56_2以及元件层44_2、45_2、50_2、51_2、52_2和53_2。

294.首先,描述层级结构l1。

295.导体层41_1、42_1和43_1被提供在半导体衬底20的上方。导体层41_1、42_1和43_1用作彼此相邻的写入位线wbl。每一个导体层41_1、42_1和43_1在y方向上延伸。

296.元件层44_1和45_1分别被提供在导体层41_1和43_1的上表面上。每一个元件层44_1和45_1用作开关元件sel1。

297.导体层46_1和47_1分别被提供在元件层44_1和45_1的上表面上。每一个导体层46_1和47_1用作接触。元件层44_1和导体层46_1配置垂直结构v1。元件层45_1和导体层47_1配置垂直结构v1。

298.垂直结构v1也可以在导体层42_1的上表面上。然而,导体层42_1上的垂直结构v1与导体层41_1上的垂直结构v1或导体层43_1上的垂直结构v1在p方向上未对齐。图29中未示出具体在导体层42_1上的垂直结构v1。

299.在p方向上延伸的导体层48_1与导体层46_1的上表面和导体层47_1的上表面接触。导体层48_1用作布线sotl。在导体层48_1上,与导体层46_1的连接部分和与导体层47_1的连接部分分别对应于布线sotl的第二部分和第四部分。

300.导体层49_1以及元件层50_1和51_1被提供在导体层48_1的上表面上。

301.导体层49_1被提供在导体层42_1的上方。在导体层48_1上,与导体层49_1的连接部分对应于布线sotl的第一部分。导体层49_1用作接触。

302.元件层50_1被提供在与导体层46_1的连接部分和与导体层49_1的连接部分之间。元件层51_1被提供在与导体层47_1的连接部分和与导体层49_1的连接部分之间。在导体层48_1上,与元件层50_1的连接部分和与元件层51_1的连接部分分别对应于布线sotl的第三部分和第五部分。每一个元件层50_1和51_1用作磁阻效应元件mtj。

303.元件层52_1和53_1被分别提供在元件层50_1和51_1的上表面上。

304.每一个元件层52_1和53_1用作开关元件sel2。元件层50_1和元件层52_1配置垂直结构v2。元件层51_1和元件层53_1配置垂直结构v2。

305.导体层54_1和55_1被分别提供在元件层52_1和53_1的上表面上。每一个导体层54_1和55_1用作读取位线rbl。每一个导体层54_1和55_1在y方向上延伸。

306.在导体层54_1和55_1的上方,导体层56_1被提供在导体层49_1的上表面上。导体层56_1用作字线wla。导体层56_1在x方向上延伸。

307.在如上的配置中,层级结构l1中的一个导体层48_1、两个垂直结构v1、两个垂直结构v2和一个垂直结构v3a用作共享导体层49_1和导体层56_1的两个存储单元mc。

308.层级结构l2具有与层级结构l1相同的配置。也就是说,导体层41_2、42_2、43_2、46_2、47_2、48_2、49_2、54_2、55_2和56_2以及元件层44_2、45_2、50_2、51_2、52_2和53_2分别具有与导体层41_1、42_1、43_1、46_1、47_1、48_1、49_1、54_1、55_1和56_1以及元件层44_1、45_1、50_1、51_1、52_1和53_1相同的结构和相同的功能。因此,层级结构l2中的一个导体层48_2、两个垂直结构v1、两个垂直结构v2和一个垂直结构v3a用作共享导体层49_2和导体层56_2的两个存储单元mc。

309.图30是示出根据第三实施例的存储单元阵列的剖面结构的示例的剖视图,其沿着图28的线xxx-xxx取得。在图30中,示出被连接到字线wlb的配置。

310.层级结构l1包括导体层43_1、57_1、58_1、61_1、62_1、63_1、64_1、65_1、70_1和71_1以及元件层59_1、60_1、66_1、67_1、68_1和69_1。层级结构l2包括导体层43_2、57_2、58_2、61_2、62_2、63_2、64_2、65_2、70_2和71_2以及元件层59_2、60_2、66_2、67_2、68_2和69_2。

311.首先,描述层级结构l1。

312.图30中的导体层43_1、57_1、58_1、61_1、62_1、63_1、70_1和71_1以及元件层59_1、60_1、66_1、67_1、68_1和69_1的配置与图29中的导体层41_1、42_1、43_1、46_1、47_1、48_1、54_1和55_1以及元件层44_1、45_1、50_1、51_1、52_1和53_1的配置相同。

313.导体层64_1被提供在导体层63_1的下表面上。

314.导体层64_1被直接提供在导体层57_1的上方。在导体层63_1上,与导体层64_1的连接部分对应于布线sotl的第一部分。导体层64_1用作接触。

315.在导体层57_1的上方,导体层65_1被提供在导体层64_1的下表面上。导体层65_1用作字线wlb。导体层65_1在x方向上延伸。尽管在图30中未具体示出,但是,导体层65_1穿过包括元件层59_1和导体层61_1的垂直结构v1与包括元件层60_1和导体层62_1的垂直结构v1之间。

316.在如上的配置中,层级结构l1中的一个导体层63_1、两个垂直结构v1、两个垂直结构v2和一个垂直结构v3b用作共享导体层64_1和导体层65_1的两个存储单元mc。

317.层级结构l2具有与层级结构l1相同的配置。也就是说,导体层43_2、57_2、58_2、61_2、62_2、63_2、64_2、65_2、70_2和71_2以及元件层59_2、60_2、66_2、67_2、68_2和69_2分别具有与导体层43_1、57_1、58_1、61_1、62_1、63_1、64_1、65_1、70_1和71_1以及元件层59_1、60_1、66_1、67_1、68_1和69_1相同的结构和相同的功能。因此,层级结构l2中的一个导体层63_2、两个垂直结构v1、两个垂直结构v2和一个垂直结构v3b用作共享导体层64_2和导体层65_2的两个存储单元mc。

318.3.4第三实施例的效果

319.根据第三实施例,布线sotl《m,n-1^n》包括第一部分、第二部分、第一部分与第二部分之间的第三部分、相对于第一部分在与第二部分的相对侧提供的第四部分、以及第一部分与第四部分之间的第五部分。布线sotl《m,n-1^n》的第一部分被连接到字线wla《m》。布线sotl《m,n-1^n》的第二部分和第四部分被分别连接到写入位线wbl《n-1》和wbl《n 1》。布线sotl《m,n-1^n》的第三部分和第五部分被分别连接到读取位线rbl《n-1》和rbl《n》。因此,两个存储单元mc《m,n-1》和mc《m,n》可以共享字线wla《m》。

320.布线sotl《m,n 1^n 2》包括第一部分、第二部分、第一部分与第二部分之间的第三部分、相对于第一部分在与第二部分的相对侧提供的第四部分、以及第一部分与第四部分之间的第五部分。布线sotl《m,n 1^n 2》的第一部分被连接到字线wlb《m》。布线sotl《m,n 1^n 2》的第二部分和第四部分被分别连接到写入位线wbl《n 1》和wbl《n 3》。布线sotl《m,n 1^n 2》的第三部分和第五部分被分别连接到读取位线rbl《n 1》和rbl《n 2》。因此,两个存储单元mc《m,n 1》和mc《m,n 2》可以共享字线wlb《m》。

321.存储单元阵列10包括字线wla《m》和wlb《m》。字线wla《m》和wlb《m》在平面图中被设置在重叠位置处。字线wla《m》被提供在布线sotl《m,n-1^n》的上方。字线wlb《m》被提供在布线sotl《m,n 1^n 2》的下方。因此,可以独立地选择被连接到相同的写入位线wbl《n 1》的两个存储单元mc《m,n》和mc《m,n 1》。

322.布线sotl具有矩形形状,其长边在与写入位线wbl和读取位线以角度θ(=90-atan(1/3)度)相交的方向上延伸。因此,当字线wla和wlb由两个存储单元共享时,磁阻效应元件mtj可以被设置在最紧密的封装中。

323.在平面图中,共享布线sotl的两个垂直结构v2被提供在与对应的布线sotl相同的轴上。因此,与垂直结构v2未被提供在与布线sotl相同的轴上的情况相比,可以增加与磁阻效应元件mtj和布线sotl的接触面积。因此,在写操作期间,布线sotl可以将更大的自旋轨道矩注入磁阻效应元件mtj。

324.根据第一实施例的第一修改例、第一实施例的第二修改例和第一实施例的第三修改例的配置和操作可以应用于根据第三实施例的磁存储设备。在这种情况下,根据第三实施例的磁存储设备可以展现与第一实施例的第一修改例、第一实施例的第二修改例和第一实施例的第三修改例相同的效果。

325.4.第四实施例

326.描述根据第四实施例的磁存储设备。第四实施例与第三实施例的不同之处在于,共享布线sotl的两个垂直结构v2未被提供在与对应的布线sotl相同的轴上。在以下的描述中,主要描述与第三实施例不同的配置和操作。可以省略与第三实施例相同的配置和操作的描述。

327.4.1存储单元阵列的平面布局

328.图31是示出根据第四实施例的存储单元阵列的平面布局的示例的平面图。图31对应于根据第三实施例的图28。

329.在平面图中,多个垂直结构v2被布置为正方形网格图案形状。因此,在共享布线sotl的两个存储单元mc中分别提供的两个垂直结构v2被布置在x方向上。然而,布线sotl的长边方向是p方向。因此,在平面图中,垂直结构v2的中心从布线sotl的沿着p方向的对称轴偏离到q方向。

330.4.2根据第四实施例的效果

331.根据第四实施例,垂直结构v2可以在x方向和y方向上以相等的间隔布置。因此,可以减少磁阻效应元件mtj和开关元件sel2的处理负载。

332.根据第一实施例的第一修改例、第一实施例的第二修改例和第一实施例的第三修改例的配置和操作可以应用于根据第四实施例的磁存储设备。在这种情况下,根据第四实施例的磁存储设备可以展现与第一实施例的第一修改例、第一实施例的第二修改例和第一实施例的第三修改例相同的效果。

333.5.第五实施例

334.描述根据第五实施例的磁存储设备。第五实施例与第三和第四实施例的不同之处在于,所有字线被提供在布线sotl的上方。在以下的描述中,主要描述与第三实施例不同的配置和操作。可以省略与第三实施例相同的配置和操作的描述。

335.5.1存储单元阵列的平面布局

336.图32是示出根据第五实施例的存储单元阵列的平面布局的示例的平面图。图32对应于根据第三实施例的图28。

337.存储单元阵列10包括多个字线wla'和wlb',以代替多个字线wla和wlb。存储单元阵列10还包括垂直结构v3a'和v3b',以代替垂直结构v3a和v3b。

338.多个字线wla'和wlb'被提供在多个读取位线rbl的上方。多个字线wla'和wlb'在y方向上被交替布置。每一个字线wla'和wlb'在x方向上延伸。字线wla'之间和wlb'之间在y方向上的间隔(间距)是根据第三实施例的字线wla在y方向上的间隔的一半和字线wlb在y方向上的间隔的一半。

339.垂直结构v3a'在z方向上延伸。在平面图中,垂直结构v3a'每一个具有圆形形状。每一个垂直结构v3a'被连接在一个对应的字线wla'与一个对应的布线sotl之间。

340.垂直结构v3b'在z方向上延伸。在平面图中,垂直结构v3b'每一个具有圆形形状。每一个垂直结构v3b'被连接在一个对应的字线wlb'与一个对应的布线sotl之间。

341.5.2第五实施例的效果

342.根据第五实施例,多个字线wla'和wlb'可以被设置在相同的高度(水平)处。因此,可以在相同的工艺中形成多个字线wla'和wlb'。因此,可以减少存储单元阵列10的制造负载。

343.根据第一实施例的第一修改例、第一实施例的第二修改例和第一实施例的第三修改例的配置和操作可以应用于根据第五实施例的磁存储设备。在这种情况下,根据第五实施例的磁存储设备可以展现与第一实施例的第一修改例、第一实施例的第二修改例和第一实施例的第三修改例相同的效果。

344.第四实施例的配置可以应用于根据第五实施例的磁存储设备。在这种情况下,根据第五实施例的磁存储设备可以展现与第四实施例相同的效果。

345.6.第六实施例

346.描述根据第六实施例的磁存储设备。第六实施例与第三实施例的不同之处在于,布线sotl被布置成与字线wl平行。在以下的描述中,主要描述与第三实施例不同的配置和操作。可以省略与第三实施例相同的配置和操作的描述。

347.6.1存储单元阵列的电路配置

348.图33是示出根据第六实施例的存储单元阵列的电路配置的示例的电路图。图33对应于根据第三实施例的图27。

349.该实施例的存储单元阵列10包括多个存储单元mc、多个字线wl、多个读取位线rbl和多个写入位线wbl。在图33中,在多个存储单元mc中,示出了八个存储单元mc《m,n-1》、mc《m,n》、mc《m,n 1》、mc《m,n 2》、mc《m 1,n-1》、mc《m 1,n》、mc《m 1,n 1》和mc《m 1,n 2》。在多个字线wl中,示出了两个字线wl《m》和wl《m 1》。在多个读取位线rbl中,示出了四个读取位线rbl《n-1》、rbl《n》、rbl《n 1》和rbl《n 2》。在多个写入位线wbl中,示出了四个写入位线wbl《n-1》、wbl《n》、wbl《n 1》和wbl《n 2》。

350.存储单元mc《m,n-1》包括被连接到字线wl《m》的第一端、被连接到写入位线wbl《n-1》的第二端和被连接到读取位线rbl《n-1》的第三端。存储单元mc《m,n》包括被连接到字线wl《m》的第一端、被连接到写入位线wbl《n》的第二端和被连接到读取位线rbl《n》的第三端。存储单元mc《m,n-1》的第一端和存储单元mc《m,n》的第一端由彼此共享。

351.存储单元mc《m,n 1》包括被连接到字线wl《m》的第一端、连接到写入位线wbl《n 1》的第二端和被连接到读取位线rbl《n 1》的第三端。存储单元mc《m,n 2》包括被连接到字线wl《m》的第一端、被连接到写入位线wbl《n 2》的第二端和被连接到读取位线rbl《n 2》的第三端。存储单元mc《m,n 1》的第一端和存储单元mc《m,n 2》的第一端由彼此共享。

352.存储单元mc《m 1,n-1》包括被连接到字线wl《m 1》的第一端、被连接到写入位线wbl《n-1》的第二端和被连接到读取位线rbl《n-1》的第三端。存储单元mc《m 1,n》包括被连接到字线wl《m 1》的第一端、被连接到写入位线wbl《n》的第二端和被连接到读取位线rbl《n》的第三端。存储单元mc《m 1,n-1》的第一端和存储单元mc《m 1,n》的第一端由彼此共享。

353.存储单元mc《m 1,n 1》包括被连接到字线wl《m 1》的第一端、被连接到写入位线wbl《n 1》的第二端和被连接到读取位线rbl《n 1》的第三端。存储单元mc《m 1,n 2》包括被连接到字线wl《m 1》的第一端、被连接到写入位线wbl《n 2》的第二端和被连接到读取位线rbl《n 2》的第三端。存储单元mc《m 1,n 1》的第一端和存储单元mc《m 1,n 2》的第一端由彼此共享。

354.包括八个存储单元mc《m,n-1》、mc《m,n》、mc《m,n 1》、mc《m,n 2》、mc《m 1,n-1》、mc《m 1,n》、mc《m 1,n 1》和mc《m 1,n 2》的该组在行方向和列方向上重复以形成存储单元阵列10。

355.在上文所描述的存储单元阵列10中的多个存储单元mc中,描述被连接到相同字线wl并且在列方向上彼此相邻的两个存储单元mc《m,n-1》和mc《m,n》的配置。存储单元mc《m,n-1》包括开关元件sel1《m,n-1》和sel2《m,n-1》以及磁阻效应元件mtj《m,n-1》。存储单元mc《m,n》包括开关元件sel1《m,n》和sel2《m,n》以及磁阻效应元件mtj《m,n》。存储单元mc《m,n-1》和mc《m,n》共享布线sotl《m,n-1^n》。

356.布线sotl《m,n-1^n》包括第一部分、第二部分、第三部分、第四部分和第五部分。布线sotl《m,n-1^n》的第三部分被提供在布线sotl《m,n-1^n》的第一部分与布线sotl《m,n-1^n》的第二部分之间。布线sotl《m,n-1^n》的第四部分相对于布线sotl《m,n-1^n》的第一部分被提供在与布线sotl《m,n-1^n》的第二部分的相对侧。布线sotl《m,n-1^n》的第五部分被提供在布线sotl《m,n-1^n》的第一部分与布线sotl《m,n-1^n》的第四部分之间。

357.布线sotl《m,n-1^n》的第一部分被连接到字线wl《m》。布线sotl《m,n-1^n》的第二

部分被连接到写入位线wbl《n-1》。布线sotl《m,n-1^n》的第三部分被连接到读取位线rbl《n-1》。布线sotl《m,n-1^n》的第四部分被连接到写入位线wbl《n》。布线sotl《m,n-1^n》的第五部分被连接到读取位线rbl《n》。

358.开关元件sel1《m,n-1》被连接在布线sotl《m,n-1^n》的第二部分与写入位线wbl《n-1》之间。磁阻效应元件mtj《m,n-1》被连接在布线sotl《m,n-1^n》的第三部分与读取位线rbl《n-1》之间。开关元件sel2《m,n-1》被连接在磁阻效应元件mtj《m,n-1》与读取位线rbl《n-1》之间。

359.开关元件sel1《m,n》被连接在布线sotl《m,n-1^n》的第四部分与写入位线wbl《n》之间。磁阻效应元件mtj《m,n》被连接在布线sotl《m,n-1^n》的第五部分与读取位线rbl《n》之间。开关元件sel2《m,n》被连接在磁阻效应元件mtj《m,n》与读取位线rbl《n》之间。

360.6.2存储单元阵列的平面布局

361.图34是示出根据第六实施例的存储单元阵列的平面布局的示例的平面图。图34对应于根据第三实施例的图28。

362.存储单元阵列10包括垂直结构v1、垂直结构v2和垂直结构v3。每一个垂直结构v1包括开关元件sel1。每一个垂直结构v2包括磁阻效应元件mtj和开关元件sel2。

363.多个字线wl被布置在y方向上。每一个字线wl在x方向上延伸。

364.多个写入位线wbl被提供在多个字线wl的上方。多个写入位线wbl被布置在x方向上。每一个写入位线wbl在y方向上延伸。

365.多个布线sotl被提供在多个写入位线wbl的上方。在平面图中,每一个布线sotl具有矩形形状。多个布线sotl的长边方向和短边方向分别平行于x方向和y方向。也就是说,布线sotl的长边方向与写入位线wbl正交。在平面图中,多个布线sotl中的每一个被提供在与一个字线wl、两个相邻的写入位线wbl和两个相邻的读取位线rbl重叠的位置处。

366.多个读取位线rbl被提供在多个布线sotl的上方。多个读取位线rbl被布置在x方向上。每一个读取位线rbl在y方向上延伸。在平面图中,两个读取位线rbl被提供在两个相邻的写入位线wbl之间。

367.垂直结构v1在z方向上延伸。在平面图中,垂直结构v1每一个具有圆形形状。每一个垂直结构v1被连接在一个对应的写入位线wbl与一个对应的布线sotl之间。

368.垂直结构v2在z方向上延伸。在平面图中,垂直结构v2每一个具有圆形形状。每一个垂直结构v2被连接在一个对应的读取位线rbl与一个对应的布线sotl之间。

369.垂直结构v3在z方向上延伸。在平面图中,垂直结构v3每一个具有圆形形状。每一个垂直结构v3被连接在一个对应的字线wl与一个对应的布线sotl之间。

370.在如上的配置中,包括一个布线sotl以及连接到一个对应的布线sotl的一个垂直结构v1、一个垂直结构v2和一个垂直结构v3的组用作一个存储单元mc。而且,布线sotl和垂直结构v3由两个存储单元mc共享。

371.分别为共享布线sotl的两个存储单元mc提供的两个垂直结构v2被布置在x方向上。在平面图中,垂直结构v2的中心位于布线sotl的沿着x方向的对称轴上。也就是说,分别为共享相同布线sotl的两个存储单元mc提供的布线sotl和两个垂直结构v2沿着x方向被提供在相同的轴上。

372.6.3根据第六实施例的效果

373.根据第六实施例,布线sotl具有矩形形状,其长边在与写入位线wbl和读取位线以90度相交的方向上延伸。因此,当字线wl由两个存储单元共享时,可以设置磁阻效应元件mtj。

374.在平面图中,共享布线sotl的两个垂直结构v2被提供在与对应的布线sotl相同的轴上。因此,与垂直结构v2未被提供在与布线sotl相同的轴上的情况相比,可以增加磁阻效应元件mtj与布线sotl之间的接触面积。因此,以与第三实施例相同的方式,在写操作期间,布线sotl可以将更大的自旋轨道矩注入磁阻效应元件mtj。

375.根据第一实施例的第一修改例、第一实施例的第二修改例和第一实施例的第三修改例的配置和操作可以应用于根据第六实施例的磁存储设备。在这种情况下,根据第六实施例的磁存储设备可以展现与第一实施例的第一修改例、第一实施例的第二修改例和第一实施例的第三修改例相同的效果。

376.7.其他

377.在上文所描述的第一至第六实施例以及第一至第三修改例中,示出了其中两个层级结构l1和l2被堆叠在半导体衬底20之上的存储单元阵列10,但实施例不限于此。例如,具有相同结构的三个或更多个层级结构可以被堆叠在半导体衬底20之上。例如,一个层级结构可以被堆叠在半导体衬底20之上。

378.尽管已经描述了某些实施例,但是这些实施例仅以示例的方式呈现,并且不旨在限制本公开的范围。实际上,可以以各种其他形式实现本文所描述的新颖实施例;此外,可以做出本文所描述的实施例的形式的各种省略、替代和改变而不脱离本公开的精神。所附的权利要求及其等同物旨在覆盖如落入本公开的范围和精神内的这种形式或修改。

379.标记的解释

380.1:磁存储设备

381.10:存储单元阵列

382.11:行选择电路

383.12:列选择电路

384.13:解码电路

385.14:写电路

386.15:读电路

387.16:电压产生电路

388.17:输入/输出电路

389.18:控制电路

390.20:半导体衬底

391.21、23、24、25、29、31、32、34、36、38、41、42、43、46、47、48、49、54、55、56、57、58、61、62、63、64、65、70、71:导体层

392.22、27、28、33、35、37、44、45、50、51、52、53、59、60、66、67、68、69:元件层

393.24a:反铁磁层

394.24b、27a、27a'、27c、27c'、27e、27e':铁磁层

395.24c、24c'、27b、27d:非磁性层

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。