1.本发明涉及一种用于常开型晶体管的共源共栅电路(cascode circuit),且特别涉及一种具有金属栅极mosfet(金氧半场效晶体管)与常开型晶体管的半导体装置。

背景技术:

2.常开型(d-mode)gan元件需要通过封装技术与低压硅(lv si)mosfet结合使用,以成为正常操作用的共源共栅结构。

3.然而,当系统进行开/关切换(turn-on/turn-off transition)时,氮化镓(gan)元件的源极和低压硅mosfet的漏极之间的瞬间高压约比gan元件的阈值电压(vt)要大两倍以上,因此这样的高压可能因为寄生效应而损坏元件。

4.再者,如果gan元件的源极和低压硅mosfet的漏极之间的电压被加到高压,则在系统进行开/关转换时,还可能会发生gan元件的栅极和低压硅mosfet的栅极的损坏以及低压硅mosfet的漏极结的损坏。

技术实现要素:

5.本发明是针对一种半导体装置,能避免开型gan元件和低压硅场效晶体管(low voltage silicon field effect transistor)的栅极以及低压硅场效晶体管的漏极结的损坏。

6.本发明是针对另一种半导体装置,可降低寄生效应并且避免半导体装置因过高的电压而损坏。

7.根据本发明的实施例,一种半导体装置包括一基板、常开型gan元件、低压硅场效晶体管以及金属栅极mosfet。常开型gan元件与金属栅极mosfet都形成于所述基板上,低压硅场效晶体管则耦接至所述常开型gan元件,其中所述金属栅极mosfet的金属栅极与源极耦接至所述低压硅场效晶体管,且所述金属栅极mosfet的漏极耦接至所述常开型gan元件。

8.在根据本发明的实施例的半导体装置中,上述金属栅极mosfet的源极与金属栅极耦接至上述低压硅场效晶体管的源极。

9.在根据本发明的实施例的半导体装置中,上述金属栅极mosfet的漏极耦接至上述常开型gan元件的源极。

10.在根据本发明的实施例的半导体装置中,上述低压硅场效晶体管的漏极耦接至所述常开型gan元件的源极。

11.根据本发明的另一实施例,一种半导体装置包括一基板、常开型gan元件以及金属栅极mosfet。常开型gan元件与金属栅极mosfet都形成于所述基板上,其中所述常开型gan元件包括源极、漏极与栅极。所述金属栅极mosfet的金属栅极耦接至一控制端,所述金属栅极mosfet的源极与所述基板接触并耦接至常开型gan元件的所述栅极,且所述金属栅极mosfet的漏极与所述基板接触并耦接至常开型gan元件的所述源极。

12.在根据本发明的另一实施例的半导体装置中,上述金属栅极mosfet与上述常开型

gan元件具有相同的接地(gnd)电位。

13.在根据本发明的所有实施例的半导体装置中,上述金属栅极mosfet还可包括多个第一导电型掺杂区以及第二导电型掺杂区。第一导电型掺杂区分别形成于金属栅极mosfet的所述金属栅极两侧的基板内。第二导电型掺杂区则形成于金属栅极mosfet的所述源极下方的基板内并且与所述金属栅极之间以上述第一导电型掺杂区隔开。

14.在根据本发明的所有实施例的半导体装置中,上述常开型gan元件包括形成于所述基板的表面的缓冲层、形成于所述缓冲层上的信道层、形成于所述信道层上的障壁层、穿过所述障壁层与所述信道层接触的上述源极与上述漏极、形成于所述障壁层上的上述栅极。

15.基于上述,在本发明的半导体装置中,于常开型gan元件与低压硅场效晶体管的共源共栅电路中另外增设一个金属栅极mosfet作为箝制二极管(clamp diode),因此可抑制电压不必要的升高,以便在系统进行开/关转换时,避免开型gan元件和低压硅场效晶体管的栅极的损坏以及避免低压硅场效晶体管的漏极结的损坏。另外,若是将金属栅极mosfet取代低压硅场效晶体管,则因为这个金属栅极mosfet是与常开型gan元件形成在同一基板上,所以不但能因为两者连线距离短而大幅降低寄生效应,还可通过金属栅极mosfet与常开型gan元件之间相同的接地(gnd)电位,而使常开型gan元件的源极与金属栅极mosfet的漏极之间的电压下降至接近常开型gan元件的阈值电压(vt)的绝对值,进而避免半导体装置的损坏。

16.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

17.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。在附图中:

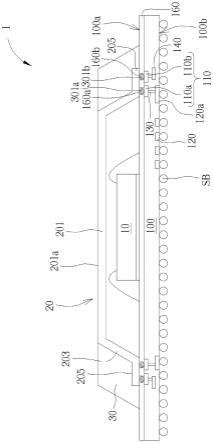

18.图1是依照本发明的第一实施例的一种半导体装置的剖面示意图。

19.图2是图1的半导体装置的等效电路图。

20.图3是依照本发明的第二实施例的一种半导体装置的剖面示意图。

21.图4是图3的半导体装置的等效电路图。

22.附图标记

23.100:基板

24.110:常开型gan元件

25.112:缓冲层

26.114:信道层

27.116:障壁层

28.118:顶盖层

29.120:低压硅场效晶体管

30.130:金属栅极mosfet

31.132:第一导电型掺杂区

32.134:第二导电型掺杂区

33.136:栅极绝缘层

34.2deg:二维电子气

35.d1、d2、d3:漏极

36.g1、g2:栅极

37.mg:金属栅极

38.s1、s2、s3:源极

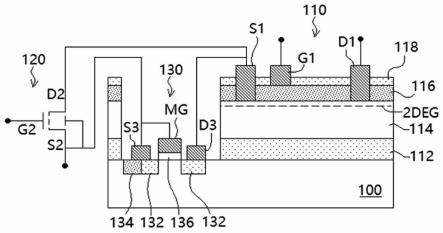

具体实施方式

39.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。此外,为了清楚起见,各个区域或膜层的相对厚度、距离及位置可能缩小或放大。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

40.图1是依照本发明的第一实施例的一种半导体装置的剖面示意图。

41.请参照图1,本实施例的半导体装置包括基板100、常开型gan元件110、低压硅(lp si)场效晶体管120以及金属栅极mosfet(金氧半场效晶体管)130。常开型gan元件110形成于基板100上,金属栅极mosfet 130形成于同一基板100上。低压硅场效晶体管120则耦接至常开型gan元件110,以构成一个共源共栅的gan电路半导体装置,使常开型gan元件110通过低压硅场效晶体管120控制成为常关型元件(或称e-mode元件),其线路连接例如通过封装技术将低压硅场效晶体管120的漏极d2耦接至常开型gan元件110的源极s1,栅极g2则可连至一栅极驱动器(未示出)。在本实施例中,金属栅极mosfet 130的金属栅极mg与源极s3耦接至低压硅场效晶体管120,如耦接至低压硅场效晶体管120的源极s2;金属栅极mosfet130的漏极d3则耦接至常开型gan元件110,如耦接至常开型gan元件110的源极s1。因此,金属栅极mosfet 130可作为箝制二极管(clamp diode),在系统进行开/关转换(turn-on/turn-off transition)时,防止由低压硅场效晶体管120的漏极d2传送至常开型gan元件110的源极s1的电压持续上升到雪崩电压。

42.在图1中,常开型gan元件110包括形成于基板100的表面的缓冲层112、形成于缓冲层112上的信道层114、形成于信道层114上的障壁层116、穿过障壁层116与信道层114接触的源极s1与漏极d1以及形成于障壁层116上的栅极g1。缓冲层112可减缓后续形成于缓冲层112上方的信道层114的应变,并具有防止缺陷形成于信道层114的效果,缓冲层112的材料可列举但不限于氮化铝、氮化镓、氮化镓铝或前述组合。信道层114可以是由未掺杂的氮化镓(gan)所形成。障壁层116的材料是未掺杂的iii-v族半导体材料,可列举但不限于氮化镓铝或者其他适当的iii-v族材料。信道层114与障壁层116为异质材料,以于信道层114与障壁层116之间形成一异质界面,借由异质材料的能隙差(band gap),可使二维电子气(two-dimensional electron gas)2deg形成于此异质界面上。此外,在障壁层116上可成长顶盖层118保护下方膜层,其中障壁层116的材料例如氮化硅或者其他适当的材料。常开型gan元件110中的各层均可利用外延工艺形成外延结构,其中外延工艺例如金属有机化学气相沉积(mocvd)、氢化物气相外延法(hvpe)、分子束外延法(mbe)或前述方法的组合。

43.在图1中,金属栅极mosfet 130还可包括多个第一导电型掺杂区132与第二导电型

掺杂区134。第一导电型掺杂区132分别形成于金属栅极mosfet 130的金属栅极mg两侧的基板100内,而第二导电型掺杂区134形成于金属栅极mosfet 130的源极s3下方的基板100内并且与金属栅极mg之间以第一导电型掺杂区132隔开。也就是说,源极s3底下有两个不同导电型的掺杂区与其接触。在一实施例中,第一导电型掺杂区132是n 型掺杂区、第二导电型掺杂区134是p 型掺杂区;在另一实施例中,第一导电型掺杂区132是p 型掺杂区、第二导电型掺杂区134是n 型掺杂区。而在金属栅极mg与基板100之间设有栅极绝缘层136。至于金属栅极mosfet130的制作方式例如但不限于,在前述常开型gan元件110的外延结构形成后以及在电极(源极s1、漏极d1、栅极g1)形成前,先移除预定形成金属栅极mosfet 130的区域内的外延结构,再利用离子注入等方式于部分基板100内形成第一导电型掺杂区132与第二导电型掺杂区134,接续形成常开型gan元件110的源极s1与漏极d1,然后常开型gan元件110的栅极g1可与金属栅极mosfet 130的源极s3、漏极d3以及金属栅极mg一同形成,且形成金属栅极mg之前通常有栅极绝缘层136的形成步骤。前述步骤可包括沉积、光刻、蚀刻(etching)等工艺,但本发明并不限于此。

44.图2是图1的半导体装置的等效电路图。由于金属栅极mosfet 130的金属栅极mg与源极s3耦接至低压硅场效晶体管120的源极s2,所以可避免共源共栅电路(cascode circuit)的雪崩击穿(avalanche breakdown),进而保护常开型gan元件110。

45.图3是依照本发明的第二实施例的一种半导体装置的剖面示意图,其中使用与第一实施例相同的元件符号来表示相同或近似的部分与构件,且相同或近似的部分与构件的相关内容也可参照第一实施例的内容,不再赘述。

46.请参照图3,本实施例的半导体装置包括基板100、常开型gan元件110以及金属栅极mosfet 130。常开型gan元件110与金属栅极mosfet 130形成于同一基板100上。所述金属栅极mosfet 130的金属栅极mg耦接至一控制端,金属栅极mosfet 130的源极s3与基板100接触并耦接至常开型gan元件110的栅极g1,且金属栅极mosfet 130的漏极d3与基板100接触并耦接至常开型gan元件110的源极s1。至于常开型gan元件110的详细结构与金属栅极mosfet 130的详细结构均可参照第一实施例所述,于此不再赘述。

47.也就是说,第二实施例是用金属栅极mosfet 130取代第一实施例中的低压硅场效晶体管,而与常开型gan元件110组成共源共栅电路,请对照图4的等效电路。因为金属栅极mosfet 130是与常开型gan元件110是形成在同一基板100上,所以不但能因为两者连线(wire connection)距离大幅缩短而能降低寄生效应,还可通过金属栅极mosfet 130与常开型gan元件110之间相同的接地(gnd)电位,而使常开型gan元件110的源极s1与金属栅极mosfet 130的漏极d3之间的电压下降至接近常开型gan元件110的阈值电压(vt)的绝对值,进而避免半导体装置的损坏。

48.综上所述,本发明通过特定的元件设计,在常开型晶体管的共源共栅电路中增加金属栅极mosfet作为箝制二极管,或是直接使用同一基板上的金属栅极mosfet取代低压硅场效晶体管,以便在系统进行开/关转换时,防止半导体装置的损坏。

49.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术

方案的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。