技术特征:

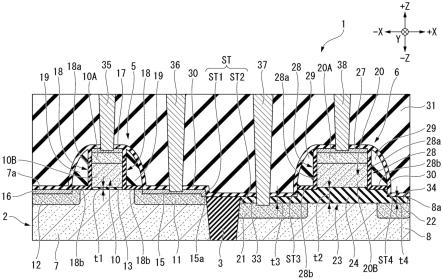

1.一种半导体装置,具备:衬底;多个晶体管,设置于所述衬底上;积层膜,设置于所述多个晶体管的上方,包含在第1方向上互相隔开的多个电极层,且具有第1区域、相对于所述第1区域位于与所述第1方向交叉的第2方向侧的第2区域、及相对于所述第1区域位于所述第2方向的相反侧的第3区域;多个插塞,在所述第1区域内,分别设置于所述多个电极层;第1柱状部,设置于所述第2区域内,包含在所述第1方向延伸的第1半导体层、及设置于所述第1半导体层与所述多个电极层间的第1电荷累积层;及第2柱状部,设置于所述第3区域内,包含在所述第1方向延伸的第2半导体层、及设置于所述第2半导体层与所述多个电极层间的第2电荷累积层;且所述多个电极层中的至少1个电极层是包含所述第1区域内所含的第1部分、所述第2区域内所含的第2部分、及所述第3区域内所含的第3部分,且从所述第2部分经由所述第1部分到达所述第3部分的连续膜;所述多个晶体管包含:第1晶体管,设置于所述第1区域的正下,且电连接于所述多个插塞中的第1插塞;第2晶体管,设置于所述第2区域的正下,且电连接于所述多个插塞中的第2插塞;及第3晶体管,设置于所述第3区域的正下,且电连接于所述多个插塞中的第3插塞。2.根据权利要求1所述的半导体装置,还具备:多条布线,将所述多个插塞分别与所述多个晶体管电连接;所述多条布线包含到达所述第2区域的正下区域的布线、及到达所述第3区域的正下区域的布线。3.根据权利要求1所述的半导体装置,其中所述多个电极层依序包含在所述第1方向上互相隔开的第1到第n电极层(n为2以上的整数);所述多个插塞包含分别设置于所述第1到第n电极层的第1到第n连接插塞。4.根据权利要求3所述的半导体装置,其中所述第1到第n连接插塞中的第k连接插塞(k为满足2≦k≦n的整数)贯通所述第1到第n电极层中的第1到第k-1电极层,与所述第1到第n电极层中的第k电极层相接。5.根据权利要求3或4所述的半导体装置,还具备:第1到第n布线,将所述第1到第n连接插塞分别与所述第2晶体管电连接;所述第1到第n布线分别相对于所述第1到第n连接插塞位于所述第2区域侧或所述第3区域侧。6.根据权利要求5所述的半导体装置,其中所述第1到第n布线中的第k1布线(k1为满足1≦k1≦n/2的整数)相对于所述第1到第n连接插塞中的第k1连接插塞位于所述第2区域侧;所述第1到第n布线中的第k2布线(k2为满足n/2<k2≦n的整数)相对于所述第1到第n连接插塞中的第k2连接插塞位于所述第3区域侧。7.根据权利要求5所述的半导体装置,其中所述第1到第n布线各自包含彼此相接的一对焊垫。

8.根据权利要求3所述的半导体装置,其中所述第1区域包含互相分离的第1部分区域及第2部分区域;所述第1到第n连接插塞设置于所述第1部分区域及所述第2部分区域内。9.根据权利要求8所述的半导体装置,其中所述第2区域相对于所述第1部分区域位于所述第2方向侧;所述第3区域相对于所述第2部分区域位于所述第2方向的相反侧。10.根据权利要求8所述的半导体装置,其中所述第2区域包含互相分离的第3部分区域及第4部分区域;所述第3区域包含互相分离的第5部分区域及第6部分区域;所述第3部分区域相对于所述第1部分区域位于所述第2方向侧;所述第4部分区域相对于所述第2部分区域位于所述第2方向侧;所述第5部分区域相对于所述第1部分区域位于所述第2方向的相反侧;所述第6部分区域相对于所述第2部分区域位于所述第2方向的相反侧。11.根据权利要求10所述的半导体装置,其中所述第1区域包含互相分离的多个第1部分区域,作为所述第1部分区域,且包含互相分离的多个第2部分区域,作为所述第2部分区域;所述第3部分区域相对于任一个第1部分区域位于所述第2方向侧;所述第4部分区域相对于任一个第2部分区域位于所述第2方向侧;所述第5部分区域相对于另一个第1部分区域位于所述第2方向的相反侧;所述第6部分区域相对于另一个第2部分区域位于所述第2方向的相反侧。12.根据权利要求8所述的半导体装置,其中所述第1部分区域包含所述第1到第n连接插塞中的第ka到第kb连接插塞;所述第2部分区域包含所述第1到第n连接插塞中的第kc到第kd连接插塞;ka、kb、kc、kd为满足1≦ka≦kb<kc≦kd≦n的整数。13.根据权利要求8所述的半导体装置,其中所述第1部分区域包含所述第1到第n插塞中的第k3连接插塞(k3为满足1≦k1≦n的奇数);所述第2部分区域包含所述第1到第n插塞中的第k4连接插塞(k4为满足1≦k2≦n的偶数)。14.一种半导体装置,具备:衬底;多个晶体管,设置于所述衬底上;第1积层膜,设置于所述多个晶体管的上方,包含在第1方向上互相隔开的多个第1电极层,且具有第1区域、相对于所述第1区域位于与所述第1方向交叉的第2方向侧的第2区域、及相对于所述第1区域位于所述第2方向的相反侧的第3区域;第2积层膜,相对于所述第1积层膜位于与所述第1及第2方向交叉的第3方向侧,包含在所述第1方向上互相隔开的多个第2电极层,具有相对于所述第3区域位于所述第3方向侧的第4区域、相对于所述第4区域位于所述第2方向侧的第5区域、及相对于所述第4区域位于所述第2方向的相反侧的第6区域;

多个第1电极层插塞,在所述第1区域内,分别设置于所述多个第1电极层;第1柱状部,设置于所述第2区域内,包含在所述第1方向延伸的第1半导体层、及设置于所述第1半导体层与所述多个第1电极层间的第1电荷累积层;第2柱状部,设置于所述第3区域内,包含在所述第1方向延伸的第2半导体层、及设置于所述第2半导体层与所述多个第1电极层间的第2电荷累积层;多个第2电极层插塞,在所述第4区域内,分别设置于所述多个第2电极层;第3柱状部,设置于所述第5区域内,包含在所述第1方向延伸的第3半导体层、及设置于所述第3半导体层与所述多个第2电极层间的第3电荷累积层;及第4柱状部,设置于所述第6区域内,包含在所述第1方向延伸的第4半导体层、及设置于所述第4半导体层与所述多个第2电极层间的第4电荷累积层;且所述多个第1电极层中的至少1个第1电极层是包含所述第1区域内所含的第1部分、所述第2区域内所含的第2部分、及所述第3区域内所含的第3部分,且从所述第2部分经由所述第1部分到达所述第3部分的连续膜;所述多个第2电极层中的至少1个第2电极层是包含所述第4区域内所含的第4部分、所述第5区域内所含的第5部分、及所述第6区域内所含的第6部分,且从所述第5部分经由所述第4部分到达所述第6部分的连续膜;所述多个晶体管包含:第1晶体管,设置于所述第1区域的正下,且电连接于所述多个第1电极层插塞中的第1插塞;第2晶体管,设置于所述第2区域的正下,且电连接于所述多个第1电极层插塞中的第2插塞;第3晶体管,设置于所述第4区域的正下,且电连接于所述多个第2电极层插塞中的第3插塞;及第4晶体管,设置于所述第6区域的正下,且电连接于所述多个第2电极层插塞中的第4插塞。15.根据权利要求14所述的半导体装置,还具备:多条第1布线,将所述多个第1电极层插塞分别与所述多个晶体管电连接;及多条第2布线,将所述多个第2电极层插塞分别与所述多个晶体管电连接;且所述多条第1布线包含到达所述第2区域的正下区域的布线;所述多条第2布线包含到达所述第6区域的正下区域的布线。16.根据权利要求14或15所述的半导体装置,其中所述多个第2电极层与所述多个第1电极层分断。17.一种半导体装置的制造方法,包含:在第1衬底上形成多个晶体管;在第2衬底上形成积层膜,所述积层膜包含在第1方向上互相隔开的多个层,且具有第1区域、相对于所述第1区域位于与所述第1方向交叉的第2方向侧的第2区域、及相对于所述第1区域位于所述第2方向的相反侧的第3区域;在所述第2区域内形成第1柱状部,所述第1柱状部包含在所述第1方向延伸的第1半导体层、及设置于所述第1半导体层与所述多个电极层间的第1电荷累积层;在所述第3区域内形成第2柱状部,所述第2柱状部包含在所述第1方向延伸的第2半导体层、及设置于所述第2半导体层与所述多个电极层间的第2电荷累积层;将所述多个层分别置换为多个电极层;在所述第1区域内,形成分别设置于所述多个电极层的多个插塞;

使所述第1衬底与所述第2衬底贴合,将所述多个插塞分别与所述多个晶体管电连接;且所述多个电极层中的至少1个电极层是包含所述第1区域内所含的第1部分、所述第2区域内所含的第2部分、及所述第3区域内所含的第3部分,且从所述第2部分经由所述第1部分到达所述第3部分的连续膜;所述多个晶体管形成为包含:第1晶体管,设置于所述第1区域的正下,且电连接于所述多个插塞中的第1插塞;第2晶体管,设置于所述第2区域的正下,且电连接于所述多个插塞中的第2插塞;及第3晶体管,设置于所述第3区域的正下,且电连接于所述多个插塞中的第3插塞。18.一种半导体装置,具备:衬底;多个晶体管,设置于所述衬底上;积层膜,设置于所述多个晶体管的上方,包含在第1方向上互相隔开的多个电极层,且具有第1区域、及相对于所述第1区域位于与所述第1方向交叉的第2方向侧的第2区域;多个插塞,在所述第1区域内,分别设置于所述多个电极层;多个柱状部,设置于所述第2区域内,包含在所述第1方向延伸的半导体层、及设置于所述半导体层与所述多个电极层间的电荷累积层,分别与所述多个晶体管电连接;且所述多个电极层中的至少1个电极层是包含所述第1区域内所含的第1部分、及所述第2区域内所含的第2部分,且从所述第1部分到达所述第2部分的连续膜;所述多个晶体管包含:第1晶体管,设置于所述第1区域的正下,且电连接于所述多个插塞中的第1插塞;及第2晶体管,设置于所述第2区域的正下,且电连接于所述多个插塞中的第2插塞。19.根据权利要求18所述的半导体装置,其中所述多个晶体管依序包含在所述第1方向上互相隔开的第1到第n电极层(n为2以上的整数);所述多个插塞包含分别设置于所述第1到第n电极层的第1到第n连接插塞。20.根据权利要求19所述的半导体装置,其中所述第1到第n连接插塞中的第k连接插塞(k为满足2≦k≦n的整数)不贯通所述第1到第n电极层中的第1到第k-1电极层,而与所述第1到第n电极层中的第k电极层相接。

技术总结

实施方式提供一种能够降低布线密度的半导体装置及其制造方法。根据一实施方式,半导体装置具备:衬底;多个晶体管,设置于衬底上;及积层膜,设置于多个晶体管的上方,包含在第1方向上互相隔开的多个电极层,具有第1、第2及第3区域。所述装置还具备:多个插塞,在第1区域内,设置于多个电极层;第1柱状部,设置于第2区域内;及第2柱状部,设置于第3区域内。多个电极层中的至少1个电极层是包含第1区域所含的第1部分、第2区域所含的第2部分、及第3区域所含的第3部分,且从第2部分经由第1部分到达第3部分的连续膜。多个晶体管分别包含在第1、第2及第3区域的正下方,电连接于第1、第2及第3插塞的第1、第2及第3晶体管。第2及第3晶体管。第2及第3晶体管。

技术研发人员:中塚圭祐 大冈拓也

受保护的技术使用者:铠侠股份有限公司

技术研发日:2022.02.21

技术公布日:2023/2/17

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。