1.本公开涉及一种包括具有主元件的主区域和具有感测元件的感测区域的半导体器件。

背景技术:

2.例如,jp 2018-101737 a公开了一种包括主区域和感测区域的半导体器件。主元件形成在主区域处,并且感测元件形成在感测区域处。在该半导体器件中,通用的绝缘栅双极晶体管(igbt)形成为主元件和感测元件。主元件和感测元件,换言之,主区域和感测区域形成为具有预定的面积比。

3.在这样的半导体器件中,检测电阻与感测元件串联连接,并且流过主元件的主电流形成为用于检测所述检测电阻两端的电压的检测信号。换言之,流过感测元件的感测电流基于检测信号导出。流过主元件的电流和流过感测元件的电流取决于主元件的面积(area)与感测元件的面积之比。因此,流过主元件的主电流由流过感测元件的感测电流和主元件的面积与感测元件的面积之比导出。

技术实现要素:

4.上述这样的半导体器件还可以基于检测信号来确定该半导体器件是处于稳定状态(换言之,正常状态或静止状态)还是故障状态。因此,在上述这样的半导体器件中,能够通过放大基于在稳定状态下的稳定检测信号的电平与故障状态下的故障检测信号的电平之间的差而获得的差分电压来禁止错误确定。

5.例如,为了放大差分电压,饱和电流被放大以放大故障检测信号的电平,并且为了放大差分电压,igbt元件中的杂质浓度被增大。但是,在这样的结构中,由关断半导体器件引起的切换损耗(switching loss)可能增加。

6.本公开的一个目的在于提供一种半导体器件,该半导体器件能够放大基于稳定检测信号的电平与故障检测信号的电平之间的差而获得的差分电压,同时抑制由关断半导体器件引起的切换损耗的增加。

7.根据本公开的一个方面,一种半导体器件包括布置在主区域处的主元件和布置在感测区域处的感测元件。主元件允许主电流流过主元件,并且感测元件允许感测电流流过感测元件。基于流过感测元件的感测电流来检测流过主元件的主电流。主元件和感测元件中的每一个包括第一导电类型的漂移层、第二导电类型的基极层、所述第一导电类型的发射极区、栅极绝缘膜、栅电极、背面层、第一电极和第二电极。所述基极层布置在所述漂移层上。所述发射极区布置在所述基极层的表面层部分处,并且具有比所述漂移层高的杂质浓度。所述栅极绝缘膜布置在所述基极层的介于所述发射极区和所述漂移层之间的表面上。所述栅电极布置在所述栅极绝缘膜上。所述背面层布置在面对所述基极层的一侧,所述漂移层介于所述背面层和所述基极层之间。所述第一电极电连接到所述发射极区和所述基极层。所述第二电极电连接到所述背面层。所述主元件中的背所述面层包括所述第二导电类

型的集电极层。所述感测元件中的所述背面层包括沿所述漂移层和所述基极层的堆叠方向的杂质含量比所述集电极层低的所述第二导电类型的低杂质层。

8.感测元件包括低杂质层,并且载流子,例如来自背面层的空穴,的注入被抑制。因此,能够降低在稳定状态下流过感测元件的感测电流的水平,并且能够降低稳定检测信号的电平。能够充分放大基于稳定检测信号的电平与故障检测信号的电平之间的差而获得的差分电压。在该半导体器件中,由于不需要将集电极层的杂质浓度增大到大于必需水平,因此能够抑制因关断半导体器件引起的切换损耗的增加。

附图说明

9.本公开的上述目的、特征和优点将从以下结合附图的详细描述而变得更加明显。在附图中:

10.图1是根据第一实施例的半导体器件的平面图;

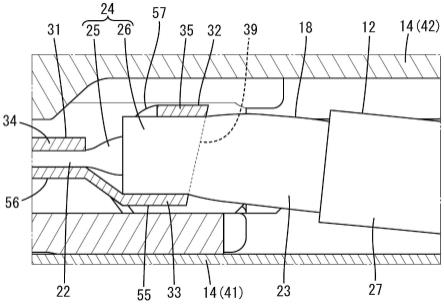

11.图2是沿图1所示的线ii-ii截取的半导体器件的横截面图;

12.图3是沿图1所示的线iii-iii截取的半导体器件的横截面图;

13.图4是图1的区域iv中的半导体衬底的第二表面的平面图;

14.图5是其中检测电阻连接到感测元件的电路图;

15.图6是示出用于获取稳定检测信号(steady detected signal)的电路的电路图;

16.图7示出根据比较例的半导体器件中的稳定检测信号;

17.图8示出根据第一实施例的半导体器件中的稳定检测信号;

18.图9是图8的区域ix的放大图;

19.图10是示出用于获取故障检测信号的电路的电路图;

20.图11示出根据比较例的半导体器件中的故障检测信号和根据第一实施例的半导体器件中的故障检测信号;

21.图12示出根据比较例的半导体器件中的稳定检测信号与故障检测信号之间的关系;

22.图13示出根据第一实施例的半导体器件中的稳定检测信号与故障检测信号之间的关系;

23.图14示出根据第一实施例的半导体器件中的稳定检测信号与故障检测信号之间的关系;

24.图15a是第一实施例的修改示例中的半导体衬底的第二表面的平面图;

25.图15b是第一实施例的修改示例中的半导体衬底的第二表面的平面图;

26.图15c是第一实施例的修改示例中的半导体衬底的第二表面的平面图;

27.图15d是第一实施例的修改示例中的半导体衬底的第二表面的平面图;

28.图15e是第一实施例的修改示例中的半导体衬底的第二表面的平面图;

29.图15f是第一实施例的修改示例中的半导体衬底的第二表面的平面图;

30.图15g是第一实施例的修改示例中的半导体衬底的第二表面的平面图;

31.图16是示出连接到根据第二实施例的半导体器件的检测电阻的电路图;

32.图17示出第一感测元件与第二感测元件的比例和稳定检测信号之间的关系;

33.图18示出第一感测元件与第二感测元件的比例和故障检测信号之间的关系;

electrode)15。栅极绝缘膜14形成为覆盖每个沟槽13的壁表面,并且由多晶硅等制成的栅电极15形成在栅极绝缘膜14上。因此,形成沟槽栅极结构(trench gate structure)。在下文中,沟槽13也可以用单数形式描述,即一个沟槽13。在本实施例中,沟槽13的壁表面的用于暴露基极层12的部分对应于基极层12的布置在后述的n

型发射极区16(n

-type emitter region)与漂移层11之间的表面。

52.发射极区16和被发射极区16夹在中间的p

型接触区17形成在基极层12的表面层部分处。发射极区16具有比漂移层11更高的杂质浓度,并且与沟槽13的侧表面接触。接触区17具有比基极层12更高的杂质浓度,并形成在面对沟槽13的一侧,发射极区16介于接触区17与沟槽13之间。

53.发射极区16在沟槽13之间的区域中沿着沟槽13的长度方向以杆状形状延伸以与沟槽13的侧表面接触。接触区17介于两个发射极区16之间,并且沿着沟槽13的长度方向以杆状形状延伸。换言之,接触区17沿发射极区16延伸。根据本实施例的接触区17形成为相对于半导体衬底10的第一表面10a比发射极区16更深。

54.在本实施例中,发射极区16形成在主区域rm和感测区域rs处,但不形成在周边区域rp处。在本实施例中,在更靠近半导体衬底10的第一表面10a的一侧,形成发射极区16的部分被设为主区域rm或感测区域rs;并且,不形成发射极区16的部分被设为周边区域rp。换言之,在更靠近半导体衬底10的第一表面10a的一侧,根据是否形成发射极区16来定义主区域rm、感测区域rs以及周边区域rp。

55.感测区域rs在更靠近半导体衬底10的第二表面10b一侧的平面区域大于感测区域rs在更靠近第一表面10a一侧的平面区域。具体地,在更靠近半导体衬底10的第二表面10b的一侧,比更靠近第一表面10a一侧的感测区域rs总共仅大所述半导体衬底10的厚度的区域被设为感测区域rs。在图1中,感测区域rs的更靠近第二表面10b一侧的区域由虚线表示;并且感测区域rs的更靠近第一表面10a一侧的区域由实线表示。

56.在基极层12上,换言之,在半导体衬底10的第一表面10a上,形成由硼磷硅玻璃(borophosphosilicate glass,bpsg)等制成的层间绝缘膜18。接触孔18a形成在层间绝缘膜18处。接触孔18a形成为暴露接触区17和发射极区16的一部分。

57.上电极19形成在层间绝缘膜18上。上电极19通过接触孔18a与发射极区16和接触区17电连接。在本实施例中,上电极19对应于第一电极。

58.n型场阻止层(field stop layer,下文简称为fs层)20形成在漂移层11面对基极层12的一侧。换句话说,fs层20形成在更靠近半导体衬底10的第二表面10b一侧。fs层20不是必然需要的,提供fs层20是为了通过防止耗尽层(depletion layer)的扩散来改善击穿电压和稳定损耗的特性,以及控制从半导体衬底10的第二表面10b一侧注入的空穴的注入量。

59.背面层21形成在面对漂移层11的一侧,fs层20介于漂移层11与背面层21之间。关于主区域rm,如图2和图4所示,p型集电极层21a形成为背面层21。另一方面,关于感测区域rs,如图3、图4所示,导电类型与集电极层21a相反的n型反向导电类型层21b形成为背面层21。即,在感测区域rs中,具有比集电极层21a更小量p型杂质的反向导电类型层(reverse conductivity-type layer)21b沿着半导体衬底10的厚度方向形成。在根据本实施例的感测区域rs中,整体地形成反向导电类型层21b,并且不形成集电极层21a。在根据本实施例的

感测区域rs中,在整个第二表面10b形成反向导电类型层21b。

60.根据本实施例,在周边区域rp处形成与在主区域rm中形成的集电极层相同的集电极层21a。在本实施例中,反向导电类型层21b对应于低杂质层。沿着半导体衬底10的厚度方向的方向也可以称为沿着漂移层11和基极层12的堆叠方向的方向。

61.下电极22形成在集电极层21a和反向导电类型层21b上。换言之,下电极22形成在半导体衬底10的第二表面10b处。在本实施例中,下电极22对应于第二电极。

62.上面已经描述了根据本实施例的半导体器件的配置。在本实施例中,n-型、n型和n-型对应第一导电类型,并且p型和p

型对应第二导电类型。

63.下面描述这种半导体器件的操作和有益效果。

64.在上述这样的半导体器件中,当将低于下电极22电压的电压施加到上电极19并且将大于或等于预定阈值电压的预定电压施加到栅电极15时,n型反型层(即沟道)形成在基极层12的与沟槽13接触的部分中。电子通过反型层(inversion layer)从发射极区16提供给漂移层11,并且空穴从集电极层21a提供给漂移层11。因此,通过电导调制(conductivity modulation)降低漂移层11的电阻值以开启半导体器件。

65.如图5所示,在这样的半导体器件中,检测电阻r连接到感测元件se的上电极19,并且以如下所述方式检测流过主元件me的主电流。在该半导体器件中,由于流过检测电阻r的电流和流过感测元件se的感测电流相等,因此基于作为检测电阻r的两端之间的电压的检测信号来检测流过感测元件se的感测电流。主元件me和感测元件se以预定的面积比形成。流过主元件me的主电流和流过感测元件se的感测电流与预定面积比成比例。基于面积比和感测电流导出流过主区域rm的主电流。

66.这样的半导体器件可以执行状态确定,以基于检测信号确定半导体器件是处于稳定状态还是故障状态。在这种情况下,可以通过放大基于稳定状态下的稳定检测信号(以下简称为稳定检测信号)的电平与故障状态下的故障检测信号(以下简称故障检测信号)的电平之间的差而获得的差分电压(differential voltage)来抑制错误确定。在根据本实施例的感测元件se中,背面层21包括反向导电类型层21b以放大稳定检测信号的电平与故障检测信号的电平之间的差。

67.与一个比较例的半导体器件中的稳定检测信号和故障检测信号进行比较来说明本实施例中的稳定检测信号和故障检测信号。在根据比较例的半导体器件中,使感测区域rs中的整个背面层21与主区域rm中的集电极层21a相同。下面描述在将主区域rm的面积与感测区域rs的面积之比设为3000:1的情况下的模拟结果。在将大于或等于预定阈值电压的电压施加到栅电极15之后,将时间t1与时间t2之间的检测信号设为稳定检测信号。时间t1是停止向栅电极15施加预定电压的时间。在将大于或等于预定阈值电压的电压施加到栅电极15之后,将时间t3与时间t4之间的检测信号设为故障检测信号。时间t3是停止向栅电极15施加预定电压的时间。

68.参照图7至图9描述通过图6所示的测试电路获得的稳定检测信号的模拟结果。在测试电路中,驱动电路(driv cirt)32通过调整电阻31连接到主元件me和感测元件se中的每一个的栅电极15,并且电源33的正电极连接到下电极22。二极管34连接到检测电阻r,并且检测电阻r连接到主元件me的上电极19和感测元件se的上电极19。

69.如图7所示,在根据比较例的半导体器件中,稳定检测信号(stea det sig)的电平

随着主电流(main cur)的水平(level)增加而增加。在根据本实施例的半导体器件中,由于将感测区域rs中的整个背面层21设为反向导电类型层21b,因此能够抑制从半导体衬底10的第二表面10b供给空穴。在根据本实施例的半导体器件中,如图8和图9所示,与根据比较例的半导体器件相比,感测电流的水平降低,并且稳定检测信号的电平变得足够小。根据本实施例的半导体器件中的稳定检测信号的电平随着主电流的水平增加而略微增加,但不会像根据比较例的半导体器件变化那么大。

70.参照图11描述通过图10所示的测试电路获取的故障检测信号的模拟结果。在测试电路中,驱动电路32通过调整电阻31连接到主元件me和感测元件se中每一个的栅电极15,并且电源33的正电极连接到下电极22。主元件me的上电极19和连接到感测元件se的上电极19的检测电阻r接地。图11和图12中每一个示出了在栅极-发射极电压vge设为15v左右的电压作为典型栅极驱动电压的情况下的故障检测信号。

71.如图11所示,在根据比较例(compa examp)的半导体器件中,在比稳定电流足够大的故障电流流过主元件的情况下,故障检测信号(fault det sig)的电平约为3.6v。在根据本实施例(pres emb)的半导体器件中,形成了反向导电类型层21b。但是,在大量故障电流流到主元件me的情况下,具有预定量的感测电流流到感测元件se,并且故障检测信号的电平约为2.9v。关于根据本实施例的半导体器件中的稳定检测信号和故障检测信号,与根据比较例的半导体器件中的稳定检测信号和故障检测信号相比,稳定检测信号的电平的下降率充分大于故障检测信号的电平的下降率。

72.根据比较例的半导体器件中的故障检测信号和稳定检测信号的叠加如图12所示。图13和图14示出根据本实施例的半导体器件中的故障检测信号和稳定检测信号的叠加。

73.在根据比较例的半导体器件中,如图12所示,稳定检测信号的电平随着主电流的水平的增加而增加,并且基于稳定检测信号的电平与故障检测信号的电平之间的差而获得的差分电压降低。例如,即使将半导体器件制造成使得故障检测信号的电平为约3.6v,在故障检测信号的实际电平由于例如设计变更而为约2.3v的情况下,稳定检测信号的电平也可能随着主电流的水平增加而变得大于故障检测信号的电平。例如,在图12中,当主电流的水平为约2600a时,稳定检测信号的电平变得大于故障检测信号的电平。在根据比较例的这样的半导体器件中,需要事先增大饱和电流以进一步增大故障检测信号。

74.在根据本实施例的半导体器件中,如图13和图14所示,稳定检测信号的电平被抑制到足够小的值,并且基于稳定检测信号的电平与故障检测信号的电平之间的差而获得的差分电压能够被充分放大。图14是图13中稳定检测信号的放大图。根据本实施例的半导体器件,即使主电流的水平变大,也能够禁止稳定检测信号的电平变得大于故障检测信号的电平的情形。在根据本实施例的半导体器件中,由于稳定检测信号通过形成反向导电类型层21b而设置为更小,所以感测元件se的电阻变大。因此,在根据本实施例的半导体器件中,在稳定状态下,感测电流变得难以流过感测元件se,从而能够提高设计饱和电流中的自由度。

75.根据如上所述的本实施例,感测元件se包括反向导电类型层21b,从而能够抑制从半导体衬底10的第二表面10b注入空穴。因为这个原因,能够减小在稳定状态下流过感测元件se的感测电流,并且能够充分地降低稳定检测信号的电平。能够充分地放大基于稳定检测信号的电平与故障检测信号的电平之间的差而获得的差分电压以禁止错误确定。

76.在根据本实施例的该半导体器件中,因为不需要增加主元件me中集电极层21a的杂质浓度到超过必要的水平,所以能够抑制由关断半导体器件引起的切换损耗的增加。

77.(第一实施例的修改)

78.下面将描述第一实施例的修改。在第一实施例中,感测区域rs处的背面层21可以不完全形成有反向导电类型层21b,背面层21可以形成为如图15a至15g所示。图15a至图15g中的每一个是在与图1的区域iv对应的部分处半导体衬底10的第二表面10b的平面图。

79.例如,如图15a所示,感测区域rs处的背面层21具有形成有反向导电类型层21b的内边缘部。集电极层21a也可以形成在背面层21处以围绕反向导电类型层21b。换言之,感测区域rs处的背面层21可以包括集电极层21a和反向导电类型层21b。

80.在这种情况下,反向导电类型层21b可以沿着与反向导电类型层21b的长度方向相同的方向形成在多个部分中,如图15b所示,或者可以沿着与反向导电类型层21b的长度方向相同的方向形成在仅单个部分中,如图15c所示。如图15b、15c所示,反向导电类型层21b沿着从感测区域rs朝向主区域rm的方向延伸。如图15d所示,反向导电类型层21b可以沿着与从感测区域rs朝向主区域rm的方向正交的方向延伸。如图15e所示,反向导电类型层21b可以具有沿着从感测区域rs朝向主区域rm的方向延伸的第一部分和沿着与从感测区域rs朝向主区域rm的方向正交的方向延伸的第二部分。第一部分和第二部分可以连接。此外,反向导电类型层21b可以形成为如图15f所示的点形状。在这种情况下,反向导电类型层21b可以形成为使得反向导电类型层21b的仅一部分被布置为如图15g所示。虽未特别图示,但反向导电类型层21b可以形成为上述形状的组合,也可以以其它形状形成。

81.(第二实施例)

82.下面描述第二实施例。与第一实施例相反,本实施例描述了多个感测元件se与主元件me并联地布置。换言之,多个感测元件se与主元件me并联地连接。其它配置与第一实施例相同,因此下文省略了对相同配置的说明。

83.如上所述,在根据比较例的半导体器件中,稳定检测信号的电平与故障检测信号的电平之间的差可以随着稳定检测信号的电平变大而变小。在根据第一实施例的半导体器件中,虽然能够充分地降低稳定检测信号的电平,但是当稳定检测信号的电平过低时,稳定状态下的主电流的检测精度可能降低。

84.因为这个原因,如图16所示,根据本实施例的半导体器件具有与主元件me并联连接的第一感测元件se1和第二感测元件se2。第一感测元件se1和第二感测元件se2具有不同的性能,换言之,特性。特别是,本实施例中的第一感测元件se1具有与主元件me相同的结构,并且作为背面层21的集电极层21a形成在整个感测区域rs处。另一方面,第二感测元件se2具有与第一实施例中描述的感测元件se相同的结构,并且作为背面层21的反向导电类型层21b形成在整个感测区域rs处。第一感测元件se1对应于第一感测元件部分,并且第二感测元件se2对应于第二感测元件部分。

85.在这样的半导体器件中,如图17和图18所示,通过调整第一感测元件se1的面积与第二感测元件se2的面积之比,能够容易地调整稳定检测信号的电平和故障检测信号的电平。特别是,如图17和图18所示,稳定检测信号和故障检测信号中每一个的电平随着第一感测元件se1的比例增大而增大。图17示出在主电流为1500a情况下的稳定检测信号。图18示出了在栅极-发射极电压vge被设为大约15v的电压作为典型栅极驱动电压的情况下的故障

检测信号。

86.如图19所示,基于稳定检测信号的电平与故障检测信号的电平之差所获得的差分电压随着第一感测元件se1的比例增大而容易减小。但是,如上所述,稳定检测信号的电平随着第一感测元件se1的比例增大而增大。因此,第一感测元件se1的面积与第二感测元件se2的面积的比例可以根据所要求的性能进行调整。在这种情况下,如图19所示,考虑到设计上的变化,稳定检测信号的电平可以设为不大于故障检测信号的电平。

87.本实施例中的稳定检测信号对应于通过与图6所示的测试电路相同的测试电路获得的模拟结果。类似地,本实施例中的故障检测信号对应于通过与图10所示的测试电路相同的测试电路获得的模拟结果。

88.根据以上说明的本实施例,由于感测元件se包括反向导电类型层21b,因此能够充分地降低稳定检测信号的电平以获得与第一实施例类似的效果。

89.在本实施例中,第一感测元件se1和第二感测元件se2并联地连接到主元件me。第一感测元件se1和第二感测元件se2具有不同的性能。因此,能够通过调整第一感测元件se1的面积与第二感测元件se2的面积的比例,容易地改变稳定检测信号的电平和故障检测信号的电平。

90.(第三实施例)

91.下面描述第三实施例。与第一实施例相反,本实施例描述了感测元件se的配置的修改。其它配置与第一实施例相同,因此以下省略对相同配的说明。

92.如图20所示,在本实施例的感测区域rs中,沿半导体衬底10的厚度方向形成p-型低杂质浓度层21c作为背面层21。低杂质浓度层21c具有比集电极层21a更小量的p型杂质。换言之,p-型低杂质浓度层21c具有比集电极层21a更小的剂量。

93.特别地,在本实施例中,主元件me中的集电极层21a和感测元件se中的低杂质浓度层21c分别通过从半导体衬底10的第二表面10b注入的离子而形成。本实施例中的低杂质浓度层21c距半导体衬底10的第二表面10b的深度与集电极层21a距半导体衬底10的第二表面10b的深度相同。但是,低杂质浓度层21c的峰值浓度比集电极层21a的峰值浓度低。图20是在与图1的区域iv对应的部分处半导体衬底10的第二表面的平面图。

94.如图21所示,在这样的感测元件se中,沿着距第二表面10b的深度(depth frm sec sur),低杂质浓度层21c的杂质浓度(impu conc)随着峰值浓度变低而变低。在图21中,集电极层21a的峰值浓度(peak conc)被设定为基准。例如,图21中所示的峰值浓度1/1与集电极层21a的峰值浓度相同。

95.如图22和图23所示,稳定检测信号的电平和故障检测信号的电平随着低杂质浓度层21c的峰值浓度变小而降低。但是,依赖于低杂质浓度层21c的峰值浓度的稳定检测信号的电平的下降率大于故障检测信号的电平的下降率。即使例如低杂质浓度层21c的峰值浓度是集电极层21a的峰值浓度的五十分之一(1/50),低杂质浓度层21c也是p型层。因此,与第一实施例中描述的背面层21是反向导电类型层21b的情况相比,稳定检测信号的电平和故障检测信号的电平变大。图22示出主电流为1000a的情况下的稳定检测信号。图23示出了在栅极和发射极之间的电压vge被设为大约15v的电压作为典型栅极驱动电压的情况下的故障检测信号。

96.如图24所示,基于稳定检测信号的电平与故障检测信号的电平之间的差所获得的

差分电压随着集电极层21a的峰值浓度(peak conc of coll layer)增加而容易减小。也就是说,随着低杂质浓度层21c的峰值电压增大,基于稳定检测信号的电平与故障检测信号的电平之间的差而获得的差分电压(diff volt)容易降低。因此,低杂质浓度层21c可以根据所要求的性能进行调整。在这种情况下,如图25所示,考虑到设计的变化,可优选将稳定检测信号的电平设定为不大于故障检测信号。换言之,在图25中,考虑到设计的变化,差分电压可以设为0v或更高。

97.本实施例中的稳定检测信号对应于通过与图6所示的测试电路相同的测试电路获得的模拟结果。类似地,本实施例中的故障检测信号对应于通过与图10所示的测试电路相同的测试电路获得的模拟结果。

98.根据如上所述的本实施例,感测元件se包括p-型低杂质浓度层21c。因此,可以获得与第一实施例相同的效果。

99.在本实施例中,感测元件se包括p-型低杂质浓度层21c。因此,与感测元件se的背面层21仅由反向导电类型层21b形成的情况相比,能够禁止感测元件se的稳定检测信号过度下降的情形。

100.(第三实施例的修改)

101.第三实施例描述了作为低杂质层的低杂质浓度层21c具有比集电极层21a的峰值浓度低的峰值浓度。但是,低杂质层可以如下所述地形成。例如,如图26所示,低杂质层(low impu layer)具有与集电极层(coll layer)21a相同的杂质浓度(impu conc)的峰值浓度。但是,低杂质层距半导体衬底10的第二表面10b的深度可以比集电极层21a浅,以减少低杂质层沿半导体衬底10的厚度方向的杂质量。换言之,低杂质层具有与集电极层21a相同的峰值浓度;但是,低杂质层可以具有比集电极层21a更小的厚度。

102.例如,集电极层21a和低杂质层如下所述地形成。换言之,通过在改变加速电压的同时执行多次离子注入来形成集电极层21a,并且通过执行一次离子注入来形成低杂质浓度层21c,从而形成集电极层21a和低杂质层。

103.在第三实施例中,与第一实施例的修改示例一样,低杂质浓度的形状可以适当地修改。感测元件se可以具有通过第三实施例和第一实施例的组合而形成为背面层21的反向导电类型层21b和低杂质浓度层21c。

104.(第四实施例)

105.下面描述第四实施例。与第一实施例相反,在本实施例中修改了主区域rm的配置。其它配置与第一实施例相同,因此以下省略了对相同配置的说明。

106.在根据本实施例的半导体器件中,如图27所示,主区域rm包括绝缘栅双极晶体管区域(igbt reg)1a和续流二极管(freewheeling diode)区域(fwd reg)1b。igbt元件形成在igbt区域1a处。fwd区域1b与igbt区域1a相邻,并用作fwd元件。也就是说,根据本实施例的半导体器件具有其中igbt区域1和fwd区域1b形成在公共的半导体衬底10上的反向导通(rc)igbt。在本实施例中,位于半导体衬底10的第二表面10b处的集电极层21a上方的部分设为igbt区域1a,并且位于半导体衬底10的第二表面10b处的阴极层21d上方的部分设为fwd区域1b。

107.igbt区域1a具有与第一实施例中的主区域rm相同的配置。在本实施例中,fwd区域1b在靠近半导体衬底10的第一表面10a的一侧具有与igbt区域的配置相同的配置。用于暴

露例如接触区17的接触孔18b和用于暴露栅电极15的接触孔18c形成在fwd区域1b中的层间绝缘膜18处。

108.上电极19通过fwd区域1b中的接触孔18b电连接到接触区17。即,本实施例中的上电极19用作在igbt区域1a中的发射极电极(emitter electrode),并用作二极管区域1b中的阳极。本实施例中的上电极19也与fwd区域1b的栅电极15电连接。fwd区域1b中的栅电极15具有与上电极19的电位相同的电位。

109.n型阴极层21d形成为更靠近半导体衬底10的第二表面10b的一侧的背面层21,邻近集电极层21a。在本实施例的半导体器件中,位于半导体衬底10的第二表面10b的集电极层21a上方的部分设为igbt区域1a,并且位于半导体衬底10的第二表面10b的阴极层21d上方的部分设为fwd区域1b。本实施例中的阴极层21d具有与感测区域rs中的反向导电类型层21b相同的杂质浓度,并且阴极层21d和反向导电类型层21b两者的深度相同。

110.根据以上说明的本实施例,由于感测元件se包括反向导电类型层21b,因此能够充分地降低稳定检测信号的电平,以获得与第一实施例相同的效果。

111.在本实施例中,半导体在主区域rm具有fwd区域1b。在fwd区域1b处的阴极层21d的杂质浓度与感测区域rs中的反向导电类型层21b的杂质浓度相同,并且阴极层21d的深度和反向导电类型层21b的深度相同。因此,在本实施例中,能够同时形成阴极层21d和反向导电类型层21b。因此,能够在不延长制造过程的情况下布置反向导电类型层21b。

112.(第四实施例的修改)

113.下面描述第四实施例的修改。在第四实施例中,可以适当地修改fwd区域1b的配置。例如,栅电极15和发射极区16可以不用必须形成在fwd区域1b处。当主区域rm包括igbt区域1a和fwd区域1b时,主区域rm可以是电流主要流过的区域。

114.(其它实施例)

115.尽管已经根据实施例描述了本公开,但是应当理解,本公开不限于这样的实施例或结构。本公开包括在等同物范围内的各种修改和变化。此外,各种组合和模式,以及包括仅一个或更多或更少要件的其它组合和模式,都落入本公开的精神和范围内。

116.例如,在上述实施例的每一个中,第一导电类型为n型,第二导电类型为p型。或者,第一导电类型可以是p型,第二导电类型可以是n型。

117.在上述实施例的每一个中,半导体器件包括分别具有沟槽栅极结构的主元件me和感测元件se。但是,半导体器件可以包括分别具有平面栅极结构的主元件me和感测元件se。

118.在上述实施例的每一个中,发射极区16和接触区17的布置可以适当地修改。例如,发射极区16和接触区17可以沿着沟槽13的长度方向交替地排列。

119.此外,上述实施例中的每一个可以适当地组合以形成半导体器件。例如,通过将第二实施例与第三实施例或第四实施例组合,感测元件se可以包括分别具有不同性能的第一感测元件se1和第二感测元件se2。通过将第三实施例与第四实施例组合,感测元件se的背面层21可以形成有低杂质浓度层21c。每个实施例的组合可以进一步组合。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。