1.至少一个实施例涉及用于执行和促进高速通信的处理资源。例如,至少一个实施例涉及用于同步接地参考信令(grs)互连中的本地发送器和远程接收器对的数据链路层的技术。

背景技术:

2.通信系统经由通信信道或介质(例如,电缆、印刷电路板、链路、无线等)将信号从发送器发送到接收器。从发送器到接收器的通信导致接收器需要与发送器同步,否则数据可能会被破坏。例如,在进行芯片到芯片(c2c)通信时,本地发送器可能需要与远程接收器同步。一些通信系统可尝试通过扫描针对特殊符号或字段通信的比特流或使用滞后滤波器来在发送器和接收器之间进行同步。例如,系统可尝试通过从发送器发送包括比特/字节/字符填充的分组来同步发送器和接收器,并使接收器扫描位流中的关键字或额外的比特/字节/字符以划分分组的边界。这样的常规方法可能不可靠或导致接收器错误地确定发送器和接收器之间的同步。

附图说明

3.将参照附图描述根据本公开的各个实施例,其中:

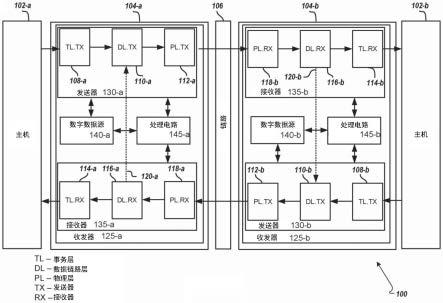

4.图1是根据至少一些实施例的采用同步接收器和发送器的方法的示例通信系统;

5.图2图示了根据至少一些实施例的在通信系统中传送的帧的示例;

6.图3是根据至少一些实施例的同步接收器和发送器的方法的示意图;

7.图4是根据至少一些实施例的用于同步高速信令互连的流程图;

8.图5图示了根据至少一些实施例的包括无线收发器的示例计算机系统,该无线收发器包括芯片到芯片互连。

具体实施方式

9.如上所述,扫描比特流以寻找特殊滤波器或利用滞后滤波器来同步本地发送器和远程接收器可能是不可靠的。没有适当的同步的情况下,接收器可能无法对接收到的数据执行错误解码操作。例如,通信系统可以包括第一设备(例如,第一芯片)和第二设备(例如,第二芯片),并且经由接地参考信令(grs)链路来传送(communicate)数据——例如,通信系统可以是芯片到芯片(c2c)互连。数据可以通过链路以固定长度的帧从第一设备的发送器传送到第二设备的接收器。例如,每个帧可以包括相同数量的比特,并发送数据的各部分。在一些示例中,grs c2c互连的物理层(pl)可以在链路被释放到数据链路层(dl)之前训练(例如,同步)。在这样的示例中,从pl到dl的转换可以在任何时间发生。此外,在基于grs链路架构从pl到dl的转换期间,链路可以恒定地被驱动到第一逻辑状态(例如,逻辑“0”)或第二逻辑状态(例如,逻辑“1”)。因此,在没有适当同步的情况下,接收器可以处理在从pl到dl的转换期间发送的数据,或基于错误地确定数据帧的开始或结束在数据帧的任意点处处理

数据——例如,处理第一数据帧和第二数据帧的一部分。这可能会导致接收器无法对接收到的数据执行数据检测,并导致系统具有高的误码率(ber)。

10.有利的是,本公开的各个方面涉及一种方法,用于在从发送器向接收器发送数据之前,确定由发送器在远程接收器处划定的帧边界(例如,给定帧的开始或结束)。根据实施例,发送器可以向接收器发送请求帧以开始同步过程。接收器可使用在发送器发送的每个帧中编码的错误代码对与请求帧的帧大小相对应的一组接收比特执行错误解码操作—例如,接收器可对接收到的每个帧执行循环冗余检查(crc)。如果请求帧通过了crc检查,接收器可以确定帧边界。在这样的示例中,接收器可以发送确定帧边界的确认,而发送器可以基于该确认开始发送数据。

11.如果请求帧未能通过crc检查,则接收器可以制止(refrain)(例如,跳过)对第一组比特之后接收到的第二组比特(例如,具有小于帧大小的大小的一定数量的比特或在一个时钟周期期间接收到的一定数量的比特)执行crc,并且对第二组比特之后接收到的第三组比特执行crc,其中第三组比特对应于帧大小。也就是说,接收器可以在确定对应于帧大小的第一组比特未能通过crc后,跳过对预定大小的比特(例如,对flit(微片)或在一个时钟周期期间接收到的一定数量的比特)执行crc,并恢复对接收到的对应于帧大小的后续第三组比特的错误解码操作。该接收器可以继续这个过程(例如,跳过与一个时钟周期内接收到的一定数量的比特的大小相对应的该数量的比特,并对与帧大小相对应的后续比特执行错误解码操作),直到所接收到的与帧大小相对应的一组比特通过crc。因此,当发送器不断发送请求帧,直到接收器确定帧边界时,接收器就可以保证帧锁定。此外,在大多数示例中,接收器将在对应于比特子集大小的“n”量内确定帧边界。本技术的实施例允许采用更可靠的方法在发送器和接收器之间进行同步,并降低系统的误码率。

12.图1图示了根据至少一个示例实施例的示例通信系统100。系统100包括主机102-a、主机102-b、第一设备104-a和第二设备104-b。系统100还包括耦合第一设备104-a和第二设备104-b的链路106。每个设备104可以包括收发器125,该收发器125包括发送器130、接收器135、数字数据源140和处理电路145。每个发送器130可以包括事务层(tl)108、数据层(dl)110、物理层(pl)112,并且每个接收器135可以包括tl 114、dl 116和pl 118。

13.在至少一个示例中,主机102或设备104可以对应于个人计算机(pc)、膝上型电脑、平板电脑、智能手机、服务器、服务器集合等中的一个或更多个。在一些示例中,主机102可以对应于与其他设备通信并且还连接到公共链路106的任何适当类型的设备。在一些示例中,主机102可以向设备104发送命令或数据。在这样的示例中,设备104可以基于主机102接收的命令或数据相互传送数据。作为另一个具体但非限制性的示例,主机102和设备104可以对应于向用户设备、客户端设备或系统100中的其他主机提供信息资源、服务和/或应用程序的服务器。

14.在至少一个示例实施例中,第一设备104-a和第二设备104-b可以是芯片的示例——例如,系统100可以是多芯片模块或芯片到芯片(c2c)互连的示例。在这样的示例中,设备104可以是单个芯片或芯片堆叠。在一些示例中,设备104可以包括图形处理单元(gpu)、交换机(例如,高速网络交换机)、网络适配器、中央处理单元(cpu)等,用于执行从主机102接收到的命令或功能。每个设备104可以包括收发器125,用于发送和接收信号,例如数据信号。数据信号可以是用数据调制的数字信号或光信号或用于承载数据的其他合适的

信号。每个收发器125可以包括接收器135和发送器130。发送器130包括用于从数字数据源140接收数字数据并根据数字数据输出数据信号以通过链路106发送到设备104-b的接收器135的合适的软件和/或硬件。设备110和设备112的接收器104可以包括用于接收信号(例如来自链路106的数据信号)的合适的硬件和/或软件。

15.在一个实施例中,设备104可以双向通信——例如,从主机102-a到主机102-b或从主机102-b到主机102-a。在一些示例中,设备104的每个接收器135或发送器130可以独立地和/或同时地操作。例如,第一设备104-a的接收器135-a可以与第一设备104-a的发送器130-a向第二设备104-b的接收器135-b发送数据同时地从第二设备104-b的发送器130-b接收数据。

16.设备104中的每个发送器130和接收器135可以包括事务层(tl)。在一些示例中,发送器130的tl 108可以被配置为请求事务——例如,请求数据的发送。例如,发送器130的tl 108可以为设备104的其他组件传送功能或组装分组。在一些示例中,发送器130的tl 108可以生成可以被发送到dl 110以进一步处理的事务层包(tlp)。在一些示例中,设备104中的每个接收器135还可以包括事务层114。在一些示例中,接收器135的tl 114可以被配置为完成事务——例如,完成数据的发送。例如,接收器135的tl 114可以从每个设备104的接收器的其他组件接收功能或者分解从每个设备104的接收器的其他组件接收到的分组。在一些实施例中,接收器135的tl 114可以验证传入的tlp分组以确保该接收到的分组是有效的——例如,没有错误。

17.设备104中的每个发送器130和接收器135还可以包括数据层。在一些示例中,dl 110和dl 116可以被配置为确保通过链路106发送的数据是正确的并且没有错误。例如,发送器130的dl 110可以用错误代码(例如,crc值)对发送的相应帧或分组进行编码。接收器125的dl 116可以基于接收到的帧生成错误代码并且解码嵌入在帧中的crc以用于比较生成的错误代码是否与发送的crc相匹配。在一些示例中,dl 116执行错误解码操作以查看接收到的数据是否正确且没有错误。在一些示例中,发送器130的dl 110可以被配置为将序列号作为报头添加到所发送的每个帧或分组,并且接收器135的dl 116也可以被配置为检查序列号。在一些示例中,发送器130的dl 110和接收器135的dl 116可以包括控制器或控制流单元或与其耦合,以对接收到的分组或帧执行错误解码操作——例如处理电路145。

18.另外,设备104中的每个发送器130和接收器135可以包括物理层(pl)。在一些示例中,pl 112和pl 118可以被配置为通过链路106发送和接收数据。例如,pl 112和pl 118可以包括输入/输出(i/o)缓冲器、并行到串行和串行到并行转换器、阻抗匹配电路、逻辑电路等,用于通过链路106发送和接收数据分组或帧。

19.每个收发器125可以包括数字数据源140和控制收发器125的处理电路145。数字数据生成器140可以包括用于以数字格式(例如,以二进制代码和/或温度计代码)输出数据的合适的硬件和/或软件。数字数据源140输出的数字数据可以从存储器(未示出)中检索或根据输入(例如,用户输入)生成。

20.处理电路145可以包括软件、硬件或其组合。例如,处理电路145可以包括存储器和处理器(例如,微处理器),存储器包括可执行指令,处理器执行存储器上的指令。存储器可以对应于任何合适类型的存储器设备或被配置为存储指令的存储器设备的集合。可以使用的合适的存储器设备的非限制性示例包括闪存、随机存取存储器(ram)、只读存储器(rom)、

它们的变体、它们的组合等。在一些实施例中,存储器和处理器可以集成到共同的设备中(例如,微处理器可以包括集成存储器)。附加地或替代地,处理电路145可以包括硬件,例如专用集成电路(asic)。处理电路132的其他非限制性示例包括集成电路(ic)芯片、中央处理单元(cpu)、通用处理单元(gpu)、微处理器、现场可编程门阵列(fpga)、逻辑门或晶体管的集合、电阻器、电容器、电感器、二极管等。一些或所有的处理电路145可以在印刷电路板(pcb)或pcb的集合上提供。应当理解,任何适当类型的电气组件或电气组件的集合都可以适合包括在处理电路145中。处理电路145可以向和/或从收发器125的其他元件发送和/或接收信号,以控制收发器125的整体操作。

21.收发器125或收发器125的所选元件可以采用设备104的可插拔卡或控制器的形式。例如,收发器125或收发器125的所选元件可以在网络接口卡(nic)上实现。

22.链路106可以是可用于连接设备104的通信网络的示例,例如互联网协议(ip)网络、以太网、infiniband(ib)网络、光纤通道网络、互联网、蜂窝通信网络、无线通信网络、它们的组合(例如,以太网光纤通道)、它们的变体和/或类似物。在一个具体但非限制性示例中,链路106是使得能够使用数据信号(例如,数字、光学、无线信号)在设备104之间进行数据传输的网络。

23.在一个实施例中,链路106可以被配置为在第一设备104-a和第二设备104-b之间传送请求、数据、功能、命令等。在一个示例中,链路106可以是电缆、印刷电路板、链路、无线等。在至少一个实施例中,链路106可以是接地参考信令(grs)互连的示例。在这样的示例中,链路106可以包括以rc为主的信道和lc传输线。此外,grs互连可以是片上链路、跨基板(例如有机封装)的链路或印刷电路板(pcb)上的链路信令。在一些示例中,grs可以使用接地网络作为信号参考电压——例如,接地可以是返回信令。尽管未明确示出,但应当理解,主机102和设备104可以包括通常与诸如发送和接收数据之类的计算任务相关联的其他处理设备、存储设备和/或通信接口。

24.在一些示例中,基于grs架构,链路106可以被配置为由设备104的任一发送器驱动到逻辑状态“1”或逻辑状态“0”。在这样的示例中,确定pl层到dl层之间的转换可能很困难——例如,链路106可以任意地从发送pl层信息转换到dl层信息。此外,基于发送高速数据的链路106,在发送数据时可能存在高ber和链路106错误的可能性。因此,至少一个实施例描述了一种在发送数据之前同步第一设备104-a的发送器130-a的dl与第二设备104-b的接收器135-b的dl的方法。如上文所述,链路106支持双向通信。在这样的实施例中,同步dl的方法也可以由第二设备104-b的发送器130-b和第一设备104-a的接收器135-a独立地和/或同时地使用。

25.在一些实施例中,系统100可以在同步第一设备104-a和第二设备104-b的dl之前同步第一设备104-a和第二设备104-b的pl。如图2所示,在同步pl之后但在发送数据之前,第一设备104-a的发送器130-a可以发送请求帧。在一些实施例中,请求帧可以在接收器135重置之后、接收器135重新启动之后、或者由用户确定的任何其他任意重新启动或接收器135使用的其他代码之后被发送。在一些示例中,请求帧可以另外称为包括请求的帧或简称为对同步的请求。

26.如图2所示,由发送器发送的帧200可以包括“n”个flit 202。例如,给定的帧200可以包括十(10)个flit 202。在一些示例中,每个flit 202可以包括相同数量的比特——例

如,每个flit 202是“x”位宽。例如,每个flit 202可以是128位宽。在一些示例中,发送器130的dl 110可以每个时钟周期发送一(1)个flit。因此,每个帧可以基于flit 202的数目“n”在“n”个时钟周期中发送。另外,每个帧200可以包括错误代码crc 208。dl 110被配置为生成用于整个帧的crc 208。在这样的实施例中,接收器135的dl 116被配置为针对每个帧200跨“n”个flit 202执行错误解码操作——例如,接收器135被配置为在接收到对应于帧200的大小或宽度的“n”个flit 202之后执行一个错误解码操作。其中,错误解码操作以帧粒度执行。每个帧200还可以包括报头204。

27.在一些示例中,帧200可以是由发送器130-a发送到接收器135-b的用于发起第一设备104-a和第二设备104-b之间的dl的同步的请求帧。例如,发送器130-a可以将请求帧200从dl 110-a发送到链路106以启动同步。由发送器130-a发送的每个请求帧200可以包括报头204,该报头204包括指示帧200是请求帧的序列、信息、标识符等——例如,同步dl 110-a与第二设备104-b中的接收器135-b的dl 116-b的请求。在一些实施例中,请求帧200还可以包括数据——例如,训练数据或以其他方式在同步过程中使用的数据。每个请求帧200还包括crc 208。第二设备104-b的接收器135-b可以利用crc 208来确定接收到的数量为“n”个flit 202是否与给定请求帧200匹配或对齐——例如,如果“n”个flit 202通过或未通过crc错误解码操作。应该注意,请求帧200的每个crc是相同的——例如,由发送器130-a发送的每个请求帧200具有与另一个请求帧200共同的至少一些部分。例如,发送器130-a可以发送具有第一数据和第一错误代码的第一请求帧200和具有第二数据和第二错误代码的第二请求帧,其中第一错误代码和第二错误代码相同。关于请求帧200、错误解码操作和同步过程的附加细节参考图3和图4进行描述。

28.在一些实施例中,如果第二设备104-b确定接收到的“n”个flit 202与请求帧200对齐,则第二设备104-b可以将确认从dl 110-b发送到dl 116-a。即,控制流单元(控制有限状态机(fsm)、控制器等)可以确定dl 116-b与dl 110-a同步,并将消息120-b(经由处理电路145-b)发送到第二设备104-b的发送器130-b。dl 110-b发送的帧200可以包括确认。例如,确认可能不是唯一的帧200,而是嵌入的(或标识在)帧200——例如,报头204可以包括该确认的符号、序列或标识符。响应于该确认,第一设备104-a可以在发送主机102-a的数据之前向第二设备104-b发送同步完成帧200(例如,包括正在完成的同步的符号、序列或标识符的帧200)——例如,在发送数据帧200之前。

29.图3图示了同步本地发送器和远程接收器的方法的图300。例如,图300图示了在接收器处利用错误解码操作来确定由发送器使用的帧边界的方法。图300所示的方法可以由包括硬件、软件、固件或其任何组合的处理逻辑来执行。在至少一个实施例中,图300所示的方法由图1中的第二设备104-b中的接收器135-b的dl 116-b或第一设备104-a中的接收器135-a的dl 116-a执行。在一些实施例中,如参考图2所述,接收器135可以分别从第一设备104-a的发送器103-a或者第二设备104-b的发送器130-b的dl 110-a或dl 110-b接收数据、flit 202、比特、帧200等。尽管以特定的序列或顺序示出,除非另有说明,否则可以修改过程的顺序。因此,所示实施例应仅被理解为示例,并且所示过程可以以不同的顺序执行,并且一些过程可以并行执行。此外,在各个实施例中可以省略一个或更多个过程。因此,并非在每个实施例中都需要所有过程。说明同步方法的其他图是可能的。

30.如上文所述,为了发起第一设备104-a的发送器和第二设备104-b的接收器之间的

dl(例如,在dl 110-a和dl 116-b之间)的同步,发送器可以发送请求帧。例如,dl 110-a可以首先发送请求帧“m”302-a和随后的请求帧“m 1”302-b、“m 2”302-c、“m 3”302-d、和“m 4”302-e。基于链路106延迟、错误和任意转换,dl 116-b可以开始接收与帧“m”302-a异步的flit(例如,一定数量的比特)。即,dl 116-b可以接收与请求帧大小或宽度相对应的“n”个flit 304,但其包括发送的帧“m”302-a和帧“m 1”302-b的各部分。在这样的实施例中,dl 116-b可以确定对“n”个flit 304的错误解码操作失败。也就是说,dl 116-b可以通过为接收到的对应于帧大小的前“n”个flit 304生成错误代码并确定嵌入在flit 304内的crc与所生成的错误代码不匹配来执行错误解码操作。因此,dl 116可以基于错误解码操作的失败来确定flit 304不对应于帧边界。在这样的实施例中,dl 116-b可以跳过或以其他方式制止对接收到的下一个flit 306执行任何错误解码操作——例如,dl 116-b可以忽略flit 306并且并不作为接收下一“n”个flit的一部分或成为dl 116-b解码的任何帧的一部分而包括flit 306。在一些示例中,flit 306也可以被称为具有小于帧大小的大小的一组比特、具有预定大小的一组比特、或比特的子集。或者,跳过flit 306可被称为跳过在接收到“n”个片304之后的时钟周期期间接收的数据或一定数量的比特。

31.在跳过flit 306之后,dl 116-b可以对随后接收的“n”个flit 308执行错误解码操作。在图300所示的示例中,flit 308也与发送的帧302异步。即,flit 308包括帧“m 1”302-b和“m 2”302-c的部分。因此,当dl 116-b对flit 308执行解码操作时,dl 116-b可以确定为flit 308生成的错误代码与嵌入在flit 308中的crc不匹配。因此,dl 116-b可以基于错误解码操作确定flit 308不对应于帧边界。因此,dl 116-b可以跳过或以其他方式制止对flit 310执行错误解码操作——例如,将flit 310从接收的下一数量为“n”个flit中排除,或制止考虑flit 310生成错误代码。

32.在跳过flit 310之后,dl 116-b可以对随后接收的“n”个flit 312执行错误解码操作。在图300所示的示例中,flit 312与发送的帧302同步。也就是说,flit 312与发送的帧“m 3”302-d同步(例如,对齐)。因此,当dl 116-b对flit 312执行解码操作时,dl 116-b可以确定嵌入在flit 312中的crc对应于为“n”个flit 312生成的错误代码。因此,dl 116-b可以基于错误解码操作确定接收到的“n”个flit 312对应于帧边界。在图300所示的示例中,dl 116-b可以接收额外的一组flit 314并且对flit 314执行错误解码操作以确保帧边界是正确的。即,当确定帧边界时,dl 116-b可以制止跳过任何flit。

33.在确定帧边界之后,dl 116-b可以生成确认并向第二设备104-b的发送器的dl 110-b发送消息116-b。因此,dl 110-b可以发送如参考图2所描述的带有确认的帧200。随后,在一些实施例中,dl 116-a可以向dl 110-a发送指示从第二设备104-a接收到的确认的消息,并且第一设备104-a可以基于第一设备104-a和第二设备104-b的dl 110-a和dl 116-b之间的同步,在数据之后发送同步完成帧——例如,第一设备104-a和第二设备104-b可以执行握手并基于握手发送数据。

34.注意,图300图示了一个示例并且其他示例是可能的。在一些实施例中,dl 116-b可以基于何时接收到flit 304来执行比图300中所指示的更多或更少的错误解码操作。例如,可以与帧“m”302-a同步地接收flit 304,并且dl 116-b可以在一(1)个错误解码操作之后确定帧边界。在其他示例中,可以接收从帧“m”302-a偏移一(1)个flit的flit 304。在这样的示例中,dl 116-b可以执行“n”个错误解码操作——例如,基于帧中的“n”个flit。也就

是说,在大多数示例中,dl 116-b可以确定接收到的1到“n”个帧内的帧边界,其中“n”是每个帧中的flit的数量。在一些实施例中,基于随机链路错误,dl 116-b可以在接收到“n”个帧之后确定帧边界——例如,在两(2)倍“n”个帧内。此外,由于发送的每个帧都包括嵌入的crc,因此dl 116-a接受损坏或错误缠身的数据的可能性降低——例如,每个帧都受crc保护。

35.如上所述,系统100是双向的。因此,dl 116-b可以和dl 116-a与dl 110-b的同步独立和/或同时地与dl 110-a同步。dl 116-a的同步可以通过本文参考图3描述的方法来完成。

36.图4图示了用于同步高速信令互连的方法400的流程图——例如,同步本地发送器和远程接收器。例如,方法400图示了在接收器处利用错误解码操作来确定由发送器使用的帧边界。方法400可以由包括硬件、软件、固件或其任意组合的处理逻辑来执行。在至少一个实施例中,方法400由图1的第二设备104-b中的接收器的dl 116-b或第一设备104-a中的接收器的dl 116-a执行。在一些实施例中,接收器可以分别从如参考图2所描述的第一设备104-a或第二设备104-b的发送器的dl 110-a或dl 110-b接收数据、flit 202、比特、帧200等。尽管以特定的序列或顺序显示,除非另有说明,否则可以修改过程的顺序。因此,所示实施例应仅被理解为示例,并且所示过程可以以不同的顺序执行,并且一些过程可以并行执行。此外,在各个实施例中可以省略一个或更多个过程。因此,并非在每个实施例中都需要所有过程。图示同步方法的其他图是可能的。

37.在操作405,第一设备(例如,图1的第一设备104-a)中的发送器(例如,dl 110-a)将用于数据层的同步的一个或更多个请求帧发送到第二设备(例如,第二设备104-b)的接收器(例如,dl 116-b)。在一个实施例中,请求帧经由耦合第一设备和第二设备的链路(例如,链路106)发送。在一些示例中,链路是grs互连。在一个实施例中,请求帧包括一定数量的比特(例如,flit)和错误代码。在一个实施例中,发送器发送具有第一数据和第一错误代码的第一请求帧以及具有第二数据和第二错误代码的第二请求帧,第一错误代码与第二错误代码相同。

38.在操作410,第二设备的接收器接收第一组比特。在一个实施例中,第一组比特对应于每个请求帧中的一定数量的比特。即,接收器接收具有等于每个请求帧的宽度或大小的一定数量的比特。

39.在操作415,接收器使用第一组比特的一部分对第一组比特执行错误解码操作。在一个实施例中,第一组比特的该部分是接收器发送的每个请求帧中包括的错误代码。在一个实施例中,接收器对第一组比特执行crc操作,因为每个请求帧包括在错误解码操作期间检查的crc值。在一个实施例中,接收器基于接收到的第一组比特生成错误代码。在这样的实施例中,接收器将生成的错误代码与第一组比特中的嵌入的crc代码进行比较。

40.在操作420,接收器确定第一组比特是否对应于帧边界。在一个实施例中,接收器基于在操作415处的错误解码操作的失败——例如,基于生成的错误代码与第一组比特中的嵌入crc代码不匹配,来确定第一组比特不对应于帧边界。在这样的实施例中,接收器进行到操作425。在一个实施例中,接收器基于在操作415处的错误解码操作的成功来确定第一组比特确实对应于帧边界。在这样的实施例中,接收器进行到操作445。

41.在操作425处,接收器制止对在第一组比特之后接收的第二组比特(例如,flit、数

量小于帧大小的一组比特或在接收器的一个时钟周期期间接收的一定数量的比特)执行错误解码操作。在一个实施例中,接收器忽略第二组比特并且不将第二组比特视为用于错误解码操作的任何帧的一部分。也就是说,接收器对接收到的对应于帧大小的一定数量的比特执行错误解码操作,但不将第二组比特视为将经受错误解码操作的该数量的比特的一部分——例如,接收器不会基于第二组比特生成错误代码。

42.在操作430,接收器可以从发送器接收第三组比特并且对第三组比特执行错误解码操作。在一个实施例中,在第二组比特之后接收第三组比特。在一个实施例中,第三组比特具有对应于帧大小/宽度的一定数量的比特。在一些示例中,为了执行错误解码操作,接收器可以为接收到的第三组比特生成错误代码,并将生成的错误代码与嵌入在第三组比特中的crc代码进行比较。

43.在435,接收器可以确定第三组比特是否对应于帧边界。在一个实施例中,接收器基于在操作430处的错误解码操作的失败——例如,基于生成的用于第三组比特的错误代码与第三组比特中嵌入的crc代码不匹配,来确定第三组比特不对应于帧边界。在这样的实施例中,接收器进行到操作440。在实施例中,接收器基于在操作430处的错误解码操作的成功——例如,基于生成的用于第三组比特的错误代码与第三组比特中嵌入的crc代码相匹配,来确定第三组比特确实对应于帧边界。在这样的实施例中,接收器进行到操作445。

44.在操作440,接收器可以重复操作425-435,直到找到帧边界。在一个实施例中,接收器可以在每次错误解码操作不成功时跳过接收到的具有等于第二组比特的大小/宽度的一定数量的比特(例如,跳过在时钟周期期间接收到的一定数量的比特)。如参考图3所描述的,通过跳过在时钟周期中接收到的比特,接收器最终将基于第一数量比特的大小确定帧边界——例如,在数量为“n”的帧内。在这样的实施例中,接收器可以继续在执行错误解码操作和跳过在失败的错误解码操作之后的时钟周期中接收到的比特之间交替,直到确定帧边界——例如,直到针对对应于帧大小的一定数量的比特生成的错误代码与嵌入在相应请求帧中的crc代码相匹配。因此,接收器可以在确定帧边界之后进行到操作445。

45.在操作445,第二设备向第一设备发送对同步的确认(例如,对确定帧边界的确认)。在一个实施例中,第二设备的发送器(例如,dl 110-b)将确认发送到第一设备的接收器(例如,dl 116-a)。在一个实施例中,第二设备生成确认并将其从第二设备的接收器传送到发送器。

46.在操作450,第一设备基于接收到确认来制止发送额外的请求帧。在一个实施例中,第一设备将确认从第一设备的接收器传送到发送器。

47.在操作455,第一设备和第二设备之间的握手完成。在一个实施例中,第一设备的发送器基于接收到确认将同步完成帧发送到第二设备的接收器。在一个实施例中,第一设备在完成握手之后向第二设备发送数据。在一个实施例中,遵循本文描述的方法的同步独立地/同时地在第二设备的发送器和第一设备的接收器之间进行。

48.图5图示了根据至少一个实施例的计算机系统500。在至少一个实施例中,计算机系统500可以是具有互连设备和组件、soc或某种组合的系统。在至少一个实施例中,计算机系统500由处理器502形成,处理器502可以包括用于执行指令的执行单元。在至少一个实施例中,计算机系统500可以包括但不限于诸如处理器502之类的组件,用于采用包括逻辑的执行单元来执行用于处理数据的算法。在至少一个实施例中,计算机系统500可以包括处理

器,例如处理器家族、xeontm、xscaletm和/或strongarmtm、core

tm

或nervana

tm

微处理器,这些微处理器可从加州圣克拉拉市的英特尔公司获得,但是也可以使用其他系统(包括具有其他微处理器的pc、工程工作站、机顶盒等的)。在至少一个实施例中,计算机系统500可以执行可从华盛顿州雷德蒙德的microsoft公司获得的windows操作系统版本,但是也可以使用其他操作系统(例如unix和linux)、嵌入式软件和/或图形用户界面。

49.在至少一个实施例中,计算机系统500可以用在其他设备中,例如手持设备和嵌入式应用程序。手持设备的一些示例包括手机、互联网协议设备、数码相机、个人数字助理(“pda”)和手持pc。在至少一个实施例中,嵌入式应用程序可以包括微控制器、数字信号处理器(dsp)、soc、网络计算机(“netpc”)、机顶盒、网络集线器、广域网(“wan”)交换机、或可以执行一个或更多个指令的任何其他系统。在一个实施例中,计算机系统500可以用在诸如图形处理单元(gpu)、网络适配器、中央处理单元和网络设备(诸如交换机(例如,高速直接gpu到gpu互连,诸如nvidia gh100 nvlink或nvidia quantum2 64端口infiniband ndr交换机))之类的设备中。

50.在至少一个实施例中,计算机系统500可以包括但不限于处理器502,处理器502可以包括但不限于一个或更多个执行单元507,其可以被配置为执行计算统一设备架构(“cuda”)(是由加州圣克拉拉市的nvidia公司开发的)程序。在至少一个实施例中,cuda程序是用cuda编程语言编写的软件应用程序的至少一部分。在至少一个实施例中,计算机系统500是单处理器桌面或服务器系统。在至少一个实施例中,计算机系统500可以是多处理器系统。在至少一个实施例中,处理器502可以包括但不限于cisc微处理器、risc微处理器、vliw微处理器、实现指令集组合的处理器或任何其他处理器设备,例如数字信号处理器。在至少一个实施例中,处理器502可以耦合到处理器总线510,处理器总线510可以在处理器502和计算机系统500中的其他组件之间传输数据信号。

51.在至少一个实施例中,处理器502可以包括但不限于一级(“l1”)内部高速缓存存储器(“高速缓存”)504。在至少一个实施例中,处理器502可以具有单个内部高速缓存或多级内部高速缓存。在至少一个实施例中,高速缓存存储器可以位于处理器502的外部。在至少一个实施例中,处理器502还可以包括内部和外部高速缓存的组合。在至少一个实施例中,寄存器文件506可以将不同类型的数据存储在各种寄存器中,包括但不限于整数寄存器、浮点寄存器、状态寄存器和指令指针寄存器。

52.在至少一个实施例中,包括但不限于执行整数和浮点运算的逻辑的执行单元507也驻留在处理器502中。处理器502还可以包括微码(“ucode”)只读存储器(“rom”),其存储用于某些宏指令的微码。在至少一个实施例中,执行单元502可以包括用于处理打包指令集509的逻辑。在至少一个实施例中,通过在通用处理器502的指令集中包括打包指令集509连同用于执行指令的关联电路,许多多媒体应用程序使用的操作可以使用通用处理器502中的打包数据来执行。在至少一个实施例中,可以通过使用处理器的数据总线的全宽来更有效地加速和执行许多多媒体应用程序,以用于对打包数据执行操作,这可以消除通过处理器的数据总线传输更小的数据单元以一次对一个数据元素执行一个或更多个操作的需要。

53.在至少一个实施例中,执行单元也可以用在微控制器、嵌入式处理器、图形设备、

dsp和其他类型的逻辑电路中。在至少一个实施例中,计算机系统500可以包括但不限于存储器520。在至少一个实施例中,存储器520可以实现为dram设备、sram设备、闪存设备或其他存储器设备。存储器520可以存储指令519和/或由可以由处理器502执行的数据信号表示的数据521。

54.在至少一个实施例中,系统逻辑芯片可以耦合到处理器总线510和存储器520。在至少一个实施例中,系统逻辑芯片可以包括但不限于存储器控制器集线器(“mch”)516,并且处理器502可以经由处理器总线510与mch 516通信。在至少一个实施例中,mch 516可以提供到存储器520的高带宽存储器路径518,用于指令和数据存储以及图形命令、数据和纹理的存储。在至少一个实施例中,mch 516可以在处理器502、存储器520和计算机系统500中的其他组件之间引导数据信号,并在处理器总线510、存储器520和系统i/o 522之间桥接数据信号。在至少一个实施例中,系统逻辑芯片可以提供用于耦合到图形控制器的图形端口。在至少一个实施例中,mch 516可以通过高带宽存储器路径518耦合到存储器520,并且图形/视频卡512可以通过加速图形端口(“agp”)互连514耦合到mch 516。

55.在至少一个实施例中,计算机系统500可以使用作为专有集线器接口总线的系统i/o 522将mch 516耦合到i/o控制器集线器(“ich”)530。在至少一个实施例中,ich 530可以经由本地i/o总线提供到一些i/o设备的直接连接。在至少一个实施例中,本地i/o总线可以包括但不限于用于将外围设备连接到存储器520、芯片组和处理器502的高速i/o总线。示例可以包括但不限于音频控制器529、固件集线器(“flash bios”)528、无线收发器526、数据存储器524、包含用户输入接口525和键盘接口的传统i/o控制器523、串行扩展端口527(例如usb)和网络控制器534。数据存储器524可以包括硬盘驱动器、软盘驱动器、cd-rom设备、闪存设备或其他大容量存储设备。在一个实施例中,无线收发器526包括受限ffe 508。

56.在至少一个实施例中,图5图示了一个系统,该系统包括互连的硬件设备或“芯片”(例如,参考图1描述的第一设备104-a和第二设备104-b)。在至少一个实施例中,图5可以图示示例性soc。在至少一个实施例中,图5中所示的设备可以使用专有互连、标准化互连(例如,pcie)或它们的某种组合互连,并利用参照图1所述的grs链路106。在至少一个实施例中,系统500的一个或更多个组件使用计算快速链路(“cxl”)互连来互连。

57.其他变型在本公开的精神内。因此,尽管所公开的技术易于进行各种修改和替代构造,但是某些图示的实施例在附图中示出并且已在上面进行了详细描述。然而,应理解,无意将本公开内容限制为所公开的一种或更多种具体形式,而是相反,其意图是涵盖落入如所附权利要求书所定义的本公开内容的精神和范围内的所有修改、替代结构和等同物。

58.除非另有说明,否则在描述公开的实施例的上下文中(尤其是在以下权利要求的上下文中)使用术语“一”和“一个”和“该”以及类似的指称将被解释为涵盖单数和复数此处或明显与上下文相矛盾,而不是作为术语的定义。除非另有说明,否则术语“包括”、“具有”、“含有”和“包含”将被解释为开放式术语(意思是“包括但不限于”)。“连接的”,当未经修改并指物理连接时,应被解释为部分或全部包含在、附接到或连接在一起,即使有某些介入。除非本文另有指出,否则本文中数值范围的列举仅旨在用作单独引用落入该范围内的每个单独值的速记方法,并且每个单独的值都被并入说明书中,就好像它在本文中单独列举一样。在至少一个实施例中,除非另有说明或与上下文相矛盾,否则术语“集”(例如,“项目集”)或“子集”的使用将被解释为包括一个或更多个成员的非空集合。此外,除非另有说明

或与上下文相矛盾,术语对应集的“子集”不一定表示对应集的真子集,而是子集和对应集可以相等。

59.除非另有明确说明或与上下文明显矛盾,否则诸如“a、b和c中的至少一个”或“a、b和c中的至少一个”形式的短语的连词是以其他方式理解为一般用于表示项目、术语等的上下文可以是a或b或c,或a和b和c的集合的任何非空子集。例如,在说明性示例中在具有三个成员的集合中,连词短语“a、b和c中的至少一个”和“a、b和c中的至少一个”指以下任何一个集合:{a}、{b}、{c},{a,b},{a,c},{b,c},{a,b,c}。因此,这种连词语言一般不旨在暗示某些实施例需要a中的至少一个、b中的至少一个和c中的至少一个各自存在。此外,除非另有说明或与上下文相矛盾,否则术语“复数”表示复数的状态(例如,“多个项目”表示多个项目)。在至少一个实施例中,多个项目的数量至少为两个,但是当明确地或通过上下文这样指示时可以更多。此外,除非另有说明或从上下文中明确,否则“基于”一词是指“至少部分基于”而不是“仅基于”。

60.除非本文另有说明或与上下文明显矛盾,否则本文描述的过程的操作可以以任何合适的顺序执行。在至少一个实施例中,诸如本文描述的那些过程(或其变体和/或组合)的过程在配置有可执行指令的一个或更多个计算机系统的控制下执行并且被实现为代码(例如,可执行指令、一个或更多个计算机程序或一个或更多个应用程序)通过硬件或其组合在一个或更多个处理器上共同执行。在至少一个实施例中,代码被存储在计算机可读存储介质上,例如,以包括可由一个或更多个处理器执行的多个指令的计算机程序的形式。在至少一个实施例中,计算机可读存储介质是不包括瞬态信号(例如,传播瞬态电或电磁传输)但包括非瞬态数据存储电路(例如,缓冲器、高速缓存和队列)在瞬态信号的收发器内。在至少一个实施例中,代码(例如,可执行代码或源代码)存储在其上存储有可执行指令(或存储可执行指令的其他存储器)的一组一个或更多个非暂时性计算机可读存储介质上,当由计算机系统的一个或更多个处理器执行(即,作为被执行的结果)使计算机系统执行本文所述的操作。在至少一个实施例中,一组非暂态计算机可读存储介质包括多个非暂态计算机可读存储介质,并且多个非暂态计算机可读存储介质中的一个或更多个单独的非暂态存储介质缺少所有代码,而多个非暂时性计算机可读存储介质共同存储所有代码。在至少一个实施例中,可执行指令被执行以使得不同的指令由不同的处理器执行。

61.因此,在至少一个实施例中,计算机系统被配置为实现一个或更多个服务,这些服务单独或共同执行本文描述的过程的操作,并且这种计算机系统配置有能够执行操作的适用硬件和/或软件。此外,实现本公开的至少一个实施例的计算机系统是单个设备,并且在另一个实施例中,是分布式计算机系统,包括多个不同地操作的设备,使得分布式计算机系统执行这里描述的操作并且使得单个设备不执行所有操作。

62.本文提供的任何和所有示例或示例性语言(例如,“诸如”)的使用仅旨在更好地阐明本公开的实施例,并且不对本公开的范围构成限制,除非另有声明。说明书中的任何语言都不应被解释为指示任何未要求保护的元素对于本公开的实践是必不可少的。

63.本文引用的所有参考文献,包括出版物、专利申请和专利,均以相同的程度通过引用并入本文,就好像每个参考文献单独且具体地指示通过引用并入并在本文中全文阐述一样。

64.在描述和权利要求中,可以使用术语“耦合”和“连接”以及它们的派生词。应当理

解,这些术语可能不旨在作为彼此的同义词。相反,在特定示例中,“连接”或“耦合”可用于指示两个或更多个元素彼此直接或间接物理或电接触。“耦合”也可能意味着两个或更多个元素彼此不直接接触,但仍相互合作或相互作用。

65.除非另有明确说明,否则可以理解,贯穿说明书的术语诸如“处理”、“计算”、“计算”、“确定”等是指计算机或计算系统的动作和/或过程或类似的电子计算设备,它们操纵和/或将计算系统的寄存器和/或存储器中表示为物理量(例如电子量)的数据转换为类似地表示为计算系统的存储器、寄存器或其他此类信息存储中的物理量的其他数据、传输或显示设备。

66.以类似的方式,术语“处理器”可以指处理来自寄存器和/或存储器的电子数据并将该电子数据转换成可以存储在寄存器和/或存储器中的其他电子数据的任何设备或设备的一部分。“计算平台”可以包括一个或多个处理器。如本文所用,“软件”进程可以包括例如随时间执行工作的软件和/或硬件实体,例如任务、线程和智能代理。此外,每个进程可以指多个进程,用于顺序或并行、连续或间歇地执行指令。在至少一个实施例中,术语“系统”和“方法”在本文中可互换使用,只要系统可以体现一种或多种方法并且方法可以被认为是系统。

67.在本文件中,可以参考获得、获取、接收或将模拟或数字数据输入到子系统、计算机系统或计算机实现的机器中。在至少一个实施例中,获得、获取、接收或输入模拟和数字数据的过程可以以多种方式完成,例如通过接收数据作为函数调用的参数或对应用程序编程接口的调用。在至少一个实施例中,获得、获取、接收或输入模拟或数字数据的过程可以通过经由串行或并行接口传输数据来完成。在至少一个实施例中,获得、获取、接收或输入模拟或数字数据的过程可以通过经由计算机网络从提供实体到获取实体传输数据来完成。在至少一个实施例中,还可以参考提供、输出、传输、发送或呈现模拟或数字数据。在各种示例中,提供、输出、传输、发送或呈现模拟或数字数据的过程可以通过将数据作为函数调用的输入或输出参数、应用程序编程接口或进程间通信机制的参数来实现.

68.尽管本文的描述阐述了所描述技术的示例实施例,但其他架构可以用于实现所描述的功能,并且旨在落入本公开的范围内。此外,尽管出于描述的目的可以在上面定义职责的具体分配,但是可以根据情况以不同的方式分配和划分各种功能和职责。

69.此外,尽管已经用特定于结构特征和/或方法动作的语言描述了主题,但应当理解,所附权利要求书中所要求保护的主题不必限于所描述的特定特征或行为。而是,公开了特定的特征和动作作为实现权利要求的示例性形式。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。