1.本发明属于半导体材料与器件结构领域,特别涉及氧化镓半导体叠层结构及制备方法。

背景技术:

2.自20世纪50年代,半导体材料被发现并应用于功率器件,一直到现在,历经70余年的发展,人们对半导体材料的研究从未停下,从第一代半导体的锗和硅,到第二代半导体的砷化镓和磷化铟,再到第三代的碳化硅和氮化镓,再到超宽禁带的氧化镓(ga2o3),半导体材料在不断的迭代更新,功率器件的功能也在不断的扩宽,包括:更高的击穿电压,更低的导通电阻,更大的电流,更强的耐温等级,更加的小型化;这其中,超宽禁带的氧化镓(ga2o3)作为一种新的半导体材料,禁带宽度在4.7~5.3ev之间,在击穿场强、巴利加优值和成本等方面优势突出。

3.氧化镓(ga2o3)具有α、β、γ、δ、ε五种相,在半导体领域,目前主要围绕α相和β相展开研究,其中β-ga2o3为单斜晶体结构,最为稳定,禁带宽度约为4.8ev;α-ga2o3为六方晶体结构,稳定性次之,禁带宽度约为5.3ev;另外,据可查资料,α-ga2o3具有比β-ga2o3更高的载流子迁移率。基于这些特性而言,α-ga2o3更适合应用于功率器件。

4.现今,受限于α-ga2o3衬底基板制备技术仍未能攻克,目前只能寻求异质衬底来进行外延α-ga2o3薄膜。已知α-ga2o3与蓝宝石基板具有相同的晶体结构,目前已知有在蓝宝石衬底上运用mist-cvd技术成功的制备出高品质的α-ga2o3单晶薄膜,并将其用于制备肖特基二极管的报道。

5.然而蓝宝石并非电子器件的理想衬底,一方面,其在价格、尺寸、导热性上均不如硅衬底;另一方面,利用蓝宝石衬底上制作α-ga2o3垂直器件,需要对蓝宝石衬底进行剥离,而剥离是一道难度大且成本高的工艺步骤。

6.硅基器件制备工艺成熟,且硅单晶(111)面具有六方对称性,与α相ga2o3具有相近的晶体结构。如果能够在硅衬底制备出高品质的α-ga2o3单晶薄膜,就可以将ga2o3半导体器件的制备兼容到现有的硅基半导体工艺中,有效降低ga2o3半导体器件的制备成本;并且,硅衬底导热性能优良,有意掺杂后的导电性能优良,有利于垂直结构器件的制备。

7.专利文献cn 110085658a,有关于在硅(111)衬底上沉积氮化物插入层,再异质外延氧化镓的介绍。

8.然而,在硅(111)衬底上外延氮化物(例如氮化镓),属于异质外延,硅和氮化物这两种不同的材料存在一定的晶格失配和热失配。如果直接在大面积的硅(111)衬底上外延氮化物薄膜(gan薄膜),由于二者之间晶格失配和热失配的存在,大面积的硅衬底上沉积的氮化物薄膜(gan薄膜)很容易出现裂纹,更进一步,会影响到氮化物薄膜(gan薄膜)上外延沉积的α-ga2o3薄膜质量,从而无法制备出高性能的半导体器件。

技术实现要素:

9.有鉴于此,本发明要解决的技术问题是提供一种氧化镓半导体叠层结构和制备方法,同时解决了硅衬底上直接生长gan薄膜层导致的晶格失配和热失配,以及硅衬底上直接生长α-ga2o3薄膜层导致的硅衬底层上表面被氧化影响薄膜质量;本发明还提供包含所述的氧化镓半导体叠层结构半导体装置。

10.作为本发明第一个方面,提供的一种氧化镓半导体叠层结构技术方案如下:

11.一种氧化镓半导体叠层结构,其特征在于,自下而上包括:硅衬底层、gan半导体层和ga2o3半导体层;所述的硅衬底层的上表面加工有隔离带,将所述的衬底层的上表面分割成多个互不相连的六边形生长平台,所述的gan半导体层是具有六方晶体结构的gan薄膜,所述的ga2o3半导体层是具有六方晶体结构的α-ga2o3薄膜。

12.优选地,所述的硅衬底层为硅(111)面衬底。

13.进一步地,所述的六边形生长平台的边长,为所述的六方晶体结构gan晶格常数的整数倍。

14.进一步地,所述的gan半导体层为单层或者多层,所述的ga2o3半导体层为单层或者多层。

15.作为本发明第二个方面,提供的上述氧化镓半导体叠层结构的制备方法技术方案如下:

16.一种上述任一项所述的氧化镓半导体叠层结构的制备方法,其特征在于,包括如下步骤:

17.s1:硅衬底清洗,去除表面氧化层;

18.s2:对硅衬底层上表面进行图形化处理,形成隔离带,将衬底层的上表面分割成多个互不相连的六边形生长平台;

19.s3:在六边形生长平台的表面上,沉积gan单晶薄膜,所沉积的gan为具有六方晶体结构的gan薄膜;

20.s4:在gan单晶薄膜层的表面上,沉积ga2o3单晶薄膜,所沉积的氧化镓薄膜为具有六方晶体结构的α-ga2o3薄膜。

21.进一步地,所述的gan薄膜层和所述的α-ga2o3薄膜层,分别还含有掺杂剂。

22.进一步地,所述的掺杂剂是n型掺杂剂的一种或多种,或p型掺杂剂的一种或多种。

23.作为本发明第三个方面,提供的包含上述氧化镓半导体叠层结构的半导体装置技术方案如下:

24.一种半导体装置,其特征在于:包括上述任一项所述的氧化镓半导体叠层结构。

25.进一步地,所述半导体装置具有立式结构。

26.进一步地,所述半导体装置是功率器件。

27.进一步地,所述半导体装置是肖特基二极管、pn结二极管、金属氧化物半导体场效应管或绝缘栅双极性晶体管。

28.为了避免在硅衬底上直接生长α-ga2o3薄膜层导致的硅衬底层上表面被氧化,从而影响薄膜质量,本发明的氧化镓半导体叠层结构为在硅衬底上先外延gan单晶薄膜层,再在gan单晶薄膜上外延α-ga2o3单晶薄膜层。由于均属于异质外延,存在着一定的晶格失配和热失配,若不对硅衬底做特别处理,而直接在大面积硅衬底上制备gan薄膜和α-ga2o3薄膜,当

达到一定厚度后,由于位错和应力的累积,会导致薄膜质量变差,甚至出现裂纹,以致不能满足功率器件的需求。

29.因此,本发明还在硅衬底的上表面加工有隔离带,例如刻蚀出一定密度的隔离沟槽,使硅衬底上表面形成多个分离且互不相连的六边形生长台面,使得在每个台面区域制备的薄膜层互不相连,不能形成合力,化整为零,减少应力,从而避免薄膜裂纹的出现,有效提升薄膜的品质,满足功率器件需求。

30.本发明将生长平台的边长设计为gan单晶晶格常数a的整数倍的目的在于这遵循了gan单晶的六方晶体结构,能减少制备过程中的晶格损坏,进一步提高半导体装置的品质。

31.本发明通过对硅衬底进行六边形图形化处理,用一定宽度的隔离带在衬底上形成多个分离的六边形的生长平台,然后在六边形的生长平台上先沉积gan薄膜层,再在gan薄膜层的上表面沉积α-ga2o3薄膜层,以实现在硅基衬底制备出高品质α-ga2o3薄膜。相较于现有技术,本发明的有益效果如下:

32.(1)相较于不做处理的硅衬底,本发明可减少晶格损坏,提升薄膜品质,弱化晶格失配和热失配的作用,减少薄膜裂纹的出现;

33.(2)相较于在硅衬底直接外延α-ga2o3薄膜,本发明解决了在硅衬底表面在沉积氧化镓的过程中被氧化形成氧化硅的问题;

34.(3)相较于在蓝宝石衬底上外延α-ga2o3薄膜,本发明省去了对蓝宝石衬底的剥离,薄膜与新衬底的键合工艺,可直接做成基于硅衬底且含有氧化镓层的垂直型器件,简化了生产工艺,可有效降低ga2o3半导体器件的制备成本。

附图说明

35.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,本发明要求的保护范围并不局限于实施例。对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

36.图1是本发明六边形图形化处理的硅(111)衬底表面局部俯视示意图;

37.图2是本发明硅衬底的六边形生长平台的局部示意图;

38.图3是本发明提供的六边形图形化硅衬底上生长六方gan薄膜和六方α-ga2o3薄膜后的俯视示意图;

39.图4是表示本发明实施方式的事例的氧化镓半导体叠层结构的剖面示意图;

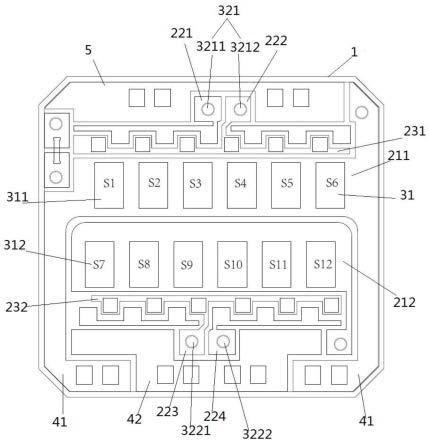

40.图5是表示本发明的肖特基势垒二极管(sbd)的一个适当例子的示意图;

41.图6是表示本发明的肖特基势垒二极管(sbd)的一个适当例子的示意图;

42.图7是表示本发明的金属氧化物半导体场效应管(mosfet)的一个适当例子的示意图;

43.图8是表示本发明的pn结二极管的一个适当例子的示意图;

44.图9是本发明所涉及的绝缘栅双极性晶体管(igbt)的一个适当例子的示意图;

45.图10是表示本发明对硅衬底进行六边形图形化设计的另一种布局示意图。

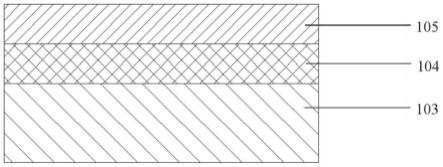

46.各附图中的标记所对应的技术特征为:

47.101为隔离带

48.102为六边形生长平台

49.103为硅衬底层

50.104为gan薄膜层

51.105为α-ga2o3薄膜层

52.103a为n 型硅衬底层

53.103c为p 型硅衬底层

54.104a为n 型gan薄膜层

55.104b为n-型gan薄膜层

56.104c为p 型gan薄膜层

57.104e为p型gan薄膜层

58.105a为n 型α-ga2o3薄膜层

59.105b为n-型α-ga2o3薄膜层

60.105d为p-型α-ga2o3薄膜层

61.105e为n型α-ga2o3薄膜层

62.106a为肖特基电极

63.106b为欧姆电极

64.107a为栅电极

65.107b为源电极

66.107c为漏电极

67.108为栅绝缘膜层

68.109a为阳极金属层

69.109b为阴极金属层

70.110a为栅电极

71.110b为发射极

72.110c为集电极

73.111为六边形生长平台

74.112为隔离带

具体实施方式

75.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本发明实施例。本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本发明。在其它情况中,省略对众所周知的系统、装置以及方法的详细说明,以免不必要的细节妨碍本发明的描述。

76.本发明通过对硅衬底进行图形化处理,通过隔离带将硅衬底层上表面分离出多个互不相连的六边形生长平台,然后在六边形生长平台上生长gan薄膜层,再在gan薄膜层上生长α-ga2o3薄膜层;硅衬底层上表面六边形生长平台的设计,使得在其上生长的gan薄膜互不相连,实现晶格失配和热失配导致的应力在大面积范围内无法形成合力,化整为零,可大幅降低应力影响,制备出高品质的gan薄膜;另外在gan薄膜层上生长α-ga2o3薄膜层,避免了

直接在硅衬底上生长α-ga2o3薄膜层,硅衬底层上表面被氧化生成氧化硅从而影响薄膜质量的问题,下面结合实施例及附图对本发明进行详细说明:

77.本发明的氧化镓半导体叠层结构的制备方法,步骤如下:

78.步骤1:对硅(111)衬底进行清洗,除去表面氧化层;

79.步骤2:利用光刻和刻蚀技术,在硅(111)衬底的上表面刻蚀出多个分离的六边形生长平台,如附图1所示,在硅衬底表面,有隔离带101,六边形生长平台102;

80.步骤3:在硅(111)衬底的六边形生长平台上,沉积gan单晶薄膜,由于隔离带上不能直接生长gan,因此随着gan的生长,在隔离带处没有gan生长,使得各个六边形生长台面上的gan薄膜在水平方向上互不相连,如附图2所示,由于gan有一定的侧向生长速率,所以隔离带的实际宽度会适当缩小;沉积gan薄膜的方法可选择mist-cvd技术、hvpe技术、mocvd技术或者mbe技术,作为优选,在这里使用mocvd技术;

81.步骤4:在已经沉积gan单晶薄膜的六边形生长平台上,在gan薄膜的上表面继续沉积α-ga2o3单晶薄膜,同样地,由于隔离带上不能直接生长α-ga2o3,因此随着α-ga2o3单晶薄膜的生长,在隔离带处会形成没有α-ga2o3生长的隔离带,使得各个六边形生长平台上的α-ga2o3薄膜在水平方向上互不相连,如附图3所示,由于α-ga2o3也有一定的侧向生长速率,所以隔离带的实际宽度会进一步适当缩小;沉积α-ga2o3薄膜的方法也可选择mist-cvd技术、hvpe技术、mocvd技术或者mbe技术,作为优选,在这里使用mist-cvd技术;

82.图4是本发明实施例的基于硅衬底的氧化镓半导体叠层结构的剖面示意图;叠层结构自下而上包括硅衬底层103,gan薄膜层104,α-ga2o3薄膜层105。

83.图5是表示本发明所涉及的肖特基势垒二极管sbd的一个例子,图5的肖特基势垒二极管sbd,采用在半导体层的表背两面分别设置电极的立式结构,具有n 型硅衬底层103a、n 型gan薄膜层104a、n-型α-ga2o3薄膜层105b、肖特基电极106a和欧姆电极106b;

84.肖特基电极以及欧姆电极的材料可以是公知的电极材料,作为所述电极材料,例如有al、mo、co、zr、sn、nb、fe、cr、ta、ti、au、pt、v、mn、ni、cu、hf、w、ir、zn、in、pd、nd或ag等金属或它们的合金;

85.肖特基电极以及欧姆电极的形成可通过真空蒸镀法或溅射法等公知的方法进行。更具体而言,例如,当形成肖特基电极时,可以使由pt构成的层和由al构成的层层叠,对于由pt构成的层以及由al构成的层,可以利用光刻法的图案化来进行;

86.当对图5的sbd施加反向偏压时,耗尽层扩大到n-型α-ga2o3薄膜层105b中,因此,成为高耐压的sbd。另外,当施加正向偏压时,电子从欧姆电极106b流向肖特基电极106a。

87.图6是表示本发明所涉及的肖特基势垒二极管sbd的一个例子,图6的肖特基势垒二极管sbd除了具有图5的sbd的结构之外,还具备绝缘层108a。更具体而言,图6的肖特基势垒二极管sbd,具备n 型硅衬底层103a、n 型gan薄膜层104a、n-型α-ga2o3薄膜层105b、肖特基电极106a、欧姆电极106b和绝缘层108;

88.作为绝缘层108的材料,例如有gao、algao、aln、al2o3、mgo、sio2或si3n4等,在本发明中,优选是具有刚玉结构的材料。绝缘层108被设置于n-型α-ga2o3薄膜层105b与肖特基电极106a之间。绝缘层的形成可以通过溅射法、真空蒸镀法或cvd法等公知的方法进行;

89.针对肖特基电极或欧姆电极的形成或材料等,与所述图5的肖特基势垒二极管sbd的情况相同;

90.图6的肖特基势垒二极管sbd与图5的肖特基势垒二极管sbd相比较,绝缘特性更好,具有更高的电流控制性。

91.图7是表示本发明所涉及的金属氧化物半导体场效应管mosfet的一个例子,图7的金属氧化物半导体场效应管mosfet,具有n 型硅衬底层103a、n 型gan薄膜层104a、p-型α-ga2o3薄膜层105d、栅绝缘膜层108、栅电极107a、源电极107b和漏电极107c;

92.图8是表示本发明所涉及的pn结二极管的一个例子,图8的pn结二极管,具有阳极金属层109a、p 型硅衬底层103c、p 型gan薄膜层104c、n 型α-ga2o3薄膜层105a和阴极金属层109b;

93.图9是本发明所涉及的绝缘栅双极性晶体管igbt的一个例子,图9的igbt,具有集电极110c、p 型硅衬底层103c、p型gan薄膜层104e、n型α-ga2o3薄膜层105e、n-型α-ga2o3薄膜层105b、n 型α-ga2o3薄膜层105a、栅绝缘膜层108、栅电极110a和发射极110b;

94.图1所示对硅衬底进行六边形图形化设计的布局方式在半导体装置进行单芯片分离时需要采用激光切割等方式,为此本发明还提出了图10所示对硅衬底进行六边形图形化设计的另一种布局示意图,包括六边形生长平台111,隔离带112,此种布局比之图1的六边形布局设计,利用率稍差,可以采用传统的机械切割的方式实现单芯片分离。

95.应理解,以上所述实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。