技术特征:

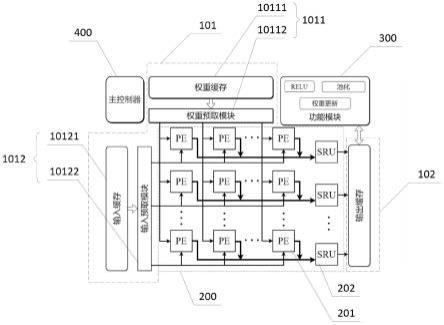

1.一种应用于卷积神经网络训练的可重构硬件加速器,其特征在于,包括缓存架构、运算处理阵列、功能模块和主控制器,其中:所述缓存架构包括输入缓存架构和输出缓存架构;所述输入缓存架构用于存储待训练网络层在候选训练阶段的待运算数据,以及将所述待运算数据按预设数据分组方式进行重新排列和分组后,输入到所述运算处理阵列中,所述候选训练阶段为所有训练阶段中任一训练阶段;所述运算处理阵列包括多个以二维数组方式排列的运算处理模块,以及与每行运算处理模块连接的缩放舍入模块;所述运算处理模块用于接收所述输入缓存架构输入的数据,并根据所述主控制器的指令,按预设移动步长进行与所述候选训练阶段相对应的卷积运算处理后,将卷积运算结果输入到对应的缩放舍入模块;所述缩放舍入模块用于对所述卷积运算结果进行数据格式转换后,发送给所述输出缓存架构进行存储;所述功能模块用于对所述输出缓存架构中的数据进行激活操作或池化操作,以及在训练完成后,对所述待训练网络层中的待训练卷积核的权重值进行权值更新;所述主控制器用于根据所述待训练卷积核的数量以及所述候选训练阶段下所述待训练网络层输入通道的数量,确定所述数据分组方式;以及,根据所述候选训练阶段以及所述移动步长,调整所述运算处理模块的内部数据连接方式,以使所述运算处理模块执行与所述移动步长和所述候选训练阶段相对应的卷积运算处理。2.根据权利要求1所述的可重构硬件加速器,其特征在于,所述输入缓存架构包括第一输入架构和第二输入架构;所述第一输入架构包括第一输入缓存模块和第一输入预取模块,所述第一输入缓存模块用于存储所述待运算数据中的第一输入数据,所述第一输入预取模块与所述运算处理阵列中每个运算处理模块连接,用于将所述第一输入数据按所述数据分组方式进行重新排列和分组后,确定每组第一目标数据对应的所述运算处理阵列中的目标列,并将每组第一目标数据发送给对应目标列中的每个运算处理模块;所述第二输入架构包括第二输入缓存模块和第二输入预取模块,所述第二输入缓存模块用于存储所述待运算数据中的第二输入数据,所述第二输入预取模块与所述运算处理阵列中每个运算处理模块连接,用于将所述第二输入数据按所述数据分组方式进行重新排列和分组后,确定每组第二目标数据对应的所述运算处理阵列中的目标行,并将每组第二目标数据发送给对应目标行中的每个运算处理模块。3.根据权利要求2所述的可重构硬件加速器,其特征在于,所述第二输入预取模块将所述第二目标数据发送给对应目标行中的所有运算处理模块时,是按照预设的时钟周期,将所述第二目标数据中每个数据依次发送给对应目标行中的所有运算处理模块。4.根据权利要求2所述的可重构硬件加速器,其特征在于,如果所述候选训练阶段为fp阶段,则所述第一输入数据为所述待训练网络层中多个待训练卷积核的权重值,所述第二输入数据为所述待训练网络层的多通道输入激活值;如果所述候选训练阶段为bp阶段,则所述第一输入数据为所述待训练网络层中多个旋转卷积核的权重值,所述第二输入数据是根据所述待训练网络层的多通道输入误差值确定的,所述旋转卷积核为将所述待训练卷积核旋转一百八十度后得到的矩阵;如果所述候选训练阶段为wg阶段,则所述第一输入数据是根据所述待训练网络层的多

通道误差值确定的,所述第二输入数据为所述待训练网络层的多通道输入激活值。5.根据权利要求4所述的可重构硬件加速器,其特征在于,所述运算处理模块包括mac阵列、加法器组、多路选择器组以及部分和fifo队列;所述mac阵列包括多个以二维数组方式排列的mac,所述mac的数量及排列方式与目标权重矩阵的尺寸相同,所述目标权重矩阵为目标待训练卷积核中目标通道的权重矩阵,所述目标待训练卷积核为多个待训练卷积核中任一待训练卷积核,所述目标通道为所述目标待训练卷积核中的任一通道;所述mac包括第一外部端口、第二外部端口、内部端口、乘法器、加法器、多路选择器和寄存器,用于将所述第一外部端口的输入数据与所述第二外部端口的输入数据相乘后,再与所述内部端口的输入数据相加,得到中间结果,并根据所述主控制器的指令,将所述中间结果按与所述候选训练阶段相对应的路径进行传递,其中,所述第一外部端口的输入数据为接收到的第一目标数据中与所述mac的位置相对应的目标位置处的第一目标值,所述第二外部端口的输入数据为接收到的第二目标数据中需与所述第一目标值相乘的所有第二目标值,所述内部端口的输入数据为卷积运算过程中的部分和、前一个mac传递的结果或者所述mac输出的中间结果三者中的一个,所述内部端口的输入数据的选择由所述多路选择器实现;所述加法器组包括两个加法器,用于根据所述主控制器的指令,在卷积运算过程中对多路mac输出的中间结果进行求和,并将结果输出到所述部分和fifo队列;所述多路选择器组包括多个行多路选择器,用于将每个mac输出的中间结果以及所述加法器组输出的结果传送到所述部分和fifo队列中,其中,所述行多路选择器的数量与所述mac阵列的行数量相同;所述部分和fifo队列用于存储卷积运算过程中的所有部分和。6.根据权利要求1所述的可重构硬件加速器,其特征在于,所述对所述卷积运算结果进行数据格式转换,包括:在完成所述待训练网络层在所述候选训练阶段的所有计算后,从目标运算处理模块输出的所有卷积运算结果中,确定第一最大值,并将所述第一最大值确定为局部最大值,所述目标运算处理模块为多个运算处理模块中任一运算处理模块;根据所述第一最大值,确定由int32格式转换为int8格式时的移位位数;按照所述移位位数,将所述目标运算处理模块输出的每个卷积运算结果由int32格式转换为int8格式,得到候选结果;从所述目标运算处理模块所在行的每个运算处理模块对应的局部最大值中,确定第二最大值,并将所述第二最大值确定为全局最大值;获取目标局部最大值对应的第一移位位数,以及所述全局最大值对应的第二移位位数,所述目标局部最大值为所述目标运算处理模块所在行的所有运算处理模块对应的局部最大值中任一局部最大值;确定所述第一移位位数与所述第二移位位数之间的移位差异;根据所述移位差异,对目标候选结果的数据格式进行二次调整,所述目标候选结果为所述目标局部最大值所对应的运算处理模块输出的候选结果。

技术总结

本申请提供一种应用于卷积神经网络训练的可重构硬件加速器。该可重构硬件加速器包括:缓存架构、运算处理阵列、功能模块和主控制器,缓存架构包括输入缓存架构和输出缓存架构,运算处理阵列包括多个以二维数组方式排列的运算处理模块,在使用时利用输入缓存架构按预设数据分组方式对待运算数据进行重新排列和分组后,发送给运算处理模块进行处理,并通过在不同的训练阶段动态调整运算处理阵列中的每个运算处理模块的内部数据连接方式,以使运算处理模块按移动步长进行与候选训练阶段相对应的卷积运算处理。整个装置的计算方式较为灵活,可并行处理多通道运算,而且仅采用硬件架构即可满足不同训练阶段的计算需求,因而具有较高的模型训练效率。具有较高的模型训练效率。具有较高的模型训练效率。

技术研发人员:王中风 邵海阔 林军

受保护的技术使用者:南京大学

技术研发日:2021.07.30

技术公布日:2023/2/6

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。