1.本公开涉及存储器中的数据操作的管理,更具体地涉及执行存储器设备内的数据拷贝、数据初始化和数据处理操作而无需涉及数据在存储信道上的移动。

背景技术:

2.在多个应用同时运行的系统中,可以触发诸如数据拷贝和数据初始化操作之类的数据操作,以在存储器设备内将数据从一个位置传输到另一位置并且将数据初始化为特定的值。在传统的方法中,存储器设备内的数据操作可以通过在存储信道上传输数据来执行,即使这样的操作不需要任何计算也是如此。因此,在存储器设备内执行的数据操作可能需要高的延迟、带宽和能量/功率,其可进一步降低系统的性能。

3.图1a和图1b描绘了用于执行数据拷贝操作的示例传统存储器系统。如图1a和图1b所示,传统存储器系统包括存储器设备和主机。存储器设备通过存储信道与主机进行通信。主机包括中央处理单元(cpu)、存储器拷贝加速器/高速缓存控制块和存储器控制器。存储器设备包括多个存储器组/阵列、与多个存储器组相关联的多个感测放大器、预取缓存器及管芯上纠错码(ecc)块、命令解码器、耦接到行地址电路系统和列地址电路系统的地址电路系统、以及输入/输出(io)电路系统。

4.主机的存储器拷贝加速器/高速缓存控制块可以响应于来自至少一个应用(其正在主机上执行)的针对在存储器设备中将数据从一个位置传输到另一位置的请求,发起针对数据拷贝操作的触发。数据拷贝操作可以涉及从一个位置读取/访问所需要的数据和将已取得的数据写入存储器设备内的另一位置。

5.存储器拷贝加速器/高速缓存控制块与存储器控制器传递关于已发起的针对数据拷贝操作的触发。基于已发起的针对数据拷贝操作的触发,存储器控制器识别用于访问/读取数据的源位置和必须将已访问/读取的数据写入的目的地位置。源位置和目的地位置包括诸如但不限于以下信息,诸如,读取和写入所需要的数据的存储器组的组id(即,组地址)、组中的行地址和已识别的组id中的行中的列地址之类。然后,当已经在存储器组中激活已识别的用于访问数据的相应的行时,存储器控制器利用已识别的列地址,在存储信道上对存储器设备的io电路系统发布read命令,因此可以在存储器组的感测放大器处获得数据。io电路系统对命令解码器传输read命令且对列地址电路系统传输列地址。命令解码器将read命令提供给与已识别的存储器组相关联的组/列选择逻辑部。列地址电路系统将已接收的列地址馈送到与已识别的存储器组相关联的组/列选择逻辑部。组/列选择逻辑部从相应的感测放大器和存储器组读取数据,所述感测放大器和存储器组对应于与激活的行内的已接收的列地址(源位置)相对应的列。组/列选择逻辑部然后将已取得的数据传输到预取缓存器及管芯上ecc检验器。io电路系统通过存储信道将已取得的数据从预取缓存器及管芯上ecc检验器传输到存储器控制器。

6.存储器控制器将已接收的数据转发到存储器拷贝加速器/高速缓存控制块。存储

器拷贝加速器/高速缓存控制块将所需要的数据拷贝进高速缓存,并且将已拷贝的数据提供给存储器控制器,已将已接收的数据写入存储器组中的目的地位置。在接收用于写入存储器组中的数据时,存储器通过激活存储器组中的数据必须写入的相应的行,生成write命令。存储器控制器通过存储信道,对存储器设备的io电路系统发布write命令和数据、以及数据必须写入的存储器组的列地址。io电路系统将已接收的列地址转发到列地址电路系统,将write命令转发到命令解码器,以及将数据转发到数据必须写入的相关联的存储器组的组/列选择逻辑部。命令解码器解码write命令,并且对数据必须写入的相关联的存储器组的组/列选择逻辑部发布已解码的write命令。列地址电路系统将已接收的列地址馈送到数据必须写入的相关联的存储器组的组/列选择逻辑部。组/列选择逻辑部将与存储器组相关联的相应的感测放大器连接到预取缓存器,以将已接收的数据写到已激活的行内的已接收的列地址(目的地位置)。因此,在传统系统中,数据拷贝操作涉及通过存储信道的数据移动。通过存储信道的数据移动可以一次作为一个字节/字/高速缓存行来执行,其可导致高延迟。而且,通过存储信道的数据移动可以涉及大量数据传输,其可以进一步影响共享存储器带宽的并发运行的应用的性能。此外,通过存储信道的数据移动可以消耗更多能量/功率。

7.目的

8.本文的实施例的主要目的是,公开了用于执行存储器设备之中的数据操作而不涉及数据在存储通道上的移动的方法及系统,其中,所述数据操作包括数据拷贝操作、数据处理操作和数据初始化操作。

9.本文的实施例的另一目的是,公开了用于实现存储器设备内的缓存器和促进缓存器中的数据移动以用于执行存储器设备内的数据拷贝操作的方法及系统。

10.本文的实施例的另一目的是,公开了用于实现存储器设备内的存储器中处理(pim)集群以从缓存器取得数据和处理已取得的数据的方法及系统。

11.本文的实施例的另一目的是,公开了用于利用物理连续位置地址、分散的位置地址和已知数据模式中的至少一种来初始化存储器设备内的数据的方法及系统。

12.本文的实施例的另一目的是,公开了用于发起缓存器填充命令(buff_fill命令)和缓存器拷贝命令(buff_copy命令)以执行存储器设备内的数据操作的方法及系统。

技术实现要素:

13.根据本发明的示例性实施例,一种存储器系统,包括:存储器设备,包括多个存储器组和数据总线管理电路;以及,主机,耦接到所述存储器设备。所述主机包括:存储器控制器,被配置为检测由至少一个应用发起的用于对存储在所述存储器设备内的数据执行至少一个操作的至少一个触发,所述至少一个操作包括数据拷贝操作和数据处理操作中的至少一种;以及,通过使用至少一个缓存器填充命令和至少一个缓存器拷贝命令来实现所述存储器设备的数据总线管理电路和所述多个存储器组中的至少一个存储器组之间的数据的移动而无需与所述主机交换数据,对所述存储器设备内的数据执行所述至少一个操作。

14.根据本发明的示例性实施例,一种用于执行耦接到主机的存储器设备内的数据操作的方法,包括:由存储器控制器检测由至少一个应用发起的用于对存储在所述存储器设备内的数据执行至少一个操作的至少一个触发,所述至少一个操作包括数据拷贝操作和数

据处理操作中的至少一种;以及,由所述存储器控制器通过使用至少一个缓存器填充命令和至少一个缓存器拷贝命令、实现所述存储器设备的数据总线管理电路和所述存储器设备的多个存储器组中的至少一个存储器组之间的数据的移动而无需与所述主机交换数据,对存储在所述存储器设备内的数据执行所述至少一个操作。

15.根据本发明的示例性实施例,一种存储器系统中的耦接到存储器设备的主机,包括:中央处理单元(cpu);存储器拷贝加速器电路,耦接到cpu并且配置为检测来自运行在cpu上的至少一个应用的针对存储器设备内的数据拷贝操作的触发,所述数据拷贝操作包括,在存储器设备内将至少一个应用所需要的数据从至少一个源位置拷贝到至少一个目的地位置;以及,存储器控制器,被配置为通过使用至少一个缓存器填充命令和至少一个缓存器拷贝命令,实现存储器设备的数据总线管理电路和存储器设备的多个存储器组中的至少一个存储器组之间的数据的移动而无需从所述至少一个存储器组接收数据,来执行数据拷贝操作。

16.根据本发明的示例性实施例,一种存储器系统中的耦接到主机的存储器设备,包括:多个存储器组;以及,数据总线管理电路,被配置为,响应于来自所述主机的至少一个缓存器填充命令,从所述多个存储器组中的第一存储器组的至少一个源位置接收,运行在所述主机上的至少一个应用所需要的数据、并且将已接收的数据存储在所述数据总线管理电路的缓存器中,以及,响应于来自所述主机的至少一个缓存器拷贝命令,将所述缓存器中已存储的数据写到所述多个存储器组中的第二存储器组的至少一个目的地位置。

17.当结合以下描述和附图考虑时,将更好地了解和理解本文中的示例实施例的这些和其他方面。然而,应该理解,虽然以下描述指示了示例实施例及其许多具体细节,但是以下描述是通过说明而非限制性的方式给出的。可以在不脱离本文中的示例实施例的精神的前提下在其范围内做出多种改变和修改,并且本文中的示例实施例包括所有这样的修改。

附图说明

18.在附图中示出了本文的实施例,在附图中相同的附图标记表示各个附图中的对应部分。从参考附图的以下描述中将更好地理解本文的实施例,在附图中:

19.图1a和图1b描绘了用于执行数据拷贝操作的示例传统存储器系统;

20.图2a和图2b描绘了根据如本文所公开的实施例的存储器系统;

21.图3a-图3d是描绘用于执行根据如本文所公开的实施例的存储器设备内的数据操作的存储器系统的各组件的框图;

22.图4a-图4c是描绘根据如本文所公开的实施例的数据拷贝和初始化操作的示例图;

23.图5是描绘根据如本文所公开的实施例的缓存器填充命令(buff_fill命令)、缓存器拷贝命令(buff_copy命令)、read命令和write命令的示例命令格式的图;

24.图6是描绘根据如本文所公开的实施例的用于执行存储器设备内的数据操作的方法的流程图;

25.图7是描绘根据如本文所公开的实施例的用于执行存储器设备内的数据拷贝操作的方法的流程图;

26.图8是描绘根据如本文所公开的实施例的用于执行存储器设备内的数据处理操作

的方法的流程图;

27.图9是描绘根据如本文所公开的实施例的用于执行数据初始化操作的方法的流程图;

28.图10a和图10b是描绘根据如本文所公开的实施例的利用计算数据初始化存储器中处理(pim)集群以及使用已初始化的计算数据处理pim集群上的数据的示例序列图;以及

29.图11是描绘根据如本文所公开的实施例的在具有多排容量的存储器模块级执行的数据拷贝操作的示例图。

具体实施方式

30.参考在附图中示出并在以下描述中详述的非限制性的示例实施例,更全面地解释本文中的实施例及其多种特征和有利的细节。省略对于公知组件和处理技术的描述以便不会不必要地混淆实施例。本文中的描述仅旨在便于理解可以实现本文中的示例实施例的方式并进一步使本领域技术人员能够实现本文中的示例实施例。因此,本公开不应被理解为限制本文中的示例实施例的范围。

31.本文的实施例公开了用于执行存储器设备内的数据操作而不涉及数据在存储信道上的移动的方法及系统,其中,所述数据操作包括数据拷贝操作、数据处理操作和数据初始化操作中的至少一种。

32.本文的实施例公开了用于通过实现存储器设备内的缓存器来执行存储器设备内的数据拷贝操作的方法及系统。

33.本文的实施例公开了用于通过实现存储器设备内的存储器中处理(pim)集群来执行存储器设备内的数据处理操作的方法及系统。

34.本文的实施例公开了用于在存储器组和pim集群之间执行数据拷贝操作而无需涉及通过存储信道的数据移动的方法及系统。

35.本文的实施例使用缓存器填充命令和缓存器拷贝命令,以用于执行存储器设备内的数据操作。

36.现在参考示出示例实施例的附图,更具体地参考图2a至图10,其中,贯穿附图类似的附图标记一致地表示对应的特征。

37.图2a和图2b描绘了根据如本文所公开的实施例的存储器系统200。存储器系统200包括至少一个存储器设备202和主机204。

38.本文提及的存储器设备202可以具有用于存储数据的存储器组件的设备。数据可以与部署在主机204上的多个应用(即,应用程序)有关。应用程序可以是广泛的、自包含的程序,其可以为用户执行特定功能。应用程序可以包括但不限于与呼叫有关的应用、顶层上(ott)应用、流应用、与文件下载有关的应用、社交网络应用、相机应用、与iot有关的应用、企业应用、数据管理应用、与增强现实(ar)有关的应用、与游戏有关的应用等,以及许多其他应用程序。本文提及的存储器设备202还可以是如图3a所描绘的用于存储数据以及处理从主机204接收的数据的存储器中处理(pim)设备(处理器逻辑与存储器的集成)。

39.在实施例中,存储器设备202可以包括随机存取存储器、闪存、固态盘(ssd)、磁盘、高速缓存或可以存储所需要的数据的任何其他设备中的至少一项。随机存取存储器的示例可以是但不限于静态随机存取存储器(sram)、动态随机存取存储器(dram)、同步图形随机

存取存储器(sgram)、高带宽存储器(hbm)、磁阻式随机存取存储器(mram)等。闪存的示例可以是但不限于nor闪存、nand闪存等。在实施例中,存储器设备202可以是至少一种类型的dram,例如但不限于:同步dram(sdram)、双倍数据速率同步dram(ddr sdram)、图形双倍数据速率dram(gddr dram)、四倍数据速率dram(qdr dram)、视频dram(vdram)、扩展数据输出dram(edo dram)、多组dram(mdram)等。在实施例中,存储器设备202可以是单片存储器电路、半导体管芯、存储器管芯的堆叠、芯片、经封装的存储器电路或任何其他类型的有形存储器电路中的至少一项。

40.存储器设备202可以通过存储信道/总线与主机204通信。存储信道可以支持各种协议,例如但不限于存储器协议(例如,双列直插存储器模块(dimm)接口、lpddr、lpdram、jedec等)、输入/输出(i/o)协议(例如,pci、infiniband等)、网络协议(例如,以太网、传输控制协议/网际互连协议(tcp/ip)等)、存储协议(例如,网络文件系统(nfs)、串行高级技术附件(sata)、串行附接scsi(sas)等)、无线协议等,以用于实现存储器设备202与主机204通信。

41.在实施例中,存储器设备202包括多个存储器组202a和数据总线管理电路系统(即,数据总线管理电路)202b,如图2a所示。存储器组202a可以存储部署在主机204上的多个应用的数据。数据总线管理电路系统202b可以被配置为,在存储器组202a的读/写操作期间,管理从存储器组访问或要写入存储器组的数据。在实施例中,当主机204希望执行在存储器中拷贝时,数据总线管理电路系统202b促进从存储器设备202内的存储器组202a取得的数据的存储,而无需允许已取得的数据在存储信道上流动,以使存储在存储器设备202内的数据可以用于写入存储器组202a而无需通过存储信道访问数据。

42.在实施例中,如图2b所示,存储器设备202还包括pim集群(即,pim电路)202c,其中,pim集群202c可以与数据总线管理电路系统202b耦接。pim集群202c可以被配置为,从数据总线管理电路系统202b接收(从存储器组202a访问的)数据并且对已接收的数据进行处理。在本文的示例中,对已接收的数据的处理可以涉及执行计算操作,例如但不限于:算术计算、逻辑计算、编码、解码、过滤、数字信号处理(dsp)运算(例如,调换(transpose)、矩阵运算、快速傅立叶变换(fft)等)等。pim集群202c还将经处理的数据提供给数据总线管理电路系统202b,数据总线管理电路系统202b进一步将已接收的经处理的数据写入存储器组202a。

43.本文提及的主机204可以是处理器、片上系统(soc)、服务器、集成芯片(ic)、芯片组、移动计算设备、手机、智能手机、平板计算机、平板手机、个人数字助理(pda)、膝上型计算机、计算机、可穿戴设备、iot(物联网)设备、可穿戴计算设备、车载信息娱乐系统、医疗设备、相机、应用处理器(ap)、多处理器系统、基于微处理器的可编程消费电子产品、网络计算机、小型计算机、大型计算机和/或支持存储器设备202的任何其他设备中的至少一项。

44.主机204可以被配置为,通过维护关于存储器设备202的信息,管理存储器设备202的操作。操作可以是读操作、写操作等中的至少一种。信息可以是关于存储器组202a、存储在存储器组202a中的数据、已存储的数据的位置/地址等的信息中的至少一项。

45.在实施例中,主机204还可以被配置为,当从正在主机204上执行的至少一个应用接收请求时管理存储器设备202内的数据操作。数据操作包括数据拷贝操作、数据处理操作和数据初始化操作中的至少一种。数据拷贝操作涉及:从至少一个位置(在下文中称为源位

置)读取/访问数据,以及将已取得的数据写入存储器设备202内的至少一个其他位置(在下文中称为目的地位置)。本文提及的数据可以是:存储在存储器设备202的至少一个存储器组202a中且由至少一个应用或另一应用需要的数据。在数据拷贝操作的情况下,源位置和目的地位置可以是不同的。源位置和目的地位置可以是同一存储器组202a内的不同位置、不同存储器组202a内的不同位置等中的至少一项。数据处理操作涉及从源位置读取/访问数据、处理已取得的数据、以及将已取得的数据写入存储器设备202内的目的地位置。在数据处理操作的情况下,源位置和目的地位置可以是相同或不同位置。数据初始化操作涉及将已取得的数据初始化为特定的值,其中,所述特定的值可以是源位置和目的地位置的地址、与要读取或写入的数据模式相关联的地址等中的至少一种。

46.如图2a所示,为了执行数据拷贝操作,主机204从至少一个应用接收针对数据拷贝操作的请求。在接收请求时,主机204识别需要拷贝的数据、源位置和目的地位置。源位置可以包括关于至少一个存储器组202a中必须从其访问数据的至少一个位置的信息。目的地位置可以包括关于在同一存储器设备202中数据必须写入的至少一个位置的同一存储器组202a或不同存储器组202a中的信息。源位置和目的地位置中指定的至少一个存储器组202a可以是不同的组或同一组。此后,主机204发起:用于从存储器设备202的至少一个存储器组202a的已识别的位置(源位置)读取所需要的数据的缓存器填充(buff_fill)命令。在实施例中,buff_fill命令可以是:将正常read命令(其在标准规范中进行定义)与执行buff_fill命令所需要的附加信息一起编码的命令。将参考图5详细描述buff_fill命令的格式。例如,buff_fill命令可以发起存储器设备202上的读取操作,并且可以将读取的数据存储在存储器设备202的缓存器中而无需从存储器设备202提供给主机204。主机204对存储器设备202发布buff_fill命令以及至少一个存储器组202a的已识别的位置(源位置)。在接收(即,响应于)buff_fill命令时,存储器设备202发起读取操作,以访问相应的存储器组202a中的已识别的位置(源位置)。在实施例中,当源位置是多个时,buff_fill命令可以发布多个。当从已识别的位置访问数据时,数据总线管理电路系统202b存储从至少一个存储器组202a的已识别的位置取得的数据,而无需通过存储信道将数据提供给主机204。

47.主机204可以通过跟踪(或计数)针对读取操作所定义的时间,对读取操作(从存储器组202a的源位置访问数据)的完成进行识别。在从存储器组202a的已识别的位置访问数据之后,主机204发起缓存器拷贝(buff_copy)命令,以将已访问获取的数据写入至少一个存储器组202a的已识别的位置(目的地位置)。在实施例中,buff_copy命令可以是,将正常write命令(其在标准规范中进行定义)与执行正常write命令所需要的附加信息一起编码的命令。将参考图5详细描述buff_copy命令的格式。例如,buff_copy命令可以发起存储器设备202上的写操作,并且要写入存储器设备202的数据可以由存储器设备202的缓存器提供而无需从主机204提供。在实施例中,主机204发起buff_copy命令无需从存储器设备202接收已取得的数据。主机204对存储器设备202发布已发起的buff_copy命令以及目的地位置。在实施例中,当目的地位置是多个时,buff_copy命令可以发布多个。在存储器设备202处,当接收buff_copy命令时,数据总线管理电路系统202b将已存储的已取得的数据写入至少一个存储器组202a的已识别的位置(目的地位置)。因此,可以在不涉及通过存储信道在存储器设备202和主机204之间的数据移动而执行数据拷贝操作,这进一步提高了存储器系统200的性能和能量效率,并且通过使用基于主机204驱动的数据掩蔽,实现了甚至是将一

个字节的数据从一个位置拷贝到另一位置。

48.如图2b中所示,为了执行数据处理操作,主机204从至少一个应用接收针对数据处理操作的请求。在接收这样的请求时,主机204识别需要拷贝/处理的数据、处理请求、关于源位置的信息、和关于存储器设备202内的目的地位置的信息。源位置可以包括关于至少一个存储器组202a中必须从其访问数据的至少一个位置的信息。目的地位置可以包括关于至少一个存储器组202a中数据必须写入的至少一个位置的信息。关于源位置的信息中所指定的位置和至少一个存储器组202a可以与关于目的地位置的信息中所指定的那些相同或不同。此后,当存储器系统200或存储器设备202启动时,主机204利用对数据进行处理所需要的计算数据来初始化pim集群202c。备选地,当pim集群202c从数据总线管理电路系统202b接收数据以进行处理时,主机204可以利用计算数据来初始化pim集群202c。将参考图10a和图10b详细描述用于使用计算数据对数据进行处理的pim集群202c的初始化。此外,主机204发起buff_fill命令,以从存储器设备202的至少一个存储器组202a的已识别的位置(源位置)读取所需要的数据并且处理已取得的数据。主机204对存储器设备202发布buff_copy命令以及至少一个存储器组202a的已识别的位置(源位置)。在接收buff_fill命令时,存储器设备202可以发起读取操作,以访问相应的存储器组202a中的已识别的位置。当从已识别的位置访问数据时,数据总线管理电路系统202b存储从至少一个存储器组202a的已识别的位置取得的数据,而无需通过存储信道将数据提供给主机204。此外,pim集群202c与数据总线管理电路系统202b通信并且接收已取得的数据。pim集群202c使用从主机204接收的计算数据,对已接收的已取得的数据进行处理。

49.一旦在存储器设备202中的pim集群202c上完成处理,主机204就发起buff_copy命令,以将已取得的数据写入至少一个存储器组202a的已识别的位置(目的地位置)。在实施例中,主机204发起buff_copy命令而无需从存储器设备202接收经处理的数据。在对数据进行处理的末尾,主机204对具有目的地位置的存储器设备202发布已发起的缓存器拷贝命令。在存储器设备202处,当接收缓存器拷贝命令时,在pim操作之后,pim集群202c将经处理的数据提供给数据总线管理电路系统202b,数据总线管理电路系统202b进一步将经处理的数据写入至少一个存储器组202a的已识别的位置(目的地位置)。因此,数据处理操作可以无需涉及通过存储信道的数据移动而执行,其进一步提高了存储器系统200的性能和能量效率。

50.在实施例中,主机204也可以发布用于执行存储器设备202上的读操作和写操作的buff_fill命令和buff_copy命令,同时执行与正常的read命令和write命令相对应的正常的读操作和写操作(即,涉及通过存储信道的数据移动)。因此,buff_fill命令和buff_copy命令与正常的read命令和write命令可以共存,并且与buff_fill命令和buff_copy命令相对应的读操作和写操作可以不影响正常的读操作和写操作地执行。

51.图3a和图3b是描绘用于执行根据如本文所公开的实施例的存储器设备202内的数据拷贝操作的存储器系统200的各组件的框图。如图3a所示,存储器设备202包括多个存储器组202a、多个感测放大器302、组/列选择逻辑部330、输入/输出(io)电路系统304、地址电路系统(即,地址缓存器)306、行地址电路系统(即,行地址解码器)308、列地址电路系统(即,列地址解码器)310、命令解码器312、预取缓存器及ecc 314、以及数据总线管理电路系统202b。数据总线管理电路系统202b包括缓存器316、门控器318和复用器(mux)320,用于在

数据拷贝操作期间对从至少一个存储器组202a访问/要写入至少一个存储器组202a的数据进行管理。在实施例中,数据总线管理电路系统202b的缓存器316可以与预取缓存器及ecc 314集成,如图3b所示。

52.多个存储器组202a可以被配置为,存储与部署在主机204上的多个应用有关的数据。利用组标识符(组id)标识的每个存储器组202a,可以包括多个存储器子阵列。每个存储器子阵列可以以可寻址的行和列布置。每个子阵列可以包括连接到至少一个感测放大器302的存储器单元的二维阵列。存储器单元可以包括用于以位的形式存储数据的电容器和确定单元当前是否针对数据进行访问的存取晶体管。存储器单元可以使用导线连接到至少一个感测放大器302,该导线在本文可以被称为位线。存储器单元的存取晶体管可以通过导线控制,该导线在本文可以被称为字线。

53.io电路系统304可以被配置为从主机204接收命令。在本文的示例中,所述命令可以是buff_fill命令和buff_copy命令中的至少一个,其用于通过实现数据在数据总线管理电路系统202b和存储器组202a之间的移动而无需与主机204交换数据,执行存储器设备202内的数据拷贝操作。buff_fill命令可以用于从源位置访问/读取数据,并且buff_copy命令可以用于将已取得的数据写入存储器设备202内的目的地位置。io电路系统304还可以从主机204接收正常的read或write命令,以执行正常的读操作或写操作。io电路系统304还可以被配置为利用来自主机204的命令接收地址输入。所述地址输入可以指示关于源位置和目的地位置的信息。源位置可以包括关于至少一个存储器组202a中必须从其访问数据的(例如,在存储器子阵列中的)至少一个位置的信息。目的地位置可以包括与至少一个存储器组202a中必须数据必须写入的(例如,在存储器子阵列中的)至少一个位置有关的信息。源位置和目的地位置中指定的位置可以彼此不同,并且源位置中指定的至少一个存储器组202a可以与目的地位置的那个不同或相同。包括在源位置和目的地位置中的位置可以利用至少一个存储器组202a的组标识符(id)、行地址、利用行地址选择的行内的列地址等中的至少一个标识。io电路系统304还将地址输入提供给地址电路系统306,并且将已接收的命令提供给命令解码器312。

54.地址电路系统306可以被配置为,选择性地将已接收的地址输入到行地址电路系统308和列地址电路系统310中的至少一个,以从存储器组202a读取的数据/对存储器组202a写数据。地址电路系统306将已接收的行地址提供给行地址电路系统308,行地址电路系统308进一步将行地址提供给与已接收的组id相关联的存储器组202a,以使相应的行线/字线激活,以访问/写入数据,并且可以启用连接到已激活的行的感测放大器302。地址电路系统306将已接收的列地址提供给列地址电路系统310。列地址电路系统310可以将已接收的列地址提供给组/列选择逻辑部330,组/列选择逻辑部330从感测放大器302读取数据/对感测放大器302写入数据,该感测放大器302与相应的已接收的列地址(源位置/目的地位置)的存储器组相关联。

55.命令解码器312可以被配置为,解码从io电路系统304接收的buff_fill/buff_copy命令,并且将已解码的buff_fill/buff_copy命令提供给数据总线管理电路系统202b的缓存器316。命令解码器312将已解码的buff_fill命令提供给缓存器316,以存储从至少一个存储器组202a的至少一个位置取得的数据。命令解码器312将已解码的buff_copy命令提供给缓存器316,以通过mux 320将已存储的已取得的数据提供给感测放大器302,以将数

据写入至少一个存储器组202a的至少一个位置。命令解码器312还可以被配置为:基于buff_fill命令和buff_copy命令的操作码(op码),将buff_fill命令/buff_copy命令转换为read命令/write命令;以及通过组/列选择逻辑部330或用于从存储器组202a读取数据/对存储器组202a写入数据的相关的内部电路系统,将已转换的命令提供给感测放大器302。在实施例中,操作码可以存储在从主机240接收的指令的字段中,其标识要执行的操作的类型。

56.感测放大器302和相关联的存储器组202a,在存储器设备202的组/列选择逻辑部330或相关的内部电路系统的控制下,可以从源位置读取/访问数据或将已取得的数据/读取的数据写入目的地位置。要注意的是,所述命令可以提供给组/列选择逻辑部330、感测放大器302或存储器设备202的任何其他相关的内部电路系统中的至少一个,以执行读操作或写操作,并且其可以基于存储器设备202的类型、存储器设备202的规范等中的至少一个变化。

57.预取缓存器和纠错码(ecc)模块314可以存储通过感测放大器302和至少一个存储器组202a从源位置取得的数据,并且如果存在任何已检测的错误,则纠正所述位。

58.响应于来自io电路系统304的buff_fill命令,缓存器316可以从预取缓存器及ecc 314接收数据,并且存储从与已接收的buff_fill命令相关联的至少一个存储器组202a的源位置取得的数据。在实施例中,缓存器316可以是预取缓存器及ecc模块314,其直接接收和存储从与已接收的buff_fill命令相对应的源位置取得的数据,如图3b所示。在实施例中,缓存器316可以与预取缓存器及ecc模块314集成,以接收和存储从感测放大器302取得的数据,如图3b所示。缓存器316还响应于buff_copy命令,通过mux 320将已存储的数据提供给组/列选择逻辑部330,以将数据写入与buff_copy命令相关联的至少一个存储器组202a的目的地位置。

59.门控器318可以在存储器组202a的写操作期间(即,当接收buff_copy命令时)操作/启用。门控器318可以在命令解码器312检测到buff_copy命令时禁用,因此,缓存器316中的已存储的已取得的数据不流到io电路系统304。在实施例中,命令解码器312在检测到buff_copy命令时,可以对门控器318生成禁用信号。在来自主机204的正常read命令的操作期间,门控器318可以被启用,以使数据可以传送到主机204。在实施例中,命令解码器312在检测到未被编码在buff_fill命令中的正常read命令时,可以对门控器318生成启用信号。为了简化附图,命令解码器312和门控器318之间的信号路径未用参考标记指示。

60.mux 320可以在存储器组202a的写操作期间(即,当接收buff_copy命令时)操作/启用。当buff_copy命令被命令解码器312检测到时,mux 320可以从缓存器316选择数据,并且通过组/列选择逻辑部330将已选择的数据提供给感测放大器302。在实施例中,命令解码器312在检测buff_copy命令时,可以对mux 320生成禁用信号。感测放大器302和相关联的存储器组202a将已接收的已读取/已取得的数据写入目的地位置。在实施例中,感测放大器302也可以用作写驱动器。本发明不限于此。在实施例中,可以提供单独的写驱动器,以将从主机204接收的数据传送到至少一个存储器组202a。在正常write命令的操作期间,mux 320可以被启用,以使数据可以通过组/列选择逻辑部330从主机204直接传送到至少一个存储器组202a。在实施例中,命令解码器312在检测到未被编码在buff_copy命令中的正常write命令时,可以对mux 320生成启用信号。为了简化附图,命令解码器312和mux 320之间的信

号路径未用参考标记指示。

61.如图3a和图3b所示,主机204包括中央处理单元(cpu)322、存储器拷贝加速器/高速缓存控制块324和存储器控制器326。cpu 322可以包括单个处理器、多个处理器、多个同构内核、多个异构内核、不同种类的多个中央处理单元(cpu)等中的至少一项。cpu 322可以被配置为执行多个应用以执行至少一个任务。任务的示例可以是但不限于:人脸检测、照片处理、媒体(音频、视频、图像等)处理、人脸标记、媒体中的对象识别、与图形有关的处理、与游戏有关的处理、机器学习任务、人工智能(ai)任务等。

62.存储器拷贝加速器/高速缓存控制器块324可以被配置为,维护和管理关于正在cpu 322和存储器设备202上执行的多个应用的信息。在实施例中,存储器拷贝加速器/高速缓存控制器块324可以检测由(在cpu 322上执行的)至少一个应用发起的针对数据操作请求。在实施例中,存储器拷贝加速器/高速缓存控制器块324检查应用所需要的数据的源地址和目的地址,以确定两个地址是否位于同一存储器设备中。当确定源地址和目的地址位于同一存储器设备中时,存储器拷贝加速器/高速缓存控制器块324触发存储器中数据拷贝操作。在实施例中,存储器拷贝加速器/高速缓存控制器块324可以被配置有每个存储器设备202的开始地址和结束地址,并且可以确定应用所需要的数据的源地址和目的地址是否位于同一存储器设备中202。当确定源地址和目的地址位于同一存储器设备中时,存储器拷贝加速器/高速缓存控制器块324触发存储器中数据拷贝操作。为了简化附图,在图3a和图3b上示出了单个存储器设备。然而,存储器设备202可以多个。在实施例中,多个存储器设备202可以是但不限于存储器模块、存储器管芯的堆叠或经封装的存储器设备的堆叠。例如,多个存储器设备202可以被包括在hbm(高带宽存储器)中。hbm可以包括cpu、逻辑管芯和存储器管芯的堆叠。在实施例中,存储器拷贝加速器/高速缓存控制器块324可以使用多个存储器设备202中的每一个的地址识别它们,并且当确定应用所需要的数据的源地址和目的地址位于同一存储器设备中202时,存储器拷贝加速器/高速缓存控制器块324可以触发存储器中数据拷贝操作。

63.存储器控制器326可以被配置为,维护关于存储器设备202的信息。在示例中,信息可以是但不限于存储器设备202中的存储器组202a的数量、存储在存储器组中的数据和相应的地址等。存储器控制器326接收来自存储器拷贝加速器/高速缓存控制块324的触发,以通过执行存储器设备202的存储器组202a的读操作和写操作而无需与主机204交换数据,来执行存储器设备202内的数据拷贝操作。在实施例中,存储器控制器326可以使用buff_fill命令和buff_copy命令来执行存储器设备202内的数据拷贝操作,所述buff_fill命令和buff_copy命令实现了数据总线管理电路系统202b的缓存器316到存储器组202a的数据移动,而无需与主机204交换数据。在实施例中,存储器控制器326也可以对存储器设备202发布正常read命令或write命令,同时,缓存器316存储要拷贝的有效数据,因此,与buff_fill命令和buff_copy命令相对应的读操作和写操作可以被执行而不不影响正常的读操作和写操作。

64.为了执行数据拷贝操作(如图3a和图3b所示),存储器控制器326识别由存储器拷贝加速器/高速缓存控制块324发起的针对存储器设备202内的数据拷贝操作的触发。当识别到触发时,存储器控制器326识别用于执行数据操作的信息,例如但不限于:存储器设备202内要拷贝/处理的数据、源位置、目的地位置等。此后,存储器控制器326基于已识别的所

需要的数据的源位置信息,发起缓存器填充(buff_fill)命令和与源位置相对应的地址输入信号。地址输入信号包括与必须从其访问数据的存储器组202a(源位置)的组id相对应的行地址、列地址。存储器控制器226还通过存储信道对存储器设备202的io电路系统304发布buff_fill命令和地址输入信号。

65.io电路系统304将地址输入信号转发到地址电路系统306并将buff_fill命令转发到命令解码器312。地址电路系统306将被包括在地址输入信号中的行地址和组id提供给行地址电路系统308。行地址电路系统308激活与已接收的行地址相对应的行,并且启用用于已激活的行的感测放大器。地址电路系统306将被包括在地址输入信号中的列地址提供给列地址电路系统310。列地址电路系统310将已接收的列地址转发到与已接收的组id相关联的组/列选择逻辑部330。命令解码器312基于从存储器控制器326接收的(如图4a至图4c所示的)命令格式,解码buff_fill命令。在本文的示例中,命令解码器312使用从存储器控制器326接收的指令的buff_fill命令的op码,解码buff_fill命令。命令解码器312将已解码的buff_fill命令提供给数据总线管理电路系统202b的缓存器316、门控器318和mux 320。门控器318和mux 320可以在接收已解码的buff_fill命令时禁用。命令解码器312使用操作码将buff_fill命令转换为read命令,并且将已转换的read命令提供给组/列选择逻辑部330。

66.当从命令解码器312接收read命令和从列地址电路系统310接收列地址时,组/列选择逻辑部330访问/读取感测放大器302和存储器组202a,以获得与与已接收的已识别的组id的已激活的行内的列地址相对应的列(即源位置)相关联的数据。组/列选择逻辑部330还将已取得的数据/读取的数据从源位置提供给预取缓存器及ecc 314。预取缓存器及ecc 314还可以将已接收的已取得的数据从源位置转发到缓存器316。备选地,组/列选择逻辑部330可以将已访问/读取的数据从源位置直接提供给缓存器316,如图3b所示。缓存器316可以存储从源位置访问/读取的数据而无需将数据提供给io电路系统304,这是因为门控器318在接收buff-fill命令时已禁用。

67.存储器控制器326可以对完成从源位置访问数据进行识别,并且确定已取得的数据必须写入的目的地位置。然后,存储器控制器326发起与目的地位置相对应的地址输入信号和buff_copy命令,以用于将已取得的数据写入存储器组202a的目的地位置。地址输入信号包括:与已取得的数据必须写入的的已识别的存储器组202a的组id相应的行地址和列地址(目的地位置)。存储器控制器326通过存储信道对io电路系统304发布buff_copy命令和地址输入信号。io电路系统304将地址输入信号转发到地址电路系统306并将buff_copy命令转发到命令解码器312。地址电路系统306将行地址提供给行地址电路系统308并将列地址提供给列地址电路系统310。行地址电路系统308激活与已接收的行地址相对应的行,并且启用用于已激活的行的感测放大器。列地址电路系统310将已接收的列地址转发到与已接收的组id相关联的组/列选择逻辑部330。列地址电路系统310将已接收的列地址输入到与已接收的组id相关联的组/列选择逻辑部330。

68.命令解码器312使用op码来解码buff_copy命令,并且对数据总线管理电路系统202b的缓存器316、门控器318和mux 320发布已解码的buff_copy命令。门控器318和mux 320可以响应于已接收的buff_copy命令而被启用。当接收buff_copy命令时,缓存器316通过mux 320将已存储的已访问的源位置的数据转发到组/列选择逻辑部330。

69.命令解码器312使用操作码将buff_copy命令转换为write命令,并且对组/列选择逻辑部330发布已转换的write命令。在接收数据、write命令和列地址时,组/列选择逻辑部330将与存储器组202a相关联的感测放大器302连接到数据总线管理电路系统202b的缓存器316,以将已接收的数据写入与已接收的组id的激活的行的已识别的列地址(即目的地位置)相对应的列。因此,使用存在于存储器设备202中的缓存器316执行的数据拷贝操作消除了针对通过存储信道在主机204和存储器设备202之间的数据移动的需要。

70.图3c和图3d是用于执行根据如本文所公开的实施例的存储器设备202内的数据处理操作的存储器系统200的框图。存储器设备202包括io电路系统304、地址电路系统306、行地址电路系统308、列地址电路系统310、命令解码器312、组/列选择逻辑部330、感测放大器302、存储器组202a、pim集群202c、控制寄存器332、预取缓存器及ecc 314、以及数据总线管理电路系统202b。pim集群202c包括:高速缓存328,用于存储从存储器组202a的源位置取得的数据、经处理的数据等。控制寄存器332可以包括:寄存器的集合,其可以通过预留的地址位置暴露给主机204,所述预留的地址是部署在主机204上的应用已知的。在实施例中,控制寄存器332可以具有预留的地址,所述预留的地址由主机204通过io电路系统304进行访问。控制寄存器332可以注册有通过主机204提供的已配置的细节。配置细节的示例可以是但不限于要执行的操作/处理操作、数据集合的尺寸等。基于所述配置细节,控制寄存器332可以发起由pim集群202c执行的处理操作。可以由主机204基于控制寄存器332中的轮询状态位来识别数据处理操作的完成。要注意的是,本文的实施例使用用于跟踪pim操作的控制寄存器的示例实现进行说明,但是本发明不限于此。在实施例中,pim操作的跟踪可以采用多种方式实现。数据总线管理电路系统202b包括缓存器316、门控器318和mux 320。在实施例中,缓存器316可以与预取缓存器及ecc 314和高速缓存328集成,如图3d所示。

71.主机204包括cpu 322、存储器拷贝加速器/高速缓存控制块324和存储器控制器326。存储器控制器326可以通过识别由存储器拷贝加速器/高速缓存控制块324发起的针对数据处理操作触发,执行数据处理操作。存储器控制器326识别:必须从其访问数据的源位置、和经处理的已取得的数据必须写入的目的地位置。然后,存储器控制器326发起buff_fill命令和地址输入信号,以从源位置访问数据。地址输入信号包括与必须从其访问数据的存储器组202a(源位置)的组id相对应的行地址、列地址。存储器控制器326通过存储信道对io电路系统304发布buff_fill命令。io电路系统304将buff_fill命令转发到命令解码器312并将地址输入信号转发到地址电路系统306。

72.命令解码器312解码buff_fill命令,并且将已解码的buff_fill命令提供给缓存器316、门控器318、mux 320和pim集群202c。门控器318和mux 320可以在接收buff_fill命令时被禁用。命令解码器312对控制寄存器332通过查找预留的地址空间的访问进行检测,并且将寄存器read/write命令提供给控制寄存器332,这可以在从源位置读取/访问数据并且获得操作的状态之后发起pim集群202c上的处理操作。命令解码器312将buff_fill命令转换为read命令,并且将read命令提供给与已接收的组id相关联的组/列选择逻辑部330。

73.地址电路系统306将行地址提供给行地址电路系统308,并且将列地址提供给列地址电路系统310。行地址电路系统308激活与已接收的行地址相对应的行,并且启用用于已激活的行的感测放大器。列地址电路系统310将列地址转发到与已接收的组id相关联的组/列选择逻辑部330。

74.在接收列地址和read命令时,组/列选择逻辑部330访问/读取感测放大器302和存储器组202a,以获得与已识别的组id的已激活的行内的列地址的列(源位置)相对应的数据。组/列选择逻辑部330还将已取得的数据/读取的数据从源位置提供给预取缓存器及ecc 314。预取缓存器及ecc 314还可以将已接收的已取得的数据从源位置转发到缓存器316。备选地,组/列选择逻辑部330可以将从源位置访问/读取的数据直接提供给缓存器316,如图3d所示。因为门控器318在接收buff-fill命令时已禁用,所以缓存器316可以通过防止数据流到io电路系统304来存储从源位置访问/读取的数据。缓存器316还将已取得的数据提供给pim集群202c,以处理已取得的数据。基于通过主机204的存储器控制器326利用控制寄存器332注册的配置细节,控制寄存器332可以触发要由pim集群202c执行的处理操作/pim操作。已配置的细节的示例可以是但不限于要执行的处理操作、数据集合的尺寸等。

75.pim集群202c处理从缓存器316接收的数据,其与来自io电路系统304的缓存器填充命令相对应。pim集群202c在已定义的区域中使用从主机204接收的计算数据处理数据。pim集群202c可以将经处理的数据存储在与pim集群202c相关联的高速缓存328中。此外,控制寄存器332可以获得数据的处理完成的状态并且更新其状态位。在实施例中,pim集群202c可以在数据处理完成时更新控制寄存器332。为了简化附图,在附图上没有明确画出用于在控制寄存器332和pim集群202c之间进行更新的信号路径。

76.存储器控制器326可以通过轮询控制寄存器332中的状态位,确定由pim集群202c执行的处理操作的完成。在确定处理操作完成时,存储器控制器326发起buff_copy命令和与目的地位置相对应的地址输入信号,以将经处理的数据写入已识别的存储器组202a的目的地位置。地址输入信号包括:与已取得的数据必须写入的(目的地位置)的已识别的存储器组202a的组id相应的行地址和列地址。存储器控制器326通过存储信道对io电路系统304发布buff_copy命令和地址输入信号。io电路系统304将地址输入信号转发到地址电路系统306并将缓存器拷贝命令转发到命令解码器312。地址电路系统306将行地址提供给行地址电路系统308,并将列地址提供给列地址电路系统310。行地址电路系统308激活与已接收的行地址相对应的行,并且启用感测放大器以连接到已激活的行。列地址电路系统310将已接收的列地址输入到与已接收的组id相关联的组/列选择逻辑部330。

77.命令解码器312使用操作码解码buff_copy命令,并且对数据总线管理电路系统202b的缓存器316、门控器318和mux 320发布已解码的buff_copy命令。门控器318和mux 320可以响应于已接收的buff_copy命令而被启用。当接收buff_copy命令时,缓存器316从pim集群202c接收经处理的数据。mux 320从缓存器316中选择已接收的经处理的数据,并且将经处理的数据提供给组/列选择逻辑部330。命令解码器312使用操作码将buff_copy命令转换为write命令,并且对与已接收的组id相关联的组/列选择逻辑部330发布已转换的write命令。

78.在接收经处理的数据、write命令和列地址时,组/列选择逻辑部330将与存储器组202a相关联的感测放大器302连接到数据总线管理电路系统202b的缓存器316,以将已接收的数据写入与已接收的已识别的组id的已激活的行内的列地址(即目的地位置)相对应的列。因此,使用存在于存储器设备202中的缓存器316执行的数据处理操作消除了针对通过存储信道的数据移动的需要。

79.图2a-图3d示出存储器系统200的示例框,但是应当理解,其他示例实施例不限于

此。在其他实施例中,存储器系统200可以包括更少或更多数量的功能框。此外,框的标签或名称仅用于说明目的,并不限制本文的实施例的范围。一个或多个框可以被组合在一起,以执行存储器系统200中的相同或实质上类似的功能。

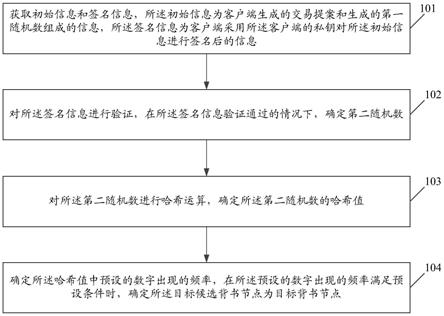

80.图4a-图4c是描绘根据如本文所公开的实施例的数据初始化操作的示例图。在实施例中,主机204的存储器控制器326分别利用读地址和写地址初始化缓存器316和存储器组202a的目的地位置。读地址和写地址与源位置和目的地位置相对应。在实施例中,读地址和写地址可以是连续地址、散布的地址、要读取或写入的数据的已知模式相关联的地址等中的至少一种。存储器控制器326利用读地址使用buff_fill命令初始化缓存器316,以使缓存器316可以存储关于初始化读地址的已取得的数据/读取的数据。存储器控制器326利用写地址使用buff_copy命令初始化存储器组202a的目的地位置,以使缓存器316可以将已取得的数据传输到利用写地址初始化的目的地位置。

81.在实施例中,存储器控制器326利用连续的物理地址初始化缓存器316和希望的存储器组202a中的位置。物理地址可以包括与源位置相对应的读地址和与目的地位置相对应的写地址,它们可以由存储器控制器326提供。存储器控制器326利用连续读地址(例如,ra1,ra1 1,ra 2

…

ra1 n)以顺序方式对缓存器316发布buff_fill命令(例如,r0,r1

…

rn),以初始化缓存器316的位置。存储器控制器326还启用缓存器316,以将从与buff_fill命令相对应的存储器组202a的源位置取得的数据(例如,data0,data1,

…

datan)存储到利用连续读地址以顺序方式初始化的位置中。

82.存储器控制器326利用连续写地址(例如,wa1,wa1 1

…

wa1 n)以顺序方式发布针对希望的存储器组202a中的目的地位置的buff_copy命令(例如,w0,w1,w2,

…

wn)。存储器控制器326还启用缓存器316,以将已存储的已取得的数据传输到希望的存储器组202a的目的地位置,所述目的地位置利用连续写地址以顺序方式初始化。在实施例中,写地址可以基于读地址的顺序发布。因为将读地址和写地址的顺序分配/映射为相同,所以最先获取到/存储在缓存器316中的已取得的数据,可以最先输出/传输到希望的存储器组202a的目的地位置。在实施例中,缓存器316可以是先进先出(fifo)缓存器。本发明不限于此。在实施例中,缓存器316可以是后进先出(lifo)缓存器。

83.例如,从与buff_fill命令r0和r1相对应的存储器组202a的源位置取得的数据data0和data1可以分别存储在缓存器316的关于已初始化的连续读地址ra1和ra1 1所初始化的位置。此外,当接收缓存器拷贝命令w0和w1时,从缓存器316取得的数据data0和data1可以传输到分别利用连续写地址wa1和wa1 1初始化的存储器组202a的目的地位置,其中,写地址的顺序必须与读地址的顺序相同。因此,最先获取的(存储的)已取得的数据data0可以是最先从缓存器316中输出,以写入存储器组202a的目的地位置。

84.在实施例中,存储器控制器326利用散布的物理地址初始化缓存器316和希望的存储器组202a的目的地位置。物理地址可以包括与源位置相对应的读地址和与目的地位置相对应的写地址,它们可以由存储器控制器326提供。存储器控制器326利用散布的读地址(例如,ra1,ra1 1,ra 2

…

ra1 n)以顺序方式对缓存器316发布buff fill命令(例如,ra0,ra1,

…

ran),以初始化缓存器316的位置。存储器控制器326然后启用缓存器316,以将从与buff_fill命令相对应的存储器组202a的源位置取得的数据(例如,data0,data1,

…

datan)存储到利用散布的读地址以顺序方式初始化的位置中。

85.存储器控制器326利用散布的写地址(例如,w0,w1,w2,

…

wn)以顺序方式发布针对希望的存储器组202a中的目的地位置的buff_copy命令(例如,w0,w1,w2,

…

wn)。存储器控制器326还启用缓存器316,以将已存储的已取得的数据传输到希望的存储器组202a的目的地位置,所述目的地位置利用散布的地址以顺序方式初始化。在实施例中,可以与读地址的顺序无关地发布写地址。然而,存储器组202a中的数据必须以已读取/已取得的数据的顺序存储。

86.考虑示例场景,其中,存储器控制器326启用缓存器316,以将从存储器组202a的源位置取得的数据data0、data1和data2存储在利用散布的读地址/连续读地址ra0、ra1和ra2初始化的位置中。存储器控制器326还可以启用缓存器316,以在data0之前将data1和data2传输到希望的存储器组202a的目的地位置。然而,数据必须基于已取得的数据/读取的数据的顺序被存储希望的存储器组202a的目的地位置中,即data1必须被存储在利用wa1分配的希望的存储器组202a的目的地位置中,并且data2必须被存储在利用wa2分配的希望的存储器组202a的目的地位置中。而且,存储器控制器326可以跳过data0。存储器控制器326可以提供伪buff_copy命令,以丢弃data0,或到达出现数据移动或数据转动的缓存器的末尾。存储器控制器326还可以启用缓存器316,从而甚至是在传输data1和data2之后,将传输data0传输到希望的存储器组202a的目的地位置,所述目的地位置利用散布的已写入的地址wa0初始化。已写入的数据的顺序应该保持为data0~datan(直到缓存器的末尾)。否则,数据可以四处滚动,并且数据可以指向用于的下一buff_copy操作的data0。

87.在实施例中,存储器控制器326可以利用已知格式来初始化缓存器316/希望的存储器组202a的目的地位置。如图4c所示,存储器控制器326使用正常write命令将已知模式(例如,pattern 0,pattern 1,

…

pattern n)写入存储器组202a。在实施例中,已知模式可以是数据,例如,“1”、“0”等。此后,存储器控制器326对缓存器316发布buff_fill命令(例如,ra0,ra1,

…

ran),以利用存储在存储器组202a中的已知模式初始化缓存器316的位置。存储器控制器326然后启用缓存器316,以将从与buff_fill命令相对应的存储器组202a的源位置取得的数据(例如,data0,data1,

…

datan)存储到利用连续已知模式以顺序方式初始化的位置中。此外,存储在缓存器316中的数据可以转动或移动以及在指向datan之后指向data0。

88.存储器控制器326利用已知格式以顺序方式发布针对希望的存储器组202a的目的地位置的buff_copy命令(例如,w0,w1,w2,

…

wn)。因此,缓存器316可以将已存储的已取得的数据传输到希望的存储器组202a的目的地位置,所述目的地位置利用已知格式以顺序方式初始化。在实施例中,存储器控制器326可以对存储器组202a发布buff_copy命令,用于利用已知模式初始化多个位置。

89.图5是根据如本文所公开的实施例的描绘buff_fiill命令、buff_copy命令、正常read命令和正常write命令的示例命令格式的表。本文的实施例启用存储器控制器326,以通过基于针对读操作和写操作所确定的源位置和目的地位置执行编码,发起buff_fill命令和buff_copy命令。在图5中示出了buff_fill和buff_copy命令的示例命令格式。本发明不限于此。在实施例中,buff_fill命令和buff_copy命令可以包括其他类型的命令格式。

90.buff_fill命令、buff_copy命令、正常read命令和正常write命令的命令格式可以包括与例如但不限于以下功能相对应的字段/op码:时钟启用(cke)、片选(cs_n)、激活命令

输入(act_n)、命令输入(ras_n,cas_n和we_n)和地址输入a11。对于cke、cs_n和we_n,buff_fill命令、buff_copy命令、正常read命令和正常write命令的op码可以相同。cke可以注册为cke高(

‘

h’)和cke低(

‘

l’)。cke高(

‘

h’)激活,并且cke低(

‘

l’)去激活,内部时钟信号和设备输入缓存器和输出驱动器。在读操作和写操作中,cke必须注册为高。cs_n可以设置用于外部存储器组/排选择,并且当cs_n被注册为高时,所有命令都可以被屏蔽。act_n定义与cs_n一起输入的激活命令。当act_n注册为高时,命令输入(ras_n,cas_n和we_n)充当用于读、写或其他类型的操作的命令。

91.buff_fill命令和buff_copy命令以及正常的read命令和write命令的op码可以针对命令输入(ras_n和cas_n)变化。在本文的示例中,命令解码器312可以基于命令输入(ras_n和cas_n)的op码来区分buff_fill命令和buff_copy命令与正常的read命令和write命令。在正常的read命令和write命令的情况下,针对ras_n、cas_n的op码可以分别是

‘

h’和

‘

l’。在buff_fill命令和buff_copy命令的情况下,针对ras_n、cas_n的op码可以分别是

‘

l’和

‘

h’。在正常read命令、buff_fill命令和buff_copy命令的情况下,针对we_n的op码可以是

‘

h’。在正常write命令的情况下,针对we_n的op码可以是

‘

l’。

92.针对a11,buff_fill命令、buff_copy命令、正常read命令和正常write命令的op码也可以不同。针对a11,buff_fill命令的op码可以是高(

‘

h’)。针对a11,buff_fill命令的op码可以是low(

‘

l’)。针对a11,正常read命令和正常write命令的op码可以是有效(

‘v’

)。

93.在本文的示例中,存储器设备202的命令解码器312可以基于a11的op码,识别buff_fill命令和buff_copy命令中的每一个。

94.图6是描绘根据如本文所公开的实施例的用于执行存储设备202内的数据操作的方法的流程图600。在步骤602处,该方法包括:由主机204检测已发起的用于对由至少一个应用所需要的数据执行存储器设备202内的至少一个操作的至少一个触发。所述操作包括数据拷贝操作、数据处理操作和数据初始化操作中的至少一种。

95.在步骤604处,该方法包括:由主机204通过使用至少一个buff_fill命令和至少一个buff_copy命令、实现存储器设备202的数据总线管理电路系统202b和其至少一个组之间的数据的移动而无需与主机204交换数据,执行已触发的存储器设备202内的至少一个操作。可以按照所呈现的顺序、按照不同顺序或同时地执行该方法和流程图600中的各种动作、行为、框、步骤等。此外,在一些实施例中,在不脱离本公开的范围的情况下,一些动作、行为、框、步骤等可以在不脱离本发明的范围的情况下被省略、添加、修改、跳过等。

96.图7是描绘根据如本文所公开的实施例的用于执行存储设备202内的数据拷贝操作的方法的流程图700。

97.在步骤702处,该方法包括:当检测到由至少一个应用发起的针对数据拷贝操作的触发时,由主机204对存储器设备202发布至少一个buff_fill命令和至少一个源位置。在实施例中,主机204可以基于与至少一个应用相关联的源位置和目的地位置,检测触发。源位置和目的地位置可以分别包括同一存储器设备202的相同的组或不同的组内的源地址和目的地址。例如,当存储器设备202设置为多个时,当数据拷贝操作要在多个存储器设备202中的一个中执行时,可以发起触发。

98.在步骤704处,该方法包括:当从主机204接收到至少一个buff_fill命令和至少一个源位置时,由存储器设备202从至少一个源位置读取数据,并且将读取的数据存储在数据

总线管理电路系统202b的缓存器316中。缓存器316可以使用门控器318防止读取到主机204的流来存储数据,门控器318在接收buff_fill命令时已被禁用。

99.在步骤706处,该方法包括:由主机204通过跟踪用于执行读取操作所需要的时间来检测读取数据的完成。在步骤708处,该方法包括:当检测到读取数据完成时,由主机204对存储器设备202发布至少一个buff_copy命令和至少一个目的地位置。

100.在步骤710处,该方法包括:当从主机204接收到至少一个buff_copy命令时,由存储器设备202将读取的数据写入至少一个目的地位置。存储器设备202使用mux 320将存储在缓存器316中的读取的数据传输到至少一个目的地位置。在步骤712处,该方法包括:由主机204通过跟踪用于执行写操作所需要的时间来检测写数据的完成。可以按照所呈现的顺序、按照不同顺序或同时地执行该方法和流程图700中的各种动作、行为、框、步骤等。此外,在一些实施例中,在不脱离本公开的范围的情况下,一些动作、行为、框、步骤等可以在不脱离本发明的范围的情况下被省略、添加、修改、跳过等。

101.图8是描绘根据如本文所公开的实施例的用于执行存储设备202内的数据处理操作的方法的流程图800。

102.在步骤802处,该方法包括:当检测到由至少一个应用发起的针对数据处理操作的触发时,由主机204对存储器设备202发布至少一个buff_fill命令和至少一个源位置。在实施例中,主机204可以基于与至少一个应用相关联的源位置和目的地位置,检测触发。源位置和目的地位置可以分别包括同一存储器设备202的相同的组或同一存储器设备202的不同的组内的源地址和目的地址。例如,当存储器设备202设置为多个时,当数据处理操作要在多个存储器设备202中的一个中执行时,可以发起触发。

103.在步骤804处,该方法包括:当从主机204接收到至少一个buff_fill命令和至少一个源位置时,由存储器设备202从至少一个源位置读取数据;将读取的数据存储在缓存器316中;以及,使用控制寄存器332启用pim集群202c,以从缓存器316接收读取的数据,并且处理读取的数据。

104.在步骤806处,该方法包括:由主机204使用存储器设备202的控制寄存器332,检测读取的数据的处理的完成。在步骤808处,该方法包括:当检测到读取的数据的处理完成时,由主机204对存储器设备202发布至少一个buff_copy命令和至少一个目的地位置。

105.在步骤810处,该方法包括:当从主机204接收到至少一个buff_copy命令和至少一个目的地位置时,由存储器设备202将经处理的读取的数据从pim集群202c传输到缓存器316,并且将经处理的读取的数据从缓存器316传输到至少一个目的地位置。在步骤812处,该方法包括:由主机204通过跟踪用于执行写操作所需要的时间来检测写数据的完成。可以按照所呈现的顺序、按照不同顺序或同时地执行该方法和流程图800中的各种动作、行为、框、步骤等。此外,在一些实施例中,在不脱离本公开的范围的情况下,一些动作、行为、框、步骤等可以在不脱离本发明的范围的情况下被省略、添加、修改、跳过等。

106.图9是描绘根据如本文所公开的实施例的用于执行数据初始化操作的方法的流程图900。

107.在步骤902处:该方法包括:通过利用读取的数据/由已读取的地址指向的内容对缓存器316发布至少一个buff_fill命令,由主机204利用至少一个读地址对缓存器316进行初始化。因此,读取的数据/由已读取的地址指向的内容被存储在关于已初始化的至少一个

读地址的缓存器316中。读地址与源位置相对应。

108.在步骤904处,该方法包括:通过利用缓存器316的已初始化的内容/读取数据对存储器设备202发布至少一个buff_copy命令,由主机204利用至少一个写地址对存储器设备202的至少一个目的地位置进行初始化。因此,来自缓存器316的所存储的读取的数据传输到利用至少一个写地址初始化的存储器设备202的至少一个目的地位置。所述至少一个读地址和所述至少一个写地址包括对应的连续的读地址和写地址、对应的散布的读地址和写地址、以及数据的已知模式中的至少一种。在步骤906处,该方法包括:通过发布一个或多个buff_fill命令,由主机204迭代地对存储器设备的一个或多个目的地位置进行初始化,直到存储器设备的所有所需要的位置利用缓存器的已初始化的内容完全初始化为止。可以按照所呈现的顺序、按照不同顺序或同时地执行该方法和流程图900中的各种动作、行为、框、步骤等。此外,在一些实施例中,在不脱离本公开的范围的情况下,一些动作、行为、框、步骤等可以在不脱离本发明的范围的情况下被省略、添加、修改、跳过等。

109.图10a和图10b是描绘根据如本文所公开的实施例的利用计算数据初始化pim集群202c以及使用已初始化的计算数据处理pim集群202c上的数据的示例序列图。

110.在步骤1001处,通过使用正常的read命令和write命令执行读操作和写操作,主机204在存储器设备202的存储器组202a上加载/初始化数据。在步骤1002处,通过使用正常write命令来执行写操作,主机204在存储器设备202的存储器组202a中的指定命令区域上加载pim命令。pim命令可以是pim集群202c的功能命令。pim命令可以基于pim集群202c的功能而变化。指定的命令区域可以是存储器设备202的存储器组202a中为了存储pim命令所定义的区域。区域的地址可以在控制寄存器中定义,以及基于pim集群202c的规范而变化。

111.当在存储器组202a中的指定的命令区域上初始化pim命令时,主机204发起pim命令初始化/加载阶段。在pim命令初始化阶段期间,在步骤1003处,主机204通过控制寄存器为pim集群202c配置以pim命令阶段。在步骤1004处,被配置以pim命令阶段的pim集群202c等待pim命令到达缓存器316。

112.在步骤1005处,主机204通过存储器控制器326对命令解码器312发布buff_fill命令,以将pim命令从存储器组202a中的指定的命令区域加载到缓存器316。在步骤1006处,命令解码器312还将buff_fill命令转换为正常read命令,并且将正常read命令提供给存储器组202a。

113.在步骤1007处,数据总线管理(dbm)电路系统202b从存储器组202a中的指定的命令区域接收pim命令,并且将从存储器组202接收的pim命令输入到缓存器316。在步骤1008处,主机204重复步骤1005、1006和1007,直到用于pim操作/处理操作的所有所需要的pim命令都已输入到缓存器316为止。在步骤1009处,由于pim命令已经输入到缓存器316,因此pim集群202c从缓存器316访问pim命令,并且将pim命令存储在内部高速缓存328中。

114.当利用pim命令初始化pim集群202c时,主机204发起pim数据加载阶段。在pim数据加载阶段期间,主机204可以利用计算数据初始化pim集群202c,并且启用pim集群202c,以从缓存器316接收用于进行处理的数据。在步骤1010处,主机204;通过控制寄存器为配置pim集群202c配置以pim数据阶段。在pim数据阶段中,pim集群202c可以加载有从存储器组202a的存储器组访问的用于进行处理的数据。在步骤1011处,被配置以pim数据阶段的pim集群202c等待数据到达缓存器316。

115.在步骤1012处,主机204通过存储器控制器326对命令解码器312发布buff_fill命令,以将数据加载到缓存器316。在步骤1013处,命令解码器312将已接收的buff_fill命令提供给数据总线管理电路系统202b。命令解码器312还将buff_fill命令转换为正常read命令,并且将正常read命令提供给存储器组202a。

116.在步骤1014处,数据总线管理电路系统202b从存储器组202a接收数据并将数据输入到缓存器316。在步骤1015处,主机204重复步骤1012、1013和1014,直到所需要的数据已输入到缓存器316为止。在步骤1016处,随着缓存器316从存储器组202a接收数据,pim集群202c将数据从缓存器316移动到内部高速缓存328。

117.当利用数据对pim集群202c进行初始化时,在步骤1017处,主机204通过控制寄存器触发pim集群202c上的处理操作。在步骤1018处,pim集群202c发起对已接收的数据的处理。

118.在对已接收的数据进行处理时,在步骤1019处,pim集群202c完成数据的处理,并且在控制寄存器中对处理的状态和处理的结果的尺寸进行更新。在步骤1020处,pim集群202c将结果的初始部分提供给缓存器316。

119.在步骤1021处,主机204轮询控制寄存器以获得处理的状态。一旦处理完成,在步骤1022处,主机204就通过存储器控制器326将buff_copy命令发送给命令解码器312。在步骤1023处,命令解码器312将buff_copy命令转换为正常write命令,并且将正常write命令提供给存储器组202a。在步骤1024处,数据总线管理电路系统202b将数据(即经处理的数据)从缓存器316提供给存储器组202a。

120.在步骤1025处,主机204重复步骤1022、1023和1024,并且pim集群202c继续提供缓存器316中的处理的结果,直到处理的所有结果已移动到存储器组202a为止。

121.图11是描绘根据如本文所公开的实施例的在存储器模块级执行的数据拷贝操作的示例图。在存储器模块中,多个存储器设备202以多排结构布置。每一排包括多个存储器设备202,每个存储器设备具有多个存储器组202a。在这种情况下,通过将存储器设备的至少一排(例如,排0)当作用于数据移动的缓存器316,主机204可以执行存储器模块104内的数据拷贝操作。在数据拷贝操作期间,通过根据正在进行的数据拷贝操作来管理数据业务,主机204也可以访问其他排(例如,排1)的存储器组,由此提高了存储器系统200的吞吐量和性能。

122.本文的实施例启用存储器中数据操作而无需涉及通过存储信道的数据移动,其中,所述数据操作包括数据拷贝操作、数据处理操作和数据初始化操作。

123.本文的实施例实现了存储器设备内的用于执行数据拷贝操作的缓存器、以及存储器设备内的用于执行数据处理操作的实时处理存储器(pim)集群。

124.本文的实施例实现了存储器设备内的任意位置之间的数据拷贝、存储器设备的存储器组和实时处理存储器(pim)(例如,hbm的缓存器管芯上的pim)之间的内部数据移动、存储器设备内的处理区域和存储器组之间的存储器中的数据传输、以及通过利用预定模式预先加载缓存器的存储器初始化。

125.本文的实施例还使用用于执行数据操作的缓存器填充(buff_fill)命令和缓存器拷贝(buff_copy)命令,其导致了针对所有存储器中的数据拷贝的更好的能力,这是由于在存储器设备上可以没有dq线上的自锁(toggling),并且提高了即使是在字节级别的粒度上

拷贝数据的灵活性。

126.即使在buff_copy操作期间,本文的实施例也提供了通过利用由主机204驱动的数据掩蔽来拷贝即使是信息的一个字节的灵活性。因此,可以仅将所需要的字节拷贝到由主机指示的存储器设备的目的地位置。

127.可以通过在至少一个硬件设备上运行并执行网络管理功能以控制各元件的至少一个软件程序来实现本文公开的实施例。图2a-图8所示的元件可以是硬件设备或硬件设备与软件模块的组合中的至少一种。

128.本文公开的实施例描述了用于执行存储器设备内的数据操作的方法及系统。因此,应该理解,保护范围扩展到这样的程序,并且除了其中具有消息的计算机可读模块之外,这种计算机可读存储模块包含:用于当程序在服务器或移动设备或任何合适的可编程设备上运行时实现该方法的一个或多个步骤的程序代码模块。该方法在优选实施例中通过用例如超高速集成电路硬件描述语言(vhdl)、另一种编程语言编写的软件程序实现或者与该软件程序一起实现,或该方法由在至少一个硬件设备上执行的一个或多个vhdl或若干软件模块来实现。硬件设备可以是可以被编程的任何类型的便携式设备。该设备还可以包括以下模块,该模块可以是例如,硬件模块(例如,asic)、或硬件和软件模块的组合(例如,asic和fpga、或至少一个微处理器和具有位于其中的软件模块的至少一个存储器)。本文描述的方法实施例可以部分地以硬件实现且部分地以软件实现。备选地,本发明可以在不同的硬件设备上实现(例如,使用多个cpu)。

129.以上对具体实施例的描述充分揭示了本文中的实施例的一般性质,从而其他技术人员通过应用现有知识,能够在不背离总体构思的前提下,容易地对这些具体实施例进行修改和/或针对各种应用进行调整,因此这种调整和修改应该且意图被包括在所公开的实施例的等同物的意义和范围内。可以理解,本文使用的短语或术语用于描述目的而不是限制性的。因此,尽管已经根据实施例描述了本文的实施例,但是本领域技术人员将认识到,可以在如本文所述的实施例的精神和范围内通过修改来实践本文的实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。