1.本发明涉及半导体技术领域,更具体地,涉及一种半导体结构及其形成方法。

背景技术:

2.在现有混合接合(hybrid bonding)制程中,在执行cmp工艺时,因为有两种以上的材料,所以在i/o之间的节距(pitch)均匀度不佳的情况下会在混合接合的接合界面处发生腐蚀(erosion)。如图1所示,区域a中的i/o 12的均匀度与区域a2中的i/o 12的均匀度不同,因此在i/o 12的顶面(接合界面)处发生较浅的腐蚀e1和较深的腐蚀e2。若存在这样的腐蚀(erosion),则会影响后续进行混合接合时的电性连接。

技术实现要素:

3.针对相关技术中的上述问题,本发明提出一种半导体结构及其形成方法,能够解决现有混合接合的接合界面处的腐蚀问题。

4.本发明的实施例提供了一种半导体结构,包括:线路(rdl)层;导电连接件,位于线路层上并且连接至线路层中的线路;伪焊盘,位于线路层上方并且与线路层间隔开,其中,伪焊盘和导电连接件中的每相邻两个之间的节距相同。

5.在上述半导体结构中,伪焊盘的宽度小于导电连接件的宽度。

6.在上述半导体结构中,导电连接件和伪焊盘中每个的高度与宽度相关联。

7.在上述半导体结构中,导电连接件的顶面和伪焊盘的顶面共面。

8.在上述半导体结构中,还包括电连接至导电连接件的管芯。

9.在上述半导体结构中,还包括与导电连接件接合的第二导电连接件,管芯通过导电连接件和第二导电连接件电连接线路层。

10.在上述半导体结构中,还包括与伪焊盘接合的第二伪焊盘。

11.在上述半导体结构中,还包括第二线路层,位于管芯与第二导电连接件之间,其中,第二伪焊盘与第二线路层间隔开。

12.在上述半导体结构中,管芯包括两个管芯,其中,伪焊盘设置在两个管芯之间。

13.在上述半导体结构中,伪焊盘与导电连接件的材料相同。

14.本发明的实施例还提供了一种形成半导体结构的方法,包括:形成位于介电材料中的线路(rdl)层;在介电材料中形成暴露线路层中的线路的第一开口和宽度小于第一开口的第二开口,第二开口的深度小于第一开口的深度;在第一开口和第二开口中形成导电材料,以形成位于第一开口内的导电连接件和位于第二开口内的伪焊盘。

15.在上述方法中,在形成导电材料之后还包括:执行平坦化操作以使第一开口和第二开口中的导电材料的顶面齐平。

16.在上述方法中,第一开口和第二开口中的每相邻两个之间的节距相同。

17.在上述方法中,第一开口和第二开口中每个的高度与宽度相关联。

18.在上述方法中,还包括在介电材料上方形成电连接至导电连接件的管芯。

19.在上述方法中,管芯通过导电连接件和第二导电连接件电连接线路层。

20.在上述方法中,伪焊盘与第二伪焊盘接合。

21.在上述方法中,第二线路层位于管芯与第二导电连接件之间,其中,第二伪焊盘与第二线路层间隔开。

22.在上述方法中,形成管芯包括形成两个管芯,其中,伪焊盘还设置在两个管芯之间。

23.在上述方法中,形成第一开口和第二开口包括:通过图案化的掩模来蚀刻介电材料,图案化的掩模具有宽度不同的多个开口。

附图说明

24.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应当注意,根据工业中的标准实践,各个部件并非按比例绘制。事实上,为了清楚讨论,各个部件的尺寸可以任意增大或减小。

25.图1是现有混合接合的接合界面处发生腐蚀的示意图。

26.图2a是根据本发明实施例的半导体结构的示意图。

27.图2b是根据本发明实施例的半导体结构的俯视示意图。

28.图3a和图3b分别是根据不同本发明实施例的伪焊盘和导电连接件的布局配置的俯视示意图。

29.图4a和图4b分别示出了伪焊盘和导电连接件的电性模拟效果的示意图。

30.图5a至图5t是根据本发明实施例的形成半导体结构的流程的多个阶段的示意图。

具体实施例

31.下列公开提供了许多用于实现所提供主题的不同特征的不同实施例或实例。下面将描述元件和布置的特定实例以简化本发明。当然这些仅仅是实例并不旨在限定本发明。例如,在以下描述中,在第二部件上方或上形成第一部件可以包括第一部件和第二部件直接接触的实施例,也可以包括在第一部件和第二部件之间形成额外的部件使得第一部件和第二部件可以不直接接触的实施例。而且,本发明在各个实例中可重复参考数字和/或字母。这种重复仅是为了简明和清楚,其自身并不表示所论述的各个实施例和/或配置之间的关系。

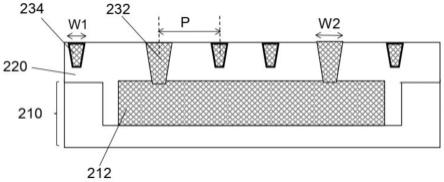

32.图2a是根据本发明实施例的半导体结构的示意图。如图2a所示,设置有线路层210。线路层210可以包括设置在介电层220中的线路212。在一些实施例中,线路层210可以是重布线(rdl)层。多个导电连接件232设置在所述线路层210上方并且电连接至所述线路层210中的线路212。图2a中所示的导电连接件232的数量仅是示例。导电连接件232可以作为i/o部件。导电连接件232位于介电层220中。在一些实施例中,多个导电连接件232之间的节距p是不均匀的,其中,节距p是指两个导电连接件232的中心线之间的距离。根据本发明的实施例,介电层220中还设置有多个伪焊盘234,伪焊盘234位于所述线路层210上方。伪焊盘234与所述线路层210间隔开而与线路层210电隔离。所述伪焊盘234与所述导电连接件232的材料可以相同,例如是诸如金属的导电材料。

33.图2b是根据本发明实施例的半导体结构的俯视示意图。结合图2a和图2b所示,所

述伪焊盘234和所述导电连接件232中的每相邻两个之间的节距是相同的。图3a和图3b分别是根据不同本发明实施例的伪焊盘和导电连接件的布局配置的俯视示意图。在图3a中,一个导电连接件232由四个伪焊盘234围绕。在图3b中,一个伪焊盘234由四个导电连接件232围绕。应理解,只要相邻的伪焊盘234和导电连接件232之间的节距相同,可以对伪焊盘234和导电连接件232的布局进行任何适当的配置。由于设置了伪焊盘234,并且使伪焊盘234与导电连接件232的总体中的任意两个之间的节距是相同的,因此可解決在现有混合接合的接合界面处发生的腐蚀问题。

34.虽然图2a至图3b中示出了在俯视图中导电连接件232和伪焊盘234为圆形,但是导电连接件232和伪焊盘234也可以是其他形状,例如正方形、长方形等。

35.在一些实施例中,可以通过利用掩模的蚀刻工艺来形成用于伪焊盘和导电连接件的多个开孔。由于蚀刻的负载效应(loading effect),利用掩模所定义出来的开孔宽度(即开孔直径)越小,则对应蚀刻后的开孔深度(高度)越浅。从而所述导电连接件232和所述伪焊盘234中每个的深度与宽度相关联,例如深度越小则宽度越小。因此,可以同时进行形成伪焊盘234和导电连接件232的操作工艺,可以利用宽度较小的开孔创建出不连接至线路层210的伪焊盘234。在一些实施例中,所述伪焊盘234的宽度小于所述导电连接件232的宽度。所述伪焊盘234的深度小于所述导电连接件232的深度。

36.再次参考图2a所示,示出了导电连接件232的宽度w2、伪焊盘234的宽度w1、以及导电连接件232与伪焊盘234之间的节距p。在一些示例中,伪焊盘234的宽度w1、导电连接件232的宽度w2、和节距p的尺寸配置可以如下表1所示。

37.表1

[0038] 数值范围(微米)w23微米至30微米w1b<a-2微米pc>a(1-10)

[0039]

所述导电连接件232的顶面可以是与其他导电连接件进行接合的接合界面。所述导电连接件232的顶面和所述伪焊盘234的顶面共面。图4a和图4b分别示出了伪焊盘和导电连接件的电性模拟效果的示意图。伪焊盘234设置在两个导电连接件232之间。在图4a中,伪焊盘234与下面的线路层210之间的间隔的高度h1为0.1微米。在图4b中,伪焊盘234与下面的线路层210之间的间隔的高度h2为0.9微米。图4a与图4b中的其他方面类似。图4a中的模拟电阻结果为26.243mω,图4b中的模拟电阻结果为26.233mω。由此可知,伪焊盘234与线路层之间的间隔高度(或可以称为伪焊盘234的深浅)不影响线路之间的阻抗值,即,伪焊盘234与线路层之间的耦合电容效应并不显著。也就是说,在接合界面处设置伪焊盘234不影响线路之间的阻抗值。

[0040]

根据本发明的实施例,还提供了形成半导体结构的方法。图5a至图5t是根据本发明实施例的形成半导体结构的流程的多个阶段的示意图。

[0041]

首先,如图5a所示,提供第一介电层510以及在第一介电层510中的互连件512。互连件512的顶面由第一介电层510暴露。第二介电层520覆盖在第一介电层510和互连件512上方。

[0042]

如图5b所示,在第二介电层520的上方形成图案化的第一掩模层532。第一掩模层

532的材料可以是光刻胶。图案化的第一掩模层532中具有第一掩模开口531,第一掩模开口531至少部分地位于互连件512的上方。然后如图5c所示,利用图案化的第一掩模层532蚀刻下方的第二介电层520,以在第二介电层520中形成位于互连件512上方的凹部521。

[0043]

如图5d所示,去除图案化的第一掩模层532,并在第二介电层520上形成图案化的第二掩模层535。图案化的第二掩模层535的材料可以是光刻胶。图案化的第二掩模层535中具有第二掩模开口536,第二掩模开口536位于凹部521内且位于互连件512上方。如图5e所示,利用图案化的第二掩模层535蚀刻下方的第二介电层520,从而在第二介电层520中形成暴露互连件512的顶面的第一开孔523。

[0044]

然后,去除图案化的第二掩模层535,并在第二介电层520上和第一开孔523内共形地覆盖第一晶种层541,如图5f所示。如图5g所示,例如通过电镀工艺,在第一晶种层541上形成第一导电材料542。随后,如图5h所示,执行平坦化操作以使第一晶种层541和第一导电材料542的顶面与第二介电层520的顶面齐平。这样,第一晶种层541和第一导电材料542形成了位于第二介电层520中的线路层210和连接在线路层210。

[0045]

如图5i所示,在第二介电层520上方沉额外的介电材料。在一些实施例中,额外的介电材料可以与第二介电层520的材料相同。从而,增加了第二介电层520的厚度且使得第二介电层520覆盖线路层210。

[0046]

如图5j所示,在第二介电层520上形成图案化的第三掩模层537。图案化的第三掩模层537的材料可以是光刻胶。图案化的第三掩模层537中具有多个第三掩模开口538。多个第三掩模开口538中的一部分位于线路层210的上方。多个第三掩模开口538中的另一部分位于不具有线路层210的第二介电层520的上方。多个第三掩模开口538可以具有不同的宽度。如上所述,掩模所定义出来的开孔宽度(即开孔直径)越小,则对应蚀刻后的开孔高度越浅。因此,随后用于形成伪焊盘的第三掩模开口538可以具有较小的宽度ds,而随后用于形成导电连接件的第三掩模开口538可以具有较大的宽度dg。多个第三掩模开口538之间的节距相同。

[0047]

如图5k所示,利用图案化的第三掩模层537蚀刻第二介电层520,而去除未被图案化的第三掩模层537覆盖的第二介电层520。具有较大宽度的第三掩模开口538在第二介电层520中形成第一开口528,具有较小宽度的第三掩模开口538在第二介电层520中形成第二开口529。第一开口528的宽度大于第二开口529的宽度。第二开口529的深度小于第二开口529的深度。第一开口528暴露线路层210的顶面。第一开口528随后用于形成导电连接件,第二开口529随后用于形成伪焊盘。第一开口528和第二开口529中的每相邻两个的节距相同。

[0048]

如图5l所示,去除图案化的第三掩模层537。然后,如图5m所示,在第二介电层520上、第一开口528和第二开口529内覆盖第二晶种层544,在第二晶种层544上形成填充过第一开口528和第二开口529的第二导电材料545。如图5n所示,执行平坦化操作以使得第二晶种层544和第二导电材料545的顶面与第二介电层520的顶面齐平,以形成位于所述第一开口528内的导电连接件232和位于所述第二开口529内的伪焊盘234。

[0049]

如图5o所示,提供要连接至导电连接件232的管芯550。其中,管芯550可以形成在第二线路层280上并与第二线路层280中的线路电连接。第二线路层280下方也可以设置有第二伪焊盘274和第二导电连接件272。第二伪焊盘274与第二线路层280分离并且电隔离。第二导电连接件272连接在线路层210下方。形成第二伪焊盘274和第二导电连接件272的过

程可以与形成伪焊盘234和导电连接件232的过程类似,因此省略其详细描述。将伪焊盘234与第二伪焊盘274混合接合,将导电连接件232与第二导电连接件272混合接合,以接合至管芯550。由于设置了伪焊盘234,并且使伪焊盘234与导电连接件232中的任意两个之间的节距是相同的,因此可解決在混合接合的接合界面处发生的腐蚀问题。

[0050]

在所示的实施例中,管芯550的数量为两个,然而管芯550的该数量仅是示例。在实施例中,所述伪焊盘234可以位于在所述两个管芯550之间的位置处。

[0051]

如图5p所示,在管芯550上接合一载体560,并将得到的结构倒置。执行平坦化操作而通过第一介电层510暴露处互连件512的表面。随后,如图5q所示,形成诸如导电凸块的电连接部件592以与互连件512连接。然后,去除载体560并将得到的结构倒置,如图5r所示。

[0052]

如图5s-1所示,形成底部填充物582以围绕管芯550的下部和第二线路层280。并且,形成包封管芯550、第二线路层280和底部填充物582的模制物584。在另一实施例中,可以不形成底部填充物,而只形成模制物来包封管芯550、第二线路层280的模制物584,如图5s-2所示。

[0053]

可选的,如图5t所示,可以在模制物584中形成连接至导电连接件232的贯通孔593,并通过贯通孔593和其他电连接件594与外部电路或器件598连接。

[0054]

上述内容概括了几个实施例的特征使得本领域技术人员可更好地理解本公开的各个方面。本领域技术人员应该理解,可以很容易地使用本发明作为基础来设计或更改其他的处理和结构以用于达到与本发明所介绍实施例相同的目的和/或实现相同优点。本领域技术人员也应该意识到,这些等效结构并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,可以进行多种变化、替换以及改变。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。