用于在固态驱动器控制器中使用nand闪存sram的方法

1.相关申请的交叉引用

2.无

技术领域

3.本发明大体上涉及固态驱动器(solid state drive,ssd)控制器,并且具体涉及在ssd控制器中使用与非(not-and,nand)闪存静态随机存取存储器(static random access memory,sram)的方法。

背景技术:

4.ssd将数据存储在固态设备中,而不是在磁性或光学介质中。典型的ssd包括控制器和固态存储器设备。主机设备对ssd进行读写操作。作为响应,ssd确认对数据的接收,存储数据,然后检索数据。在使用过程中,先前写入固态存储器设备的数据块可能会变得无效和不可用,直到它们被擦除。在一个称为“垃圾收集”的过程中,从第一个固态设备收集仍然有效的块,这些块被聚合并重写到其它固态设备。然后,第一固态设备的部分或全部被擦除,并再次用于写入数据。

技术实现要素:

5.第一方面涉及一种写入操作方法,由具有多个与非(not-and,nand)闪存设备的固态驱动器(solid state drive,ssd)的ssd控制器实现,所述多个nand闪存设备具有片上静态随机存取存储器(static random access memory,sram)和nand闪存。所述方法包括从包括多个数据块的流接收数据块;确定是否为所述流创建了条带;基于确定尚未为所述流创建所述条带,为所述流创建所述条带,所述条带通过以下步骤创建:将所述多个nand闪存设备的第一子集分配给所述条带,对可以在所述第一子集中的多个nand闪存设备中的每个nand闪存设备的所述片上sram中为所述条带存储的所述多个数据块的数量设置限制;在所述第一子集中的所述nand闪存设备中的一个nand闪存设备的所述片上sram中为所述条带存储所述数据块;当在所述nand闪存设备中的所述一个nand闪存设备的所述片上sram中存储所述数据块导致达到所述限制时,指示所述nand闪存设备中的所述一个nand闪存设备将在所述nand闪存设备中的所述一个nand闪存设备的所述片上sram中为所述条带存储的每个数据块编程到所述nand闪存设备中的所述一个nand闪存设备的所述nand闪存中。

6.可选地,根据上述任一方面,在所述方面的另一种实现方式中,还包括:当所述第一子集中的所有nand闪存设备成功地将所述第一子集中的所述nand闪存设备的所述片上sram中的所述数据块编程到所述第一子集中的所述nand闪存设备的所述nand闪存中时,使所述第一子集中的所述nand闪存设备中的每个nand闪存设备标记为可重复使用所述第一子集中的所述nand闪存设备中的每个nand闪存设备的所述片上sram。

7.可选地,根据上述任一方面,在所述方面的另一种实现方式中,从主机设备接收所述流的每个数据块,并且所述方法包括:在所述第一子集中的所述nand闪存设备中的一个

nand闪存设备的所述片上sram中为所述条带存储所述数据块之前,将所述数据块存储在所述ssd控制器的sram中;向所述主机设备发送确认消息;当所述数据块成功地存储在所述nand闪存设备中的所述一个nand闪存设备的所述片上sram中时,将存储所述数据块的所述ssd控制器的所述sram标记为可重复使用。

8.可选地,根据上述任一方面,在所述方面的另一种实现方式中,所述ssd控制器包括多个通道,每个通道耦合到所述多个nand闪存设备的第二子集,并且所述第一子集中的所述nand闪存设备中的每个nand闪存设备耦合到与所述第一子集中的其它nand闪存设备不同的通道。

9.可选地,根据上述任一方面,在所述方面的另一种实现方式中,确定是否为所述流创建了所述条带的步骤包括:当先前创建的条带的所有数据块存储在所述第一子集中的所述nand闪存设备的所述片上sram中时,确定尚未为所述流创建所述条带。

10.可选地,根据上述任一方面,在所述方面的另一种实现方式中,所述流是第一流,并且所述第一流的每个接收的数据块包括标识所述第一流的流标识符,还包括:从包括第二多个数据块的第二流接收第二数据块,所述第二数据块包括标识所述第二流的第二流标识符;确定是否为所述第二流创建了第二条带;基于确定尚未为所述第二流创建所述第二条带,为所述第二流创建所述第二条带,所述第二条带通过以下步骤创建:将所述多个nand闪存设备的第三子集分配给所述第二条带,对可以在所述第三子集中的多个nand闪存设备中的每个nand闪存设备的所述片上sram中为所述第二条带存储的所述第二多个数据块的数量设置第二限制;在所述第三子集中的所述nand闪存设备中的一个nand闪存设备的所述片上sram中为所述第二条带存储所述第二数据块;当在所述第三子集中的所述nand闪存设备中的所述一个nand闪存设备的所述片上sram中存储所述第二数据块导致达到所述第二限制时,指示所述第三子集中的所述nand闪存设备中的所述一个nand闪存设备将在所述第三子集中的所述nand闪存设备中的所述一个nand闪存设备的所述片上sram中为所述第二条带存储的每个数据块编程到所述第三子集中的所述nand闪存设备中的所述一个nand闪存设备的所述nand闪存中。

11.可选地,根据上述任一方面,在所述方面的另一种实现方式中,接收所述第一流中的数据块,其中夹杂着所述第二流中的数据块。

12.可选地,根据上述任一方面,在该方面的另一种实现方式中,还包括:从主机设备接收读取请求,所述读取请求指定待读取的请求的数据块;确定所述请求的数据块是否存储在所述多个nand闪存设备中的一个或多个nand闪存设备的片上sram中;基于确定所述请求的数据块存储在所述多个nand闪存设备中的所述一个或多个nand闪存设备的所述片上sram中:从所述多个nand闪存设备中的所述一个或多个nand闪存设备的所述片上sram读取所述请求的数据块;向所述主机设备发送所述请求的数据块。

13.可选地,根据上述任一方面,在所述方面的另一种实现方式中,还包括:将从所述多个nand闪存设备中的所述一个或多个nand闪存设备的所述片上sram读取的所述请求的数据块存储在所述ssd控制器的所述sram中;将所述请求的数据块从所述ssd控制器的所述sram发送到所述主机设备。

14.可选地,根据上述任一方面,在所述方面的另一种实现方式中,还包括:当断电事件被检测到时,使具有存储在所述片上sram中的数据块的所述多个nand闪存设备中的任何

nand闪存设备将所述数据块编程到所述nand闪存设备的所述nand闪存中。

15.第二方面涉及一种垃圾收集方法,由具有多个与非(not-and,nand)闪存设备的固态驱动器(solid state drive,ssd)的ssd控制器实现,所述多个nand闪存设备具有片上静态随机存取存储器(static random access memory,sram)和nand闪存,所述方法包括:从所述多个nand闪存设备中选择源nand闪存设备;从所述多个nand闪存设备中选择目的地nand闪存设备;对可以向所述目的地nand闪存设备写入的数据块的数量设置限制;通过以下步骤将数据块从所述源nand闪存设备发送到所述目的地nand闪存设备:从所述源nand闪存设备读取所述数据块,将所述数据块存储在所述目的地nand闪存设备的所述片上sram中;当在所述目的地nand闪存设备的所述片上sram中存储所述数据块导致达到所述限制时,使所述目的地nand闪存设备将所述目的地nand闪存设备的所述片上sram中的所述数据块编程到所述目的地nand闪存设备的所述nand闪存中。

16.可选地,根据上述任一方面,在所述方面的另一种实现方式中,所述ssd包括耦合到所述多个nand闪存设备的闪存子系统,所述闪存子系统包括随机化器和纠错电路。从所述源nand闪存设备读取所述数据块的步骤包括:通过对所述数据块进行纠错来创建纠错数据块;通过对所述纠错数据块进行去随机化来创建去随机化的数据块。将所述数据块存储在所述目的地nand闪存设备的所述片上sram中的步骤包括:通过对所述去随机化的数据块进行随机化来创建随机化的数据块来存储处理后的数据块;通过向所述随机化的数据块添加纠错码来创建所述处理后的数据块。

17.可选地,根据上述任一方面,在该方面的另一种实现方式中,还包括:在从所述源nand闪存设备读取所述数据块的步骤与将所述数据块存储在所述目的地nand闪存设备的所述片上sram中的步骤之间对所述数据块进行解密和重新加密。

18.可选地,根据上述任一方面,在所述方面的另一种实现方式中,所述ssd控制器包括多个通道,每个通道耦合到所述多个nand闪存设备的子集,并且所述源nand闪存设备耦合到与所述目的地nand闪存设备不同的通道。

19.可选地,根据上述任一方面,在所述方面的另一种实现方式中,所述选择源nand闪存设备的步骤包括选择多个源nand闪存设备;将所述数据块从所述源nand闪存设备发送到所述目的地nand闪存设备的步骤包括当所述多个源nand闪存设备中的第一源nand闪存设备上没有保留数据块时,从所述多个源nand闪存设备的第二源nand闪存设备读取后续数据块。

20.可选地,根据上述任一方面,在该方面的另一种实现方式中,还包括:指定待从所述源nand闪存设备读取的所述数据块在所述源nand闪存设备中的位置;从所述源nand闪存设备中的所述指定的位置读取所述数据块。

21.可选地,根据上述任一方面,在所述方面的另一种实现方式中,所述限制是基于所述目的地nand闪存设备能够存储的数据块数量来设置的。

22.可选地,根据上述任一方面,在所述方面的另一种实现方式中,从所述源nand闪存设备读取的所述数据块是使用与所述源nand闪存设备相关联的第一随机化键进行去随机化的,以产生所述去随机化的数据块;所述去随机化的数据块是使用与所述目的地nand闪存设备相关联的第二随机化键进行随机化的,以产生所述随机化的数据块。

23.可选地,根据上述任一方面,在所述方面的另一种实现方式中,还包括:当断电事

件被检测到时,使具有存储在所述片上sram中的数据块的所述多个nand闪存设备中的任何nand闪存设备将所述数据块编程到所述nand闪存设备的所述nand闪存中。

24.第三方面涉及一种具有多个与非(not-and,nand)闪存设备的固态驱动器(solid state drive,ssd)的ssd控制器,所述多个nand闪存设备具有片上静态随机存取存储器(static random access memory,sram)和nand闪存,所述ssd控制器包括:用于从包括多个数据块的流接收数据块的部件;用于从包括多个数据块的流接收数据块的部件;用于确定是否为所述流创建了条带的部件;用于基于确定尚未为所述流创建所述条带,为所述流创建所述条带的部件,所述条带通过以下步骤创建:将所述多个nand闪存设备的第一子集分配给所述条带,对可以在所述第一子集中的多个nand闪存设备中的每个nand闪存设备的所述片上sram中为所述条带存储的所述多个数据块的数量设置限制;用于在所述第一子集中的所述nand闪存设备中的一个nand闪存设备的所述片上sram中为所述条带存储所述数据块的部件;用于当在所述nand闪存设备中的所述一个nand闪存设备的所述片上sram中存储所述数据块导致达到所述限制时,指示所述nand闪存设备中的所述一个nand闪存设备将在所述nand闪存设备中的所述一个nand闪存设备的所述片上sram中为所述条带存储的每个数据块编程到所述nand闪存设备中的所述一个nand闪存设备的所述nand闪存中的部件。

25.可选地,根据上述任一方面,在所述方面的另一种实现方式中,提供了:用于从主机设备接收读取请求的部件,所述读取请求指定待读取的请求的数据块;用于确定所述请求的数据块是否存储在所述多个nand闪存设备中的一个或多个nand闪存设备的片上sram中的部件;用于基于确定所述请求的数据块存储在所述多个nand闪存设备中的一个或多个nand闪存设备的所述片上sram中,从所述多个nand闪存设备中的所述一个或多个nand闪存设备的所述片上sram中读取所述请求的数据块,并将所述请求的数据块发送到所述主机设备的部件。

26.第四方面涉及一种具有多个与非(not-and,nand)闪存设备的固态驱动器(solid state drive,ssd)的ssd控制器,所述多个nand闪存设备具有片上静态随机存取存储器(static random access memory,sram)和nand闪存,所述ssd控制器包括:用于从所述多个nand闪存设备中选择源nand闪存设备并从所述多个nand闪存设备中选择目的地nand闪存设备的部件;用于对可以向所述目的地nand闪存设备写入的数据块的数量设置限制的部件;用于通过以下步骤将数据块从所述源nand闪存设备发送到所述目的地nand闪存设备的部件:从所述源nand闪存设备读取所述数据块,将所述数据块存储在所述目的地nand闪存设备的所述片上sram中;用于当在所述目的地nand闪存设备的所述片上sram中存储所述数据块导致达到所述限制时,使所述目的地nand闪存设备将所述目的地nand闪存设备的所述片上sram中的所述数据块编程到所述目的地nand闪存设备的所述nand闪存中的部件。

27.为了清楚起见,上述任一种实现方式可以与上述其它任何一种或多种实现方式组合以创建在本发明范围内的新实施例。从结合附图和权利要求书的以下详细描述中,将更清楚地理解这些实施例和其它特征。

附图说明

28.为了更完整地理解本发明,结合附图和具体实施方式,参考以下简要描述,其中,相同的附图标记表示相同的部件。

29.图1是nand闪存ssd的示意图。

30.图2是图1的ssd的nand闪存设备的示意图。

31.图3是图1的ssd执行写入操作过程的数据流图。

32.图4是图1的ssd执行垃圾收集过程的数据流图。

33.图5是根据本发明的ssd的nand闪存设备的示意图。

34.图6是根据本发明的ssd执行写入操作过程的数据流图。

35.图7是图6的ssd执行垃圾收集(garbage collection,gc)过程的数据流图。

36.图8a至图8d示出了图6的写入操作过程的更详细的视图。

37.图9a至图9d示出了图7的gc过程的更详细的视图。

38.图10示出了根据本发明的读取操作过程的流程图。

39.图11是根据本发明的实施例的处理器设备的示意图。

40.图12示出了用于实现本文所描述的方法中的一个或多个的装置。

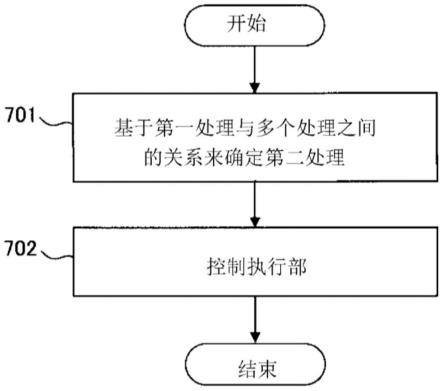

41.图13示出了用于实现本文所描述的方法中的一个或多个的装置。

42.图14示出了用于实现本文所描述的方法中的一个或多个的装置。

具体实施方式

43.首先应理解,尽管下文提供了一个或多个实施例的说明性实现方式,但所公开的系统和/或方法可使用任何数量的技术来实现,无论这些技术是当前已知还是现有的。本发明绝不限于下文所说明的说明性实现方式、附图和技术,包括本文所说明和描述的示例性设计和实现方式,而是可在所附权利要求书的范围以及其等效部分的完整范围内修改。

44.新开发的nand闪存芯片在芯片上包括sram。这样的芯片可以是三维(three dimensional,3d)nand芯片或四维(four dimensional,4d)nand芯片。在本发明中,这两种类型将统称为“具有片上sram的nand芯片”。一些这种nand芯片提供1兆字节(megabyte,mb)的片上sram,但另一些芯片提供大于或小于1mb的片上sram。本发明提供了用于使用具有片上sram的这种nand芯片的片上sram来执行写入操作和垃圾收集的新过程。

45.图1是nand闪存ssd 100的示意图。ssd 100包括主中央处理器(central processing unit,cpu)102和nand闪存接口(nand flash interface,nfi)cpu 108。主cpu 102包括前端cpu 104和后端cpu 106。前端cpu 104实现用于通过外围组件互连标准(peripheral component interconnect express,pcie)总线、串行连接小型计算机系统接口(serial attached small computer system interface,sas scsi)总线或其它适当的接口从主机设备130接收的命令的处理程序。前端cpu 104还实现响应于接收到的主机命令而发出的后端(back end,be)命令的调度器。后端cpu 106实现后端固件(firmware,fw)、执行闪存转换层(flash translation layer,ftl)、映射和其它后端功能。

46.nfi cpu 108控制和管理通道122。每个通道122将数据和命令发送到nand闪存阵列150中的nand闪存设备124的子集(参考图2进行了更详细的描述)。在其它ssd中,主cpu 102和/或nfi cpu 108可以用其它数量或类型的cpu和/或其它功能分布来实现。

47.ssd 100还包括动态随机存取存储器(dynamic random access memory,dram)112、静态随机存取存储器(static random access memory,sram)114、硬件(hardware,hw)加速器116和其它外设118。dram 112的大小为32千兆字节(gigabyte,gb),但在其它ssd中

可以更大或更小。sram 114是10兆字节(megabyte,mb),但在其它ssd中可以更大或更小。

48.hw加速器116包括异或(exclusive-or,xor)引擎、缓冲区管理器、hw垃圾收集(garbage collection,gc)引擎,并且可以包括设计成独立处理主cpu 102和nfi cpu 108的特定、有限功能的其它hw电路。其它外设118可以包括各种电路,例如串行外设接口(serial peripheral interface,spi)电路、通用输入/输出(general purpose input/output,gpio)电路、内部集成电路(inter-integrated circuit,i2c)总线接口、通用异步接收器/发送器(universal asynchronous receiver/transmitter,uart)电路和其它接口电路。

49.ssd 100还包括闪存子系统120,闪存子系统120可以包括低密度奇偶校验(low density parity check,ldpc)或其它纠错电路、随机化器电路、闪存信号处理电路,并且可以包括提供与向nand闪存阵列150写入和读取数据有关的处理的其它电路。主cpu 102、nfi cpu108、dram 112、sram 114、hw加速器116、其它外设118和闪存子系统120包括ssd控制器,并通过互连网络(或总线)110通信地耦合到主机设备130。

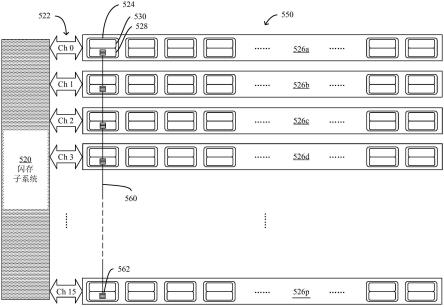

50.图2是图1的ssd 100的nand闪存阵列150的示意图。每个通道122将数据和命令从闪存子系统120发送到nand闪存阵列150的nand闪存芯片的子集。16个通道ch0、ch1

……

ch15分别耦合到nand闪存阵列150的子集126a、126b

……

126p。每个子集内有16个nand闪存设备124(也可以称为逻辑单元(logical unit,lun))。每个nand闪存设备124耦合到一个通道122,并且没有nand闪存设备124耦合到一个以上的通道122。在其它ssd中,可以使用更少的通道或更多的通道。类似地,在其它ssd中,可以为每个通道提供更少的或更多的nand闪存设备。

51.条带160包括nand闪存阵列150的每个子集126a、126b

……

126p中的一个nand闪存设备124。条带160还包括条带160的每个nand闪存设备124内的一个或多个数据块162。

52.图3是图1的ssd 100执行写入操作过程300的数据流图。在步骤302中,主机设备130向ssd 100发送待写入nand闪存阵列150的数据块流。当流中的块进入ssd 100时,它们临时存储在sram 114中。在一些ssd中,接收到的块也可以临时存储在dram 112中,如步骤302a所示。在每个块成功地存储在sram 114或dram 112中之后,在步骤306中,对该块的确认被发送到主机设备130。在接收到足够数量的块以形成条带160(参考图2所描述)之后,在步骤304中,条带160的块从sram 114写入nand闪存阵列150(或在步骤304a中,从dram 112写入),这被称为“刷新”操作。条带160包括待通过十六个通道122中的每一个通道写入nand闪存阵列150的十六个子集126a至126p中的每一个子集的nand闪存设备的一个或多个块。

53.主机设备130可以具有多个并发应用程序,每个应用程序向ssd 100写入和读取其块流,以要求ssd提供多流功能。因此,在步骤302中接收的块流可以夹杂多个流中的块,每个块包括流标识符,以按照流将块分离。主机提供类似多流的ssd功能可能有其它原因,例如持久数据库对象的存储和键:值存储。

54.虽然与sram 114和dram 112的大小相比,从主机设备130写入ssd 100的块通常较小,但几个因素结合起来却会限制ssd 100可以提供给主机设备130的单独同时流的数量。这些因素包括但不限于条带160中的块数量、将条带160写入nand闪存阵列150并接收所有块成功地写入的确认所需的时间,以及sram 114(和/或dram 112)的大小。

55.有时,主机设备130会对ssd 100执行读取操作,以读取主机设备130写入ssd 100

的数据。这种读取操作可以称为“立即读取”或“写入后立即读取”。如果主机设备130在步骤304的刷新操作的启动之前执行立即读取操作,则主cpu 102确定所请求的数据仍然存储在sram 114(或dram 112)中,并将存储的数据发送到主机设备130以完成读取操作。在这种情况下,读取操作可以在几十微秒内完成。

56.但是,如果步骤304的刷新操作已开始,则请求的数据不再可从sram 114(或dram 112)获得,并且在请求的数据被编程到nand闪存阵列150之后,读取操作无法完成。在这种情况下,读取操作的完成可能会延迟3至7毫秒。

57.图4是图1的ssd 100执行垃圾收集(garbage collection,gc)过程400的数据流图。gc可以由主cpu 102启动,并由hw加速器116中的gc引擎执行。在步骤402中,nand闪存阵列150的子集126a的一个或多个源nand中的所有有效块通过ch0通道122读取,并临时存储在sram 114中。在收集了足够数量的有效块之后,在步骤404中,这些块通过ch15通道122写入nand闪存阵列150的子集126p的目的地nand。虽然使用子集126a和126p示出了gc过程400的数据流图,但应理解,垃圾收集过程400可以使用nand闪存阵列150的任何源nand和目的地nand来执行,尽管通常源nand和目的地nand通过通道122中的不同的通道来接入。

58.虽然gc过程400的数据流图仅显示了正在执行的单个gc过程,但在一些ssd中,使用通道122的其它组合同时在多个源nand上执行并行gc过程。在一些这种ssd中,在多个垃圾收集过程中收集的有效块的总数可以受到sram 114的大小的限制,或可以要求dram 112用作sram 114的溢出存储,其中,一些有效块在步骤402a中临时存储,并在步骤404a中写入目的地nand。

59.图5是根据本发明的ssd 500的nand闪存阵列550(在图6中更详细地示出)的示意图。nand闪存阵列550包括多个nand闪存设备523。每个通道522将数据和命令从闪存子系统520发送到nand闪存阵列550中的nand闪存设备524的子集526a、526b

……

526p。每个子集内有16个nand闪存设备524(也可以称为lun)。每个nand闪存设备524耦合到一个通道522,并且没有nand闪存设备524耦合到一个以上的通道522。在根据本发明的其它ssd中,可以使用更少的通道或更多的通道。类似地,在根据本发明的其它ssd中,可以为每个通道提供更少的或更多的nand闪存设备。每个nand闪存设备524包括片上sram 528和闪存530。

60.在一些实施例中,sram 528的大小为1mb,但是在其它实施例中,可以更大。在一些其它实施例中,16个以上的nand闪存设备可以包括在子集中和/或16个以上的通道和子集可以耦合到闪存子系统520。

61.图6是根据本发明的ssd 500对数据块执行写入操作过程600的数据流图。在步骤602中,ssd 500从主机设备130接收包括多个数据块的流中的数据块,这些数据块待写入nand闪存阵列550。当接收到每个块时,前端cpu 504将该块临时存储在sram 514中,并且在成功地存储在sram 514中之后,在步骤610中,前端cpu 504向主机设备130发送对该块的确认。当在步骤604(在图8c中示出)中接收到流中的第一块时,后端cpu 506确定没有为流创建条带,并且作为响应,创建条带560,并将条带nand闪存设备524分配给条带560,并将对待写入的块数量的限制分配给每个分配的条带nand闪存设备524。分配的条带nand闪存设备524包括nand闪存阵列550中的nand闪存设备524的子集。当接收到新条带560中的第一块时,在每个通道522中对条带nand闪存设备524进行分配,新条带560的块将存储在条带nand闪存设备524中。

62.条带560包括nand闪存阵列550的每个子集526a、526b

……

526p中的一个nand闪存设备524。条带560还包括条带560的每个nand闪存设备524的片上sram 528内的一个或多个数据块562。

63.在根据本发明的其它ssd中,条带560分配的创建可以在主cpu 502中的其它地方进行。虽然条带560使用nand闪存阵列550的nand闪存设备524的子集526a、526b

……

526p中的每个子集中的第一nand闪存设备524,但将理解,另一个条带560可以使用子集526a、526b

……

526p中的不同子集中的不同的nand闪存设备524。例如,使用子集526a的第二nand闪存设备524、子集526b的第十nand闪存设备524、子集526c的第六nand闪存设备524等。

64.在条带560中的每个块被接收并存储到sram 514中之后,无需等待条带560中的所有块被接收,在步骤606中,nfi cpu 508将该块写入分配给该块的条带nand闪存设备524中的片上sram 528进行临时存储。在每个块写入片上sram 528之后,块在sram 514中的存储空间被释放以供后续使用。

65.在一些实施例中,条带560包括64个块,其中四个块写入条带nand闪存设备524中的每个sram 528。在一些这种实施例中,条带560中的前四个接收块写入耦合到通道522ch0的条带nand闪存设备524的sram 528,接下来的四个接收块写入耦合到通道522ch1的条带nand闪存设备524的sram 528,依此类推,直到条带560中的最后四个接收块写入耦合到通道522ch15的条带nand闪存设备524的sram 528。在其它这种实施例中,条带560中的第一接收块写入耦合到通道522ch0的条带nand闪存设备524的sram 528,第二接收块写入耦合到通道522ch1的条带nand闪存设备524的sram 528,依此类推,直到第十六接收块写入耦合到通道522ch15的条带nand闪存设备524的sram 528。然后,条带560中的第十七接收块写入耦合到通道522ch0的条带nand闪存设备524的sram528,第十八接收块写入耦合到通道522ch1的条带nand闪存设备524的sram 528,依此类推,直到第六十四接收块写入耦合到通道522ch15的条带nand闪存设备524的sram528。

66.在其它实施例中,条带560可以包括多于或少于64个块,其中,块在条带nand闪存设备524之间均匀或不均匀分布。在刚才描述的场景中,块顺序写入耦合到通道522ch0、ch1、

……

ch15的条带nand闪存设备524的片上sram 528,但是,可以理解,在其它场景中,块可以以任意顺序写入耦合到通道522ch0至ch15的条带nand闪存设备524中的片上sram 528,直到整个条带560都写入片上sram 528。

67.同样在步骤606中,nfi cpu 508确定是否达到对待写入条带nand闪存设备524的片上sram 528的块数量的限制。如果达到限制,则nfi cpu 508向该条带nand闪存设备524发出“提交”命令,以使其将来自其片上sram 528的块编程到条带nand闪存设备524的nand闪存530中。当达到对其它条带nand闪存设备524的限制时,类似的单个“提交”命令被单独发送到这些其它条带nand闪存设备524中的每一个。因此,接收条带560的块的每个条带nand闪存设备524的nand闪存530与其它条带nand闪存设备524的nand闪存530独立地和异步地编程。然而,为了支持从任何条带nand闪存设备524中的写入故障中恢复,条带560中的块被保存在它们相应的片上sram 528中,直到条带560的所有块都被成功地编程到条带560的所有条带nand闪存设备524的nand闪存530中,并且只有这样,在步骤608中,后端cpu 506才发送“释放”命令,以使条带560的所有条带nand闪存设备524标记为可重复使用它们的片上sram 528中的块的存储空间。如果在任何条带nand闪存设备524中发生写入故障,则不会

发送“释放”命令,并且条带nand闪存设备524中的一个或多个中的数据可以从片上sram 528中恢复,根据需要重新处理,并写入一个或多个其它nand闪存设备524的片上sram 528,以编程到一个或多个其它闪存设备524的nand闪存530中。

68.在完整的条带560写入nand闪存阵列550之后,当接收到同一流中的附加块时,在步骤604中创建另一个条带。

69.ssd 500用于同时接收多个流中的块。从写入操作过程600的描述可以看出,ssd 500可以同时从主机设备130接收的流的数量大于ssd 100,这是因为由ssd 500接收的每个流的块存储在sram 514中,存储的时间量仅为将每个块写入条带nand闪存设备524中的片上sram 528所需的时间量,然后用于块的sram 514中的存储空间被释放以供重复使用。相比之下,在ssd 100中,在将条带中的所有块写入nand闪存阵列150并释放它们在sram114中的存储空间以供重复使用之前,条带中的所有块必须存储在sram 114中。

70.虽然过程600被描述为存储作为流的一部分的块,但可以理解,过程600也可以用于存储由主机设备130发送的块,以用于持久数据库对象的存储和/或用于键:值存储。

71.如果主机设备130执行请求当前写入条带560的数据的“立即读取”操作,则在将条带560的数据块编程到条带nand闪存设备524的长时间过程中,所请求的数据可从与条带560相关联的条带nand闪存设备524的片上sram 528获得。也就是说,在整个写入操作过程600中,通过从一个或多个片上sram 528读取请求的数据块,将它们存储在sram 514中,以及将请求的块发送到主机设备130以完成读取操作,可以在几十微秒内完成请求当前写入条带560的数据块的“立即读取”操作(如参考图10更详细地描述的)。在相关联的条带nand闪存设备524的编程完成,并且后端cpu 506发送了“释放”命令以释放条带560在片上sram528中的存储空间之后,用于“立即读取”操作的请求数据在条带nand闪存设备524中不再可用。因此,写入操作过程600消除了在ssd 100的写入操作过程300中完成“立即读取”操作时的长时间延迟,如果在步骤304的刷新操作开始之后但在请求的数据编程到nand闪存阵列150之前接收到“立即读取”操作,则该长时间延迟发生。

72.图7是图6的ssd 500执行垃圾收集过程700的数据流图。主cpu 502通过选择耦合到通道522ch0的一个或多个nand闪存设备524(或源nand)用于垃圾收集,选择耦合到通道522ch15的nand闪存设备524(或目的地nand)用于接收收集的块,以及对可以写入目的地nand闪存设备524的数据块的数量设置限制,来准备垃圾收集过程700的参数。然后,为了执行垃圾收集,将所选择的源nand闪存设备524中的有效块读出到闪存子系统520的电路中。在闪存子系统520中,块由ldpc电路542校正错误,由随机化器540使用其源nand闪存设备524的随机化键去随机化,然后由随机化器540使用目的地nand闪存设备524的随机化键重新随机化,并且纠错码由ldpc电路542添加。在重新随机化和纠错编码之后,块通过ch15通道522写入目的地nand闪存设备524的片上sram 528。在块写入片上sram 528中时,片上sram 528中的块可以单独编程到目的地nand闪存设备524的nand闪存530中,在对块的限制写入片上sram 528中时,这些块成组地编程,或在这些块都写入片上sram 528中之后,在单个写入操作中编程。

73.在一些实施例中,在去随机化与重新随机化之间,块发送到hw加速器516中的加密/解密引擎,在该加密/解密引擎中,这些块在由随机化器540重新随机化之前被解密和重新加密。

74.虽然过程700被描述为从耦合到通道522ch0的源nand闪存设备524收集有效块,并将处理后的块写入耦合到通道522ch15的目的地nand闪存设备524,但应理解,过程700可以用于从耦合到任何通道522的源nand闪存设备524收集有效块,并在任何其它通道522中将收集的块写入目的地nand闪存设备524。

75.图8a至图8d示出了图6的写入操作过程600的更详细的视图。图8a示出了写入操作过程600的概述。在步骤602中,ssd 500从主机设备130接收流中的数据块,该流包括待写入nand闪存阵列550的多个数据块。在步骤604中,后端cpu 506确定没有为流创建条带560(或先前完成了为流创建条带560),并且作为响应,创建用于存储接收到的数据块的条带560。在步骤606中,ssd 500将接收到的数据块存储到分配给条带560的nand闪存设备524中的一个中。在条带560被填充之后,在接收到流的后续数据块时,重复步骤604,以创建附加的条带560。下面分别参考图8b、图8c和图8d更详细地描述步骤602、604和606。

76.在步骤608中,在nfi cpu 508向后端cpu 506报告所有条带nand闪存设备524成功地将其用于条带560的数据块编程到其nand闪存530中之后,后端cpu 506使所有条带nand闪存设备524将其存储了条带560的数据块的片上sram 528的部分标记为可重复使用。

77.在步骤602中接收的数据块包括流标识符,该流标识符标识数据块所属的流。ssd 500可以以夹杂的方式接收多个流中的数据块。如果ssd 500接收到具有不同于先前接收到的数据块的流标识符的流标识符的数据块,则ssd 500为每个新识别的流创建写入操作过程600的新实例化。每个实例化为其流创建独立的条带560,并将其流的数据块存储到独立的条带560。虽然上面的描述将术语“流标识符”用于标识流的数据,但可以理解,该术语也可以用于存储持久数据库对象或键:值数据库的流。

78.图8b更详细地示出了从主机设备130接收流中的数据块的步骤602。在步骤602a中,从主机设备130接收数据块。在步骤602b中,前端cpu 504将数据块临时存储在sram 514中。在前端cpu 504确定数据块成功地存储在sram 514中之后,在步骤610中,前端cpu504向主机设备130发送对该块的确认。

79.图8c更详细地示出了创建条带560的步骤604。在步骤604a中,后端cpu 506分配多个nand闪存设备524(或条带nand闪存设备)的子集,条带560的数据块将存储到其中。在一些实施例中,后端cpu 506从nand闪存阵列550的nand闪存设备524的每个子集526a-526p向条带560分配一个条带nand闪存设备524,即,每个通道522一个条带nand闪存设备524。在步骤604b中,后端cpu 506分配对将存储到每个条带nand闪存设备524中的数据块的数量的限制。在一些实施例中,对每个条带nand闪存设备524的限制是四个数据块。

80.图8d更详细地示出了将接收到的数据块存储到分配给条带560的nand闪存设备524中的一个的步骤606。在步骤606a中,后端cpu 506将接收到的数据块存储在条带nand闪存设备524的片上sram 528中。在步骤606中,在数据块成功地写入条带nand闪存设备524的片上sram 528中之后,主cpu 502释放sram 514中存储数据块的部分,供随后重复使用。

81.在一些实施例中,所有接收到的数据块存储到第一条带nand闪存设备524的片上sram 528,直到该设备对数据块的限制被存储,然后,所有后续接收到的数据块存储到第二条带nand闪存设备524的片上sram 528,直到该设备对数据块的限制被存储,依此类推,直到条带560的所有数据块存储到所有条带nand闪存设备524的片上sram 528。在其它实施例中,每个接收到的数据块存储到任意条带nand闪存设备524的片上sram 528,直到条带560

的所有数据块都存储到条带560的条带nand闪存设备524的片上sram 528。

82.在步骤606b中,在接收到的数据块存储到条带nand闪存设备524的片上sram 528之后,后端cpu 506确定是否达到待存储到条带nand闪存设备524的片上sram 528的数据块的限制。如果没有达到限制,则写入操作过程600结束。如果达到限制,则在步骤606c中,nfi cpu 508使条带nand闪存设备524将条带560的数据块编程到其nand闪存530中。

83.图9a至图9d示出了图7的gc过程700的更详细的视图。在步骤702中,后端cpu 506准备垃圾收集参数,如图9b中更详细地描述的。在步骤704中,根据在步骤702中准备的参数执行垃圾收集过程,如图9c中更详细地描述的。

84.图9b更详细地示出了准备垃圾收集参数的步骤702。在步骤702a中,后端cpu 506选择待从其读取有效数据块的至少一个源nand闪存设备524(或源nand)。如果单个源nand闪存设备524没有足够数量的用于完整gc过程700的有效数据块,则后端cpu 506选择待从其读取有效数据块的附加源nand闪存设备524,直到可以从所选择的源nand闪存设备524读取用于完整gc过程700的足够数据块。对于每个选择的源nand闪存设备524,后端cpu 506指定待读取的有效数据块的位置。

85.在步骤702b中,后端cpu 506选择数据块将存储到其中的目的地nand闪存设备524(或目的地nand)。在步骤702c中,后端cpu 506对可以写入目的地nand闪存设备524的数据块的数量设置限制。在一些实施例中,该限制被设置为被认为足以用于完整gc过程700的数据块数量,如步骤702a中使用的。在其它实施例中,该限制被设置为某个块数量,该块数量基于目的地nand闪存设备524能够存储的块数量。

86.图9c更详细地示出了执行垃圾收集过程的步骤704。在步骤706中,从源nand闪存设备524读取有效数据块,并写入目的地nand闪存设备524的片上sram 528(如参考图9d更详细地解释的)。在步骤708中,确定是否达到对待存储在目的地nand闪存设备524的片上sram 528中的数据块数量的限制。如果没有达到限制,则过程700返回到步骤706,以读取和存储另一个数据块。如果达到限制,则在步骤710中,nfi cpu 508使目的地nand闪存设备524将片上sram 528中的数据块编程到nand闪存530中。

87.图9d更详细地示出了从所选择的源nand闪存设备524读取数据块并将其写入所选择的目的地nand闪存设备524的片上sram 528的步骤706。在步骤706a中,nfi cpu 508使从源nand闪存设备524中的指定位置读取数据块,并使用闪存子系统520的纠错电路对数据块进行纠错。然后,nfi cpu 508通过与源nand闪存设备524相关联的随机化键,使用闪存子系统520的随机化器电路来去随机化数据块。在步骤706b中,nfi cpu 508通过闪存子系统520的随机化器电路,使用与所选择的目的地nand闪存设备524相关联的随机化键重新随机化去随机化和纠错数据块,通过ldpc电路542添加纠错码,并使所产生的数据块写入所选择的目的地nand闪存设备524的片上sram 528。

88.在一些实施例中,在步骤706a与706b之间,去随机化和纠错块被发送到hw加速器516中的加密/解密引擎,在该加密/解密引擎中,这些块在由随机化器540重新随机化之前被解密和重新加密。

89.图10示出了根据本发明的读取操作过程1000的流程图。在步骤1002中,ssd 500接收来自主机设备130的读取操作请求。读取操作请求指定待读取的数据块,并包括块的流标识符。在步骤1004中,主cpu 502确定请求的数据块是否是在写入操作过程600的实例化中

当前写入nand闪存阵列550的条带560的一部分(即,请求的数据块是否存储在一个或多个条带nand闪存设备524的片上sram中)。步骤1004包括确定写入操作过程600的实例化是否到达步骤608,其中,存储条带560的数据块的片上sram 528的部分被释放并标记为供重复使用。如果确定数据块当前未在写入操作过程600中写入,则在步骤1006中,主cpu 502启动传统的读取操作过程,以从nand闪存阵列550读取请求的数据块。

90.如果在步骤1004中确定请求的数据块是当前在写入操作过程600的实例化中写入的条带560的一部分,则在步骤1008中,后端cpu 506使nfi cpu 508从条带nand闪存设备524的存储数据块的片上sram 528读取请求的数据块,然后请求的数据块发送到主机设备130。在将请求的数据块发送到主机之前,在步骤1008中,临时将部分或全部请求的数据块存储在sram 514中。

91.在写入操作过程600或gc过程700期间,如果在ssd 500中检测到发生了断电事件,则ssd 500的断电保护(power loss protection,plp)功能使得主cpu 502使具有临时存储在其片上sram 528中的数据块的任何nand闪存设备524将数据块编程到其nand闪存530,以防止数据丢失。在ssd 500恢复供电之后,主cpu 502使所存储的数据块由相关联的nand闪存设备524检索到其片上sram 528中,并执行电力损失恢复过程以完成被电力损失事件中断的任何写入操作过程600和/或gc过程700。

92.图11是根据本发明的实施例的处理器设备1100的示意图。处理器设备1100适用于实现本文所描述的公开实施例。处理器设备1100包括处理器、逻辑单元或其它用于处理数据的适当处理电路1130;总线收发器(xcvr)1140和总线端口1150,用于通过图6和图7所示的互连网络(或总线)510的总线发送和接收数据;存储器1260,用于存储数据。处理器设备1100适合于实现由主cpu 502、前端cpu 504、后端cpu 106或nfi cpu 508执行的本文所描述的功能。

93.处理器1130通过硬件和软件来实现。处理器1130可以实现为一个或多个cpu芯片、核(例如,多核处理器)、现场可编程门阵列(field-programmable gate array,fpga)、专用集成电路(application specific integrated circuit,asic)和数字信号处理器(digital signal processor,dsp)。处理器1130与总线收发器1140、总线端口1150和存储器1160通信。处理器1130包括ssd控制模块1170。ssd控制模块1270实现以上所描述的公开实施例。例如,ssd控制模块1170执行写入操作过程600和垃圾收集过程700中的一个或多个的步骤。因此,包括ssd控制模块1170对处理器设备1100的功能提供了实质性的改进,并实现处理器设备1100到不同状态的转换。替代地,ssd控制模块1170实现为存储在存储器1160中并由处理器1130执行的指令。

94.存储器1160可以用作溢出数据存储设备,以在选择程序用于执行时存储这些程序,以及存储程序执行期间读取的指令和数据。存储器1160可以是易失性和/或非易失性的,并且可以是只读存储器(read-only memory,rom)、随机存取存储器(random access memory,ram)、三态内容寻址存储器(ternary content-addressable memory,tcam)和静态随机存取存储器(static random-access memory,sram)。

95.图12示出了用于实现本文所描述的一个或多个方法(例如图8a的写入操作过程600)的装置1200。装置1200包括用于从主机设备接收数据块的部件1202,如参考图8b所描述;用于在存储接收的数据块的nand闪存阵列的nand闪存设备中创建条带的部件1204,如

参考图8c所描述;用于将接收到的数据块存储到分配给条带的nand闪存设备中的一个的部件1206,如参考图8d所描述。

96.图13示出了用于实现本文所描述的一个或多个方法(例如图9a的垃圾收集过程700)的装置1300。装置1300包括:用于准备垃圾收集参数的部件1302,如参考图9b所描述;用于根据参数执行垃圾收集过程的部件1304,如参考图9c所描述。

97.图14示出了用于实现本文所描述的一个或多个方法(例如图10的读取操作过程1000)的装置1400。装置1400包括:用于接收来自主机设备的读取操作请求的部件1402;用于确定读取请求中指定的数据块是否存储在nand闪存设备的片上sram中的部件1404;用于从片上sram读取请求的数据块并将请求的数据块发送到主机设备的部件1406。

98.所公开的实施例可以是任何可能的集成技术细节级别的系统、装置、方法和/或计算机程序产品。计算机程序产品可包括具有计算机可读程序指令的计算机可读存储介质,计算机可读程序指令使得处理器执行本发明的各方面。计算机可读存储介质可以是能够保留和存储指令以供指令执行设备使用的有形设备。

99.虽然本发明提供了若干个实施例,但应当理解,在不脱离本发明的精神或范围的情况下,所公开的系统和方法可以通过其它多种具体形式体现。当前的这些示例被认为是说明性的而非限制性的,并且意图不限于本文给出的细节。例如,各种元件或组件可以组合或集成在另一个系统中,或可以省略或不实现一些特征。

100.此外,在不脱离本发明的范围的情况下,各种实施例中描述和说明为离散或单独的技术、系统、子系统和方法可以与其它系统、模块、技术或方法组合或集成。展示或讨论为彼此耦合或直接耦合或通信的其它项也可以使用电方式、机械方式或其它方式通过某一接口、设备或中间组件间接地耦合或通信。变化、替换、变更的其它示例可由本领域技术人员确定,并可以在不脱离本文中公开的精神和范围的情况下举例。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。