1.本发明属于微处理器可靠性设计领域,在复制寄存器过程中暂停物理寄存器释放,并预测程序段所需的运行时钟周期划分程序段,降低异构并行差错检测对主核性能的影响并降低差错检测的延时。

背景技术:

2.汽车半导体和车载信息产业革命以来,每辆汽车上的电子控制单元(ecu)越来越多,对汽车电子可靠性的要求也越来越高。但是汽车芯片面临着高温、高湿等严峻的工作环境,使得车载处理器与一般电子系统相比更加频繁地产生差错,使汽车芯片的可靠性面临严峻的考验。双核锁步通过两个处理器核运行相同的程序,并对两个核的输出进行比较来检测,有成倍的面积、功耗开销,由于其较高的差错检测速度和差错覆盖率能够满足汽车芯片可靠性的要求。异构并行差错检测通过使用一系列低性能的检查核并行重复运行高性能主核的程序段进行差错检测。为了提高性能,芯片的面积和功耗呈超线性增长,这些低性能核的面积、功耗之和小于高性能核,能够以较低的功耗、面积开销,实现与双核锁步近似的差错覆盖率。

3.每次复制寄存器状态需要暂停提交指令会影响主核性能。异构并行差错需要将高性能主核的程序划分为多个程序段,分配给检查核重复运行进行差错检测。因此在每个程序段的开始与结束都需要将主核当前状态复制给检查核,使得检查核能够以相同的状态开始运行,并在运行完之后比较寄存器状态实现差错检测。在复制寄存器堆状态时,由于面积功耗的开销,不能设置过多的读端口,因此需要主核暂停提交指令多个周期,将寄存器堆装填复制给检查核,主核暂停提交指令会影响它的性能。而程序段划分的粒度决定了主核暂停的频率,为了减小对主核的影响,通常需要设置较大的程序段,以减小主核暂停提交的频率,从而降低差错检测对主核性能的影响。与此同时,对于某些差错需要检查核将程序段执行完比较寄存器状态才能够将其检测出来,而由于检查核性能较低,较大的程序段需要较长的运行时间,将会带来较大的差错检测延时。

4.异构并行差错检测的实现还需要考虑如何划分程序段以设置合适的检查点。为了检查核能够重复运行程序段,主核会将加载(load)/存储(store)指令的数据与地址保存到日志中,对于加载指令,检查核直接从日志中获取数据作为输入,对于存储指令,将日志中的数据与地址进行比较进行差错检测。每当当前检查核的日志装满或者主核提交足够的指令,需要将当前状态作为检查点划分程序段。由于load/store的在程序段中出现的频率不同,装满日志时每个程序段的指令数量不同,并且程序段中的每条指令运行时间也不同,比如乘除法指令比普通的加法指令需要更多的执行周期,浮点运算指令则需要更多的执行周期。因此,不同的程序段,会由于其指令数量、指令种类的不同需要运行不同的时间。由于检查核的性能远低于主核,对于某些差错,需要检查核运行完整个程序段,最后对程序段结束时的寄存器状态进行比较才能够被检测出来,导致差错检测有过大的延时,无法满足关键系统的实时性需求。

技术实现要素:

5.本发明为了降低异构并行差错检测对高性能主核性能的影响,减少差错检测的延时,提出了在复制寄存器时,暂停物理寄存器释放的方法,将检查点状态保存在物理寄存器堆中,从而无需主核暂停提交指令,允许设置更小的程序段,并根据预测的程序段运行时间划分程序段,使得差错检测的延时可控。

6.针对现有技术的不足,本发明提出一种控制运行时钟周期的处理器运行差错检测方法,其中包括:

7.步骤1、获取具有主核以及检查核的处理系统,且该主核与该检查核有相同的指令集架构;

8.步骤2、当该主核运行待执行程序时,根据该主核提交的指令种类和数量对程序段在该检查核的运行时钟周期进行预测,当该运行时钟周期大于阈值,则将该主核当前的状态作为检查点划分程序段;

9.步骤3、将该主核开始运行该程序段时的状态复制给该检查核,使该检查核以与该主核相同的状态开始运行,在该检查核运行该程序段的过程中,对于加载指令,直接访问该加载存储日志,获取加载数据作为加载结果,并判断该加载结果的地址是否和该加载存储日志中加载地址相同,若不同则表示产生差错;当该检查核结束运行该程序段,判断该检查核结束运行该程序段时的状态是否和该主核结束运行该程序段时的状态相同,若不同则表示发生差错。

10.所述的控制运行时钟周期的处理器运行差错检测方法,其中该步骤2还包括:

11.每当提交加载指令,将该加载指令对应的加载地址与加载数据保存到当前该检查核对应的加载存储日志中,当写满该加载存储日志时,将主核当前状态作为检查点划分程序段。

12.所述的控制运行时钟周期的处理器运行差错检测方法,其中该主核的重命名部件中包括:当前状态表、检查点状态表、暂停队列;

13.其中该当前状态表,用于将记录当前逻辑寄存器所对应的物理寄存器;该检查点状态表,用于保存检查点的各个逻辑寄存器与物理寄存器的对应关系;该暂停队列,用于在将该主核状态复制给该检查核的过程中,暂停释放检查点状态中各物理寄存器,并将其保存在暂停队列中,直到复制结束再释放。

14.本发明还提出了一种控制运行时钟周期的处理器运行差错检测系统,其中包括:

15.初始模块,用于获取具有主核以及检查核的处理系统,且该主核与该检查核有相同的指令集架构;

16.预测模块,用于在该主核运行待执行程序时,根据该主核提交的指令种类和数量对程序段在该检查核的运行时钟周期进行预测,当该运行时钟周期大于阈值,则将该主核当前的状态作为检查点划分程序段;

17.检测模块,用于将该主核开始运行该程序段时的状态复制给该检查核,使该检查核以与该主核相同的状态开始运行,在该检查核运行该程序段的过程中,对于加载指令,直接访问该加载存储日志,获取加载数据作为加载结果,并判断该加载结果的地址是否和该加载存储日志中加载地址相同,若不同则表示产生差错;当该检查核结束运行该程序段,判断该检查核结束运行该程序段时的状态是否和该主核结束运行该程序段时的状态相同,若

不同则表示发生差错。

18.所述的控制运行时钟周期的处理器运行差错检测系统,其中该预测模块还用于:

19.每当提交加载指令,将该加载指令对应的加载地址与加载数据保存到当前该检查核对应的加载存储日志中,当写满该加载存储日志时,将主核当前状态作为检查点划分程序段。

20.所述的控制运行时钟周期的处理器运行差错检测方法,其中该主核的重命名部件中包括:当前状态表、检查点状态表、暂停队列;

21.其中该当前状态表,用于将记录当前逻辑寄存器所对应的物理寄存器;该检查点状态表,用于保存检查点的各个逻辑寄存器与物理寄存器的对应关系;该暂停队列,用于在将该主核状态复制给该检查核的过程中,暂停释放检查点状态中各物理寄存器,并将其保存在暂停队列中,直到复制结束再释放。

22.本发明还提出了一种存储介质,用于存储执行所述任意一种控制运行时钟周期的处理器运行差错检测方法的程序。

23.本发明还提出了一种数据处理装置,包括存储介质,当该数据处理装置的处理器调取并执行该计算机可读存储介质中的计算机可执行指令时,该数据处理装置执行控制运行时钟周期的处理器运行差错检测。

24.本发明还提出了一种客户端,用于所述的任意一种控制运行时钟周期的处理器运行差错检测系统。

25.由以上方案可知,本发明的优点在于:

26.本发明为了异构并行差错检测对高性能主核性能的影响,提出了复制寄存器时,暂停物理寄存器释放的方法,将检查点状态保存在物理寄存器堆中,从而无需主核暂停提交指令,降低了复制寄存器对高性能主核的影响。因此可以划分更小粒度的程序段,从而降低差错检测延时。

27.本发明对指令进行分类,统计各类指令所需的执行时间,根据指令的种类和数量对程序段在检查核的运行时间进行预测,并根据设定的时间划分程序段,从而降低最大差错检测延时,保障系统的实时性。

附图说明

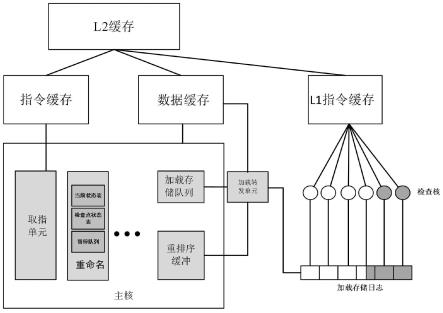

28.图1为本发明整体结构图;

29.图2为检查核的吞吐量与主核的匹配过程示意图;

30.图3为程序段在检查核的运行时间预测示意图;

31.图4为当前状态表、检查点状态表示意图;

32.图5为复制寄存器过程中暂停物理寄存器释放的过程图;

33.图6是本发明的数据处理装置示意图。

具体实施方式

34.乱序处理器会使用寄存器重命名技术,将逻辑寄存器指向各个物理寄存器。对于每条指令,重命名部件为其目的寄存器分配一个新的物理寄存器,用来保存它运算的结果,而之后与该条指令相依赖的指令,直接从其物理寄存器中获取数据,与其他有相同逻辑寄

存器的指令区别开,从而消除了指令之间的寄存器读后写相关(war)和写后写相关(waw),提高了指令运行的并行性。当一条指令提交时,其目的逻辑寄存器会指向分配给它的新的物理寄存器,来表示当前的状态,而原来的物理寄存器可以被释放,分配给其他指令,只有被分配的那条指令写回后才能够对该物理寄存器进行修改。因此在复制寄存器时,只要暂停检查点状态对应的物理寄存器的释放,就可以防止物理寄存器的值被接下来的指令所覆盖,从而将检查点状态保留在物理寄存器堆中,而不用暂停提交指令。

35.在研究过程中发现,某个程序段在顺序处理器核运行的时间与该程序段中的各种指令的数量呈一定的线性关系。因此本发明可将程序段中的指令进行分类,统计各类指令在检查核运行所需的时间。在主核运行的过程中,根据指令的种类和数量对程序段在检查核的运行时间进行预测,当预测的时间大于设定的值时,将其作为检查点划分程序段,控制检查核检查程序段的时间,减少差错检测的延时。为了实现上述技术效果,本发明包括如下关键技术点:

36.关键点1:本发明提出了复制寄存器时,暂停物理寄存器释放的方法,将检查点寄存器状态完整地保存在物理寄存器堆中,使得在复制物理寄存器中无需暂停提交指令,从而减少异构并行差错检测对主核性能的影响,从而允许设置更小的程序段,减小差错检测延时。

37.关键点2:本发明提出了根据预测的运行时间划分程序段的方法,使得各个程序段在检查核的运行时间都相对均匀,使得最大差错检测延时可控,以满足关键系统的实时性要求。

38.为让本发明的上述特征和效果能阐述的更明确易懂,下文特举实施例,并配合说明书附图作详细说明如下。

39.本文提出的低性能开销的异构并行差错检测的整体结构如图1所示,主要由一个高性能的乱序主核,多个低性能顺序检查核、加载转发单元、加载存储日志组成,并在乱序主核的重命名部件中增加了当前状态表、检查点状态表、暂停队列。

40.主核与检查核拥有相同的指令集架构,主核运行正常的程序,并将程序划分为多个程序段,交于检查核重复运行,进行差错检测,各个检查核有其单独的l0指令缓存,以及和其他检查核共享的l1指令缓存,l1指令缓存与主核的l2缓存相连接,从主核的l2缓存中获取所需的指令。

41.加载转发单元用于将加载指令取到的数据进行复制,当加载指令提交时,将其与加载存储队列中的数据进行比较,以防止将加载指令的错误传输到检查核中。具体来说,对于一条加载指令,正常的情况下,加载指令在执行的过程中,会从数据缓存中获取对应的数据,并将其保存在加载队列中。而本发明会将其从数据缓存中的数据同时保存在加载转发单元中。当指令提交时,我们需要将该条指令在加载队列中的数据拿出来,与加载转发单元中的数据进行比较,当两个数据相同时,则将其保存再加载存储日志中。从而保证加载存储日志中加载的数据的正确性。因此加载转发单元首先保存指令从缓存中获取的数据,当指令提交时,获得对应指令的序列号,根据序列号获取保存的对应的指令的数据,并将其与加载队列中的数据进行比较,从而保证加载存储日志中加载的数据的正确性。

42.对于加载指令,当其发射之后,加载执行单元会向数据缓存发送读请求,数据缓存会将对应地址的数据返回给处理器,保存在加载存储队列中。对于存储指令,当其需要存储

的数据准备好之后,会发射该存储指令,当指令发射时,会将所需要存储的数据保存在加载存储队列中。

43.加载存储日志用于保存主核提交的加载、存储指令对应的地址与数据。各个检查核有其独立的分区,能够并行访问,检查核在运行的过程中,对于加载、存储指令直接访问加载存储日志,对数据、地址进行比较以实现差错检测。

44.主核重命名部件中增加的当前状态表,用于将记录当前逻辑寄存器所对应的物理寄存器,检查点状态表用于保存检查点状态各个逻辑寄存器所对应的物理寄存器,暂停队列用于在复制寄存器的过程中,暂停检查点状态中各个物理寄存器被释放,并将暂停释放的寄存器保存在暂停队列中,等到复制寄存器结束,再被释放,以被其他的指令利用。

45.主核运行正常的程序,并将程序划分为多个程序段分别交给各个检查核重复运行以实现差错检测,由于检查核性能较低,因此存在多个检查核并行运行的过程,因此多个检查核的吞吐量能够匹配主核,其运行过程如图2所示。每一个程序段都为其分配一个检查核,在程序段的开始,将当前的状态复制给检查核,使得检查核能够以相同的状态开始运行。在程序段的结束,也将当前状态赋值给检查核,用于检查核对该程序段运行结束后对状态进行检查,令当前检查核开始运行,并为新的程序段分配一个新的检查核。

46.当主核运行时,每当提交加载、存储指令,需要将加载、存储的地址于数据保存到当前检查核对应的加载存储日志分区中,假如当前的加载存储日志分区装满时,则将当前状态作为检查点划分程序段。与此同时,根据提交的指令的种类和数量对程序段的运行时钟周期进行预测,当其大于设定的值,则将当前状态作为检查点划分程序段。

47.接下来结合实例介绍本发明预测程序段运行时间划分程序段的过程。

48.我们分析程序段,根据所需的运行时钟周期对指令种类进行划分,定点乘除运算、浮点运算密集的程序段,运行的时钟周期较长。为此可以将指令划分为定点乘法指令、定点除法指令、分支指令、跳转指令、浮点除法平方根指令、浮点加法乘法指令、浮点杂项指令、其他指令。其他指令包括算数逻辑指令、加载指令、存储指令等。加减、逻辑指令执行只需要一个周期,由于加载、存储指令直接从加载存储日志中获取数据,也没有延时,因此将它们划分到一起。随后分别以条指令作为程序段的划分,获取不同程序段里各种指令的数量和运行时钟周期,获取各钟指令运行需要的时间,各条指令的预测周期数都为整数。

49.对于检查核中的加载指令,我们需要使得它相比较于主核中的加载指令有相同的加载的数据,使得检查核与主核能够运行相同的程序段。故直接从加载存储日志中获取数据相比较于令检查核直接从缓存中获取数据,这种方式对主核的性能的影响较小。与此同时这也能够加快检查核运行程序段的速度。

50.根据统计的各条指令所需要的时间,对程序段在检查核的运行时间进行预测如图3所示。在主核运行的过程中,对于每种指令,都为其分配一个寄存器,用于记录该程序段已经提交的该种指令的数量。最后将各种指令的数量乘以其所需的运行时钟周期,并对其值进行累加以获得预测的程序段的运行时间。当预测的时钟周期大于设定的时钟周期则将当前状态作为检查点划分程序段。以此能够将最大差错检测的延时控制在一定的范围内。

51.对于每个程序段,检查核的运行分为3个阶段1)在程序段的开始,将主核程序计数器、通用寄存器、状态寄存器等状态,复制给检查核,使得检查核能够以与主核相同的状态开始运行;2)在检查核运行的过程中,对于加载指令,直接访问加载存储日志,获取所需要

的数据,并对地址进行比较,不同则表示产生差错。对于存储指令,对加载存储日志中的数据与地址进行比较,不同则表示产生差错。3)当程序段运行结束,则将检查核的状态与复制的程序段尾的状态进行比较,不同则表示产生差错。

52.接下来结合实例介绍本发明复制寄存器的过程。

53.本发明在乱序主核的重命名部件中增加了当前状态表、检查点状态表,其组织形式如图4所示。当前状态表中寄存器的数量等于逻辑寄存器的数量,每个寄存器记录了主核当前状态该逻辑寄存器所对应的物理寄存器,检查点状态表中寄存器的数量等于逻辑寄存器的数量,每个寄存器记录了主核当前状态该逻辑寄存器所对应的物理寄存器。每当指令提交时,修改当前状态表中,其目的逻辑寄存器中的寄存器使其为提交的物理寄存器。每当遇到检查点时,将当前状态表复制给检查点状态表。

54.在复制寄存器的过程中,查询检查点状态表来获取检查点状态逻辑寄存器所对应的物理寄存器,并读取寄存器堆中对应的物理寄存器值,以将检查点的寄存器状态复制给检查核。与此同时,主核无需暂停提交指令,当指令提交时,根据指令的逻辑目标寄存器,查询表中的物理目标寄存器,如果相等,则暂停其释放,将其放入暂停队列中,防止其被其他指令使用,确保检查点状态不会被覆盖。复制寄存器完成后,暂停队列中的寄存器会被释放到空闲列表中用于重命名。由于复制寄存器时无需暂停提交指令,本发明能够减小复制寄存器对主核性能的影响,从而允许设置更小的程序段,减少差错检测的延时。

55.图5给出了复制寄存器时物理寄存器释放的示例过程,当第一次释放逻辑寄存器l5对应的物理寄存器p36时,根据逻辑地址查找检查点状态逻辑寄存器对应的物理寄存器,发现相等,则暂停其物理寄存器释放。当再次释放l5时,由于为其分配了新的物理寄存器(p62),查表发现与检查点状态的物理寄存器不相等,可以将其物理寄存器释放。复制寄存器结束后,暂停队列中的物理寄存器会被释放到空闲列表中,用于接下来的重命名。

56.当检测发现差错时,可使用检查点技术,将主核的状态恢复到前一个检查点状态。也可以对主核进行重启,使其重新运行程序。也可以使用中断处理程序,使用中断处理程序来对差错进行处理。

57.本发明还提出了一种控制运行时钟周期的处理器运行差错检测系统,其中包括:

58.初始模块,用于获取具有主核以及检查核的处理系统,且该主核与该检查核有相同的指令集架构;

59.预测模块,用于在该主核运行待执行程序时,根据该主核提交的指令种类和数量对程序段在该检查核的运行时钟周期进行预测,当该运行时钟周期大于阈值,则将该主核当前的状态作为检查点划分程序段;

60.检测模块,用于将该主核开始运行该程序段时的状态复制给该检查核,使该检查核以与该主核相同的状态开始运行,在该检查核运行该程序段的过程中,对于加载指令,直接访问该加载存储日志,获取加载数据作为加载结果,并判断该加载结果的地址是否和该加载存储日志中加载地址相同,若不同则表示产生差错;当该检查核结束运行该程序段,判断该检查核结束运行该程序段时的状态是否和该主核结束运行该程序段时的状态相同,若不同则表示发生差错。

61.所述的控制运行时钟周期的处理器运行差错检测系统,其中该预测模块还用于:

62.每当提交加载指令,将该加载指令对应的加载地址与加载数据保存到当前该检查

核对应的加载存储日志中,当写满该加载存储日志时,将主核当前状态作为检查点划分程序段。

63.所述的控制运行时钟周期的处理器运行差错检测方法,其中该主核的重命名部件中包括:当前状态表、检查点状态表、暂停队列;

64.其中该当前状态表,用于将记录当前逻辑寄存器所对应的物理寄存器;该检查点状态表,用于保存检查点的各个逻辑寄存器与物理寄存器的对应关系;该暂停队列,用于在将该主核状态复制给该检查核的过程中,暂停释放检查点状态中各物理寄存器,并将其保存在暂停队列中,直到复制结束再释放。

65.本发明还提出了一种存储介质,用于存储执行所述任意一种控制运行时钟周期的处理器运行差错检测方法的程序。

66.如图6所示,本发明还提出了一种数据处理装置,包括存储介质,当该数据处理装置的处理器调取并执行该计算机可读存储介质中的计算机可执行指令时,该数据处理装置执行控制运行时钟周期的处理器运行差错检测。

67.本发明的计算机可读存储介质存储有计算机可执行指令,计算机可执行指令被数据处理装置的处理器执行时,实现上述共享主核控制流信息的异构并行差错检测方法。本领域普通技术人员可以理解上述方法中的全部或部分步骤可通过程序来指令相关硬件(例如处理器、fpga、asic等)完成,所述程序可以存储于可读存储介质中,如只读存储器、磁盘或光盘等。上述实施例的全部或部分步骤也可以使用一个或多个集成电路来实现。相应地,上述实施例中的各模块可以采用硬件的形式实现,例如通过集成电路来实现其相应功能,也可以采用软件功能模块的形式实现,例如通过处理器执行存储于存储器中的程序/指令来实现其相应功能。本发明实施例不限制于任何特定形式的硬件和软件的结合。

68.本发明还提出了一种客户端,用于所述的任意一种控制运行时钟周期的处理器运行差错检测系统。

69.以下为与上述方法实施例对应的系统实施例,本实施方式可与上述实施方式互相配合实施。上述实施方式中提到的相关技术细节在本实施方式中依然有效,为了减少重复,这里不再赘述。相应地,本实施方式中提到的相关技术细节也可应用在上述实施方式中。

70.综上,本发明提出了一种在复制寄存器的过程中暂停物理寄存器释放的方法,使得主核无需暂停提交指令,减小了复制寄存器对主核性能的影响,能够允许更小地划分程序段,从而减少差错检测的延时。与此同时,根据预测的运行时钟周期对程序段进行划分,使得最大差错检测延时可控,以满足关键系统实时性的要求。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。