1.本发明是涉及数据接收技术,尤其是涉及一种盲解卷积机制的数据接收装置及方法。

背景技术:

2.在低功率广域网络中,使用者对于低功耗的需求越来越高。特别是在物联网的应用下,大量使用装置需要连上网络。其中部分装置需要低数据量的传输搭配长时间的等待。当装置起始进行数据接收时,需要对数据进行盲解。当盲解所需的时间愈长,对于装置的功耗就会愈多。因此,如果装置能够具备更有效率而快速的盲解机制,将对于降低装置功耗有所助益。

技术实现要素:

3.鉴于先前技术的问题,本技术实施例提供一种具有加速盲解卷积机制的数据接收装置及方法,以改善先前技术。

4.为了解决上述技术问题,本技术是这样实现的:

5.本技术提供了一种盲解卷积机制的数据接收装置,包括:解扰(descrambler)电路、缓存电路、软信息处理电路以及后处理电路。解扰电路配置以对自天线接收的接收数据根据天线以及在传送周期内的n个数据位置假设进行解扰,以产生n组软比特数据,其中接收数据经由卷积编码程序产生,各n组软比特数据在传送周期内具有n个数据子区块,n个数据位置假设依序假设所述接收数据的第一数据子区块为第一原始数据子区块至第n原始数据子区块。缓存电路包括各具有单位编码长度的n个循环缓存器。软信息处理电路配置以撷取对应单位编码长度的比特位置资讯以决定多个不变比特位置以及多个变动比特位置,以进行盲解程序,包括:使缓存电路的n个循环缓存器对应n个数据位置假设,循环存储并叠加n组软比特数据产生n组叠加结果;以及在所假设的新的传送周期起始时使n个循环缓存器保留对应不变比特位置的数据,以及清除n个循环缓存器中对应变动比特位置的数据。后处理电路配置以对每一个数据子区块对应的n组叠加结果进行解交织(deinterleave)以及解码,以产生n组解码结果进行校验进而产生n个校验结果。其中当n个校验结果显示n组解码结果均未通过校验时,软信息处理电路持续进行盲解程序以使n个循环缓存器叠加n组软比特数据,且当n个校验结果显示任一n组解码结果通过校验时,软信息处理电路终止盲解程序。

6.本技术更提供了一种盲解卷积机制的数据接收方法,应用于数据接收装置中,包括:由解扰电路对自天线接收的接收数据根据天线以及在传送周期内的n个数据位置假设进行解扰,以产生n组软比特数据,其特征在于,接收数据经由卷积编码程序产生,各n组软比特数据在传送周期内具有n个数据子区块,n个数据位置假设依序假设所述接收数据的第一数据子区块为第一原始数据子区块至第n原始数据子区块;由软信息处理电路撷取对应单位编码长度的比特位置资讯以决定多个不变比特位置以及多个变动比特位置;由软信息

things;nb-iot)系统的窄频实体广播通道(narrowband physical broadcast channel;npbch)或是窄频实体下行链共享信道(narrowband physical downlink shared channel;npdsch)接收来自数据传送装置(未绘示)传送的接收数据rd。

21.接收数据rd可由数据传送装置执行的卷积编码程序产生。数据接收装置100将在起始接收到接收数据rd后对其进行盲解。

22.由于数据接收装置100的运作与数据传送装置执行的卷积编码程序相关,以下将以咬尾卷积码(tail-biting convolutional code;tbcc)的编码技术的特性为例,先说明卷积编码程序的进行方式。然而本发明并不限于此编码方式。

23.请参照图2。图2显示本发明的一实施例中,原始数据a经由编码流程产生编码完成的数据e的示意图。

24.如图2所示,原始数据a是长度为na

×

1的向量,亦即其为具有na个比特数的数据,并包括第一及第二待编码比特区段se1、se2。

25.于一数值范例中,第一待编码比特区段se1的长度为6比特,并包括例如,但不限于4比特的系统讯框编号(system frame number;sfn)及2比特超系统讯框编号(hyper sfn),其内容随着不同的周期变化而为变动比特。第二待编码比特区段se2的长度则为28比特,其内容长时间不变而为不变比特。因此,na为34。

26.在步骤s210中,原始数据a经由检查码添加程序添加第三待编码比特区段se3,例如长度为nb的侦错数据b,成为长度为nc

×

1的数据c。侦错数据b可由例如但不限于循环冗余校验实现,用于检验原始数据a的正确性。

27.于一实施例中,侦错数据b段由第一及第二待编码比特区段se1、se2运算产生,其内容随着不同的周期变化而为变动比特。此时,nc=na nb。于一数值范例中,第三待编码比特区段se3的长度为16比特。因此nb为16,nc为50。

28.在步骤s220中,数据c经由通道编码程序进行通道编码来对抗通道效应。

29.于一实施例中,数据传送装置可包括数目为l个(例如6个)的缓存器以及加法器,并借由上述元件实现编码率例如为1/3的咬尾卷积技术编码,产生3

×

nc且可由向量表示的数据d。然而本发明用以编码的编码率并不为此所限。因此,一个原始长度为50比特的数据在经过编码后,将产生总长度为150比特的数据,此150比特的长度在此定义为单位编码长度。

30.于一实施例中,编码是由第一待编码比特区段se1(6比特)及第二待编码比特区段se2中,邻接于第一待编码比特区段se1且长度相当于缓存器长度l的第一部分(6比特)产生。对各三路编码数据(d0、d1以及d2)而言,原先对应第一待编码比特区段se1(6比特)及第二待编码比特区段se2的变动比特将成为6 6=12比特,而不变比特则成为28-6=22。对应第三待编码比特区段se3的变动比特则仍为16比特。

31.在步骤s230中,数据d进行交织程序。

32.于一实施例中,窄频物联网系统以固定的交织演算法对数据d进行交织,并对于三路编码数据采用相同的交织方式,以产生一维且长度为3nc

×

1(仍为150比特的单位编码长度)并可由向量[v0,v1,v2]表示的数据v。举例而言,文献“evolved universal terrestrial radio access(e-utra);multiplexing and channel coding”中的5.1.4.2定义了适用于窄频物联网系统的交织方式。

[0033]

虽然变动比特以及不变比特经过交织而产生位置的变化且不再连续,但由于交织演算法是固定的,因此对于不同周期的数据而言,交织后的变动比特位置以及不变比特位置是相同的。并且,由于编码以及交织均分成三路进行,变动比特以及不变比特在上述个别三段各50比特的向量v0、v1以及v2中亦具有相同的对应位置。举例而言,对应第一段向量v0的22个不变比特如表示为unchangedpos_v=[u0,u1,

…

,u20,u21],则对应第二段向量v1以及第三段向量v2的不变比特将分别为unchangedpos_v 50以及unchangedpos_v 100。三段向量将共包括66比特的不变比特。

[0034]

于步骤s240中,数据v经过速率匹配程序以及加扰程序来把数据均匀地分配到所有可使用的资源单位,形成长度为ne

×

1的待传送数据e。

[0035]

请参照图3。图3显示本发明一实施例中,待传送数据e的结构示意图。图3所示的待传送数据e是以窄频实体广播通道的数据结构为例进行说明。然而本发明并不为此所限。

[0036]

待传送数据e的一个传送周期为640毫秒,以对应64个讯框。每8个讯框为一个原始数据子区块(sub-block),一个传送周期共有8个原始数据子区块sbo0~sbo7。前述具有单位编码长度为150比特的数据d在经过交织产生数据v后,将经由速率匹配到1600比特,每个原始数据子区块sbo0~sbo7对应此1600比特中的200比特,同一原始数据子区块中的不同讯框具有不同的扰码。

[0037]

数据接收装置100所接收到的接收数据rd将为待传送数据e。然而,数据接收装置100并无法得知其起始接收到的接收数据rd是待传送数据e的哪个原始数据子区块,而必须先进行盲解。

[0038]

请再次参照图1。以下将针对数据接收装置100中包括的元件以及运作进行说明。如图1所示,数据接收装置100包括:天线110、通道估测电路120、等化电路130、解扰(descrambler)电路140、缓存电路150、软信息处理电路160以及后处理电路170。

[0039]

天线110将自无线通道接收到接收数据rd。通道估测电路120以及等化电路130分别配置以对接收数据rd进行通道估测以及等化后传送至解扰电路140。

[0040]

解扰电路140配置以对接收数据rd根据天线110以及在传送周期内的n个数据位置假设进行解扰,以产生n组软比特数据。于一实施例中,软比特数据分别为对数似然比(log-likelihood ratio;llr)。

[0041]

各n个软比特数据在传送周期内具有n个数据子区块,n个数据位置假设依序假设接收数据rd在传送周期内的第一数据子区块为第一原始数据子区块至第n原始数据子区块。

[0042]

请参照图4a。图4a显示本发明一实施例中,对应不同数据位置假设的不同接收数据rd的示意图。

[0043]

对应图2中n为8的实施例,图4a绘示出8列分别对应8个数据位置假设的接收数据rd,并分别标示第1假设至第8假设。接收数据rd具有8个数据子区块sbd0~sbd7。

[0044]

第1列对应的第1假设是假设接收数据rd的第1个数据子区块sbd0是图2的第1原始数据子区块sbo0。第2列对应的第2假设是假设接收数据rd的第1个数据子区块sbd0是图2的第2原始数据子区块sbo1。

[0045]

依此类推,第8列对应的第8假设是假设接收数据rd的第1个数据子区块sbd0是图2的第8原始数据子区块sbo7。

[0046]

由于在一个传送周期结束后,数据接收装置100将接收到新一个传送周期的接收数据rd。因此,根据第2假设,第2列所绘示的接收数据rd在第8个数据子区块sbd8,将对应下一传送周期的第1原始数据子区块sbo0。根据第3假设,第3列所绘示的接收数据rd自第7个数据子区块sbd6起,将对应下一传送周期的第1及第2原始数据子区块sbo0、sbo1。

[0047]

依此类推,根据第8假设,第8列所绘示的接收数据rd自第2个数据子区块sbd1起,将对应下一传送周期的第1至第7原始数据子区块sbo0~sbo6。其中,所假设的下一传送周期的原始数据子区块是以虚线边框绘示来与前一传送周期的原始数据子区块的实线边框区别。

[0048]

由于每个原始数据子区块的加扰方式不同,解扰电路140将根据8个数据位置假设对接收数据rd解扰,产生8组软比特数据sd0~sd7。

[0049]

请参照图4b。图4b显示本发明一实施例中,软比特数据sd0~sd7的示意图。

[0050]

软比特数据sd0~sd7是分别根据图4a中对应8个数据位置假设的接收数据rd其中的一产生。如图4b所示,各软比特数据sd0~sd7包括解扰后的8个200比特的软比特数据子区块ds0~ds7。

[0051]

以软比特数据sd5为例,其对应的数据位置假设是对应图4a的第6假设。因此,软比特数据sd5的软比特数据子区块ds0同样被假设为第6原始数据子区块sbo5。而软比特数据子区块ds3~ds7起将对应下一传送周期的第1至第5原始数据子区块sbo0~sb04,并以虚线边框绘示。其他的软比特数据的结构可由相同的方式理解,在此不再赘述。

[0052]

请再次参照图1。缓存电路150包括各具有单位编码长度的n个循环缓存器。对应图2中n为8的实施例,缓存电路150包括8个循环缓存器rb0~rb7,且各具有为150比特的单位编码长度。

[0053]

软信息处理电路160配置以撷取对应单位编码长度的比特位置资讯bp以决定多个不变比特位置以及多个变动比特位置。

[0054]

比特位置资讯bp是由图2的步骤s230中进行的交织程序所使用的交织演算法产生。以不变比特位置为例,比特位置资讯bp可包括前述unchangedpos_v、unchangedpos_v 50以及unchangedpos_v 100共66个不变比特的位置资讯。

[0055]

于一实施例中,数据接收装置100可设置有运算电路(未绘示)以根据交织演算法计算得到比特位置资讯bp,再由软信息处理电路160撷取。于另一实施例中,数据接收装置100可设置有存储电路(未绘示)以存储已经计算好的比特位置资讯bp,再由软信息处理电路160撷取。本发明并不限于此。

[0056]

软信息处理电路160配置以进行盲解程序。盲解程序先使缓存电路150的8个循环缓存器rb0~rb7对应8个数据位置假设,分别循环存储并叠加8组软比特数据sd0~sd7产生叠加结果ar0~ar7。

[0057]

由于软比特数据sd0~sd7分别为对数似然比,因此叠加结果ar0~ar7即为此些对数似然比的资讯的合并。软信息处理电路160进而在所假设的新的传送周期起始时使n个循环缓存器保留对应不变比特位置的数据,以及清除n个循环缓存器中对应变动比特位置的数据。

[0058]

以下将以软比特数据sd5以及循环缓存器rb5为例,对循环缓存器循环存储及叠加软比特数据的过程进行说明。

[0059]

请参照图5a至图5d。图5a至图5d分别显示本发明一实施例中,软比特数据sd5以及循环缓存器rb5的示意图。

[0060]

软比特数据sd5包括8组各200比特的软比特数据子区块ds0~ds7。循环缓存器rb5为具有150比特长度的缓存器。

[0061]

如图5a所示,具有为150比特的单位编码长度的循环缓存器rb5将从第101个位置先存储第一个软比特数据子区块ds0的前50比特,再循环从头存储并叠加软比特数据子区块ds0的后150比特。

[0062]

如图5b所示,循环缓存器rb5继续循环从头存储并叠加第二组软比特数据子区块ds1的前150比特,再循环从头存储并叠加软比特数据子区块ds1的后50比特。

[0063]

如图5c所示,循环缓存器rb5从第51个位置继续存储并叠加第三组软比特数据子区块ds2的前100比特,再循环从头存储并叠加软比特数据子区块ds2的后100比特。

[0064]

如图5d所示,此时,所假设的下一传送周期已经开始。盲解程序在新的传送周期起始时使循环缓存器rb5保留对应不变比特位置的数据,以及清除n个循环缓存器中对应变动比特位置的数据。

[0065]

由于软比特数据子区块ds3是软比特数据sd5中对应的假设下新传送周期的开始,将会从循环缓存器rb5的起始位置开始存储。循环缓存器rb5将从头存储并叠加软比特数据子区块ds3的前150比特,再循环从头存储并叠加软比特数据子区块ds3的后50比特。后续的软比特数据子区块ds4~ds7将可依照上述方式由缓存电路150循环存储并叠加,在此不再赘述。

[0066]

须注意的是,由于软比特数据sd5是对应第6假设,而此假设是假设软比特数据子区块ds3为下一传送周期的开始而对应进行循环缓存器rb5的清除。对于其他的软比特数据(对应其他假设)来说,由于软比特数据子区块ds3并非其他假设中下一传送周期的开始,因此不需在处理软比特数据子区块ds3时清除相应的循环缓存器,而是在所述假设下的新传送周期开始时才清除相应的循环缓存器。

[0067]

请再次参照图1。后处理电路170包括解交织电路180、解码电路190以及校验电路195。

[0068]

解交织电路180配置以对每一个数据子区块对应的叠加结果ar0~ar7进行解交织(deinterleave)以产生解交织结果di0~di7。解码电路190配置以对解交织结果di进行解码以产生解码结果do0~do7。

[0069]

校验电路195对解码结果dr0~dr7进行校验以产生校验结果cr0~cr7传送至软信息处理电路160。软信息处理电路160将根据校验结果cr0~cr7判断解码结果dr0~dr7是否通过校验。

[0070]

当校验结果cr0~cr7显示解码结果dr均未通过校验时,软信息处理电路160持续进行盲解程序以使n个循环缓存器叠加n组软比特数据。当校验结果cr0~cr7显示任一组解码结果dr0~dr7通过校验时,软信息处理电路160终止盲解程序,软信息处理电路160输出通过校验的解码结果。举例而言,当解码结果dr5通过校验时,软信息处理电路160将判断对应图4a的第6假设为正确,而终止盲解程序。

[0071]

于不同实施例中,后处理电路170可采用不同的方式进行解交织、解码以及校验。本发明并不限制于特定的解交织、解码以及校验技术。

[0072]

须注意的是,上述的实施例均是以单一天线假设110为范例进行说明。于一实施例中,当天线数目的可能假设数为m,数据接收装置110包括的缓存电路150的数目将为m。解扰电路140须对m个天线假设以及n个数据位置假设进行解扰,以产生m

×

n组软比特数据。软信息处理电路160则使m个缓存电路150的n个循环缓存器分别循环存储并叠加m

×

n组软比特数据来产生叠加结果ar。

[0073]

在部分技术中,软信息处理电路在新的传送周期起始时会使缓存电路清除全部的资讯而不进行跨周期的资讯合并。在这样的情形下,盲解程序往往需要更多次的迭代才能完成盲解。

[0074]

本发明的数据接收装置可由软信息处理电路在新的传送周期起始时保留对应不变比特位置的数据,借由跨周期资讯合并来提高盲解成功的机率,进而降低盲解所需耗费的时间。

[0075]

请参照表1以及表2。仿真时设定天线数目的可能假设数m为2,信道类型为etu,多普勒扩展为5hz。表1以及表2显示本发明一实施例中,在不进行跨周期资讯合并以及进行跨周期合并的情形下成功盲解所需的迭代次数。表1为达到5%数据区块错误率(block error rate;bler)所需要的最少迭代次数。表格2为达到5%数据区块错误率时所需要的平均迭代次数。窄频实体广播通道的起始讯框在640毫秒的传送周期中的真实位置以及讯噪比的高低都会影响效能。

[0076]

表1

[0077]

表2

[0078]

其中对于真实位置在40且讯噪比为-12db时,即使达到最大迭代次数,不进行跨周期资讯合并的技术的数据区块错误率依然只能降到5.6%。从表1可以看到,讯噪比越低,本发明跨周期资讯合并的技术的改善越明显。因为在高讯噪比下,只需要很少的迭代次数就能解对,更不容易触发跨周期边界的条件。真实位置对改善幅度也有影响,因为真实位置不同,触发跨周期边界的机率也不同。同时,历史周期的讯框数所占比例也不同。在表1以及表2的情形下,本发明相对于不进行跨周期资讯合并的技术所需的最少迭代次数最多降低了十几次,最少降低0次。

[0079]

本发明相对不进行跨周期资讯合并的技术,新增的成本是用以存储不变比特位置的资讯的记忆体空间。在低讯噪比下,达到5%数据区块错误率的最少迭代次数最多可以节约十几次,平均迭代次数最多可以节约1.76次。对于窄频实体广播通道的盲解过程而言,如天线数目的可能假设数为2,数据位置假设为8,则一次迭代要尝试16种假设。减少一次迭代意味着大幅节省了16次解码。

[0080]

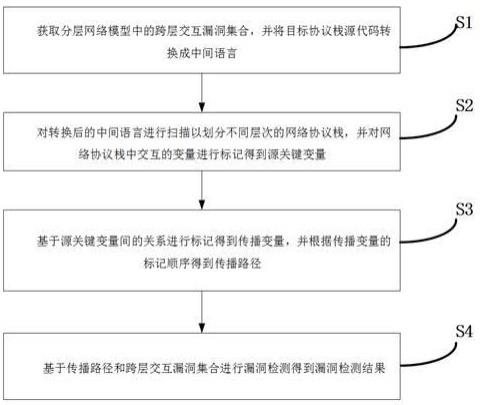

图6显示本发明一实施例中,一种具有加速盲解卷积机制的数据接收方法600的流程图。

[0081]

除前述装置外,本发明另揭露一种具有加速盲解卷积机制的数据接收方法600的流程图,应用于例如,但不限于图1的数据接收装置100中。数据接收方法600的的一实施例如图6所示,包括下列步骤。

[0082]

于步骤s610,由解扰电路140对自天线110接收的接收数据rd根据天线110以及在传送周期内的n个数据位置假设进行解扰,以产生n组软比特数据(例如软比特数据sd0~sd7)。

[0083]

于步骤s620,由软信息处理电路160撷取对应单位编码长度的比特位置资讯bp以决定多个不变比特位置以及多个变动比特位置。

[0084]

于步骤s630,由软信息处理电路160进行盲解程序。

[0085]

于步骤s640,盲解程序首先由软信息处理电路160使缓存电路150中各具有单位编码长度的n个循环缓存器对应n个数据位置假设,循环存储并叠加n组软比特数据产生n组叠加结果(例如叠加结果ar0~ar7)。

[0086]

于步骤s650,盲解程序接着由软信息处理电路160判断所假设的新的传送周期起始时使n个循环缓存器保留对应不变比特位置的数据,以及清除n个循环缓存器中对应变动比特位置的数据。

[0087]

于步骤s660,由后处理电路170对每一个数据子区块对应的n组叠加结果进行解交织以及解码,以产生n组解码结果(例如解码结果do0~do7)进行校验进而产生n个校验结果(例如校验结果cr0~cr7)。

[0088]

于步骤s670,判断n个校验结果显示任一n组解码结果是否通过校验。

[0089]

当n个校验结果显示n组解码结果均未通过校验时,软信息处理电路160回至步骤s630持续进行盲解程序以使n个循环缓存器叠加n组软比特数据。

[0090]

于步骤s680,当n个校验结果显示任一n组解码结果通过校验时,软信息处理电路160终止盲解程序。

[0091]

需注意的是,上述的实施方式仅为一范例。于其他实施例中,本领域的通常知识者当可在不违背本发明的精神下进行更动。

[0092]

综合上述,本发明中具有加速盲解卷积机制的数据接收装置及方法借由累积数据中固定不变的比特位置的资讯进行盲解,降低完成盲解的时间。

[0093]

虽然本案的实施例如上所述,然而所述些实施例并非用来限定本案,本技术领域具有通常知识者可依据本案的明示或隐含的内容对本案的技术特征施以变化,凡此种种变化均可能属于本案所寻求的专利保护范畴,换言的,本案的专利保护范围须视本说明书的申请专利范围所界定者为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。