1.本发明涉及通信技术领域,尤其涉及一种时钟同步电路、芯片及电子设备。

背景技术:

2.目前,由于标准以太网采用网线(power over ethernet,poe)传输方式更容易同时实现传输数据和对远端单元供电,且相比光纤传输系统有成本和易施工优势,在短距离无线通信系统传输中多采用标准以太网传输,所以在无线通信系统中就会同时存在光纤通信系统以及以太网通信系统。

3.标准以太网传输速率通常为10mb/s、100mb/s、1000mb/s、10000mb/s,标准以太网通信系统需要的参考时钟为25mhz的整数倍;而无线通信基站系统基带时钟速率为3.84mhz的整数倍,为了满足无线通信基站系统频率误差要求,提供给扩展单元和远端单元基带处理用的3.84mhz整数倍时钟必须和标准以太网传输系统的25mhz时钟同源。

4.现有技术中选用通用的双环锁相环芯片,无法通过第二级压控振荡器(voltage controlled oscillator,vco)整数分频同时得到25mhz和122.88mhz两个时钟信号,通常需要两套时钟方案级联实现,成本较高。

技术实现要素:

5.针对现有技术中存在的问题,本发明提供一种时钟同步电路、芯片及电子设备,实现同时输出标准以太网和无线通信系统同源的时钟信号,并降低设备成本。

6.本发明提供一种时钟同步电路,包括:第一锁相环电路、第二锁相环电路和第一分频器;

7.所述第一锁相环电路的第一端与输入端连接;

8.所述第一锁相环电路的第二端分别与所述第二锁相环电路的第一端和第一输出端连接;

9.所述第二锁相环电路的第二端与所述第一分频器的第一端连接;

10.所述第一分频器的第二端与第二输出端连接。

11.在一些实施例中,所述第一锁相环电路包括:第一压控振荡器、第一鉴相器、第二分频器和第三分频器;

12.所述第二分频器的第一端和所述第一压控振荡器的第二端连接;

13.所述第二分频器的第二端和所述第一鉴相器的第一端连接;

14.所述第三分频器的第一端和所述输入端连接;

15.所述第三分频器的第二端和所述第一鉴相器的第一端连接;

16.所述第一鉴相器的第二端和所述第一压控振荡器的第一端连接;

17.所述第一压控振荡器的第二端和所述第一输出端连接。

18.在一些实施例中,所述第二锁相环电路包括:第二压控振荡器、第二鉴相器、第四分频器和第五分频器;

19.所述第四分频器的第一端和所述第一压控振荡器的第二端连接;

20.所述第四分频器的第二端和所述第二鉴相器的第一端连接;

21.所述第五分频器的第一端和所述第二压控振荡器的第二端连接;

22.所述第五分频器的第二端和所述第二鉴相器的第一端连接;

23.所述第二鉴相器的第二端和所述第二压控振荡器的第一端连接。

24.在一些实施例中,所述第二压控振荡器的第二端和所述第一分频器的第一端连接。

25.在一些实施例中,所述第一压控振荡器为电压控制晶体振荡器。

26.在一些实施例中,所述第一分频器的数量为多个。

27.在一些实施例中,所述输入端输入的参考时钟频率是从网线的传输数据中恢复的。

28.在一些实施例中,所述输入端输入的参考时钟频率是从光纤的传输数据中恢复的。

29.本发明还提供一种芯片,包括上述任一种所述的时钟同步电路。

30.本发明还提供一种电子设备,包括上述任一种所述的芯片。

31.本发明提供的时钟同步电路、芯片、电子设备及时钟同步方法,通过接入单元、拓展单元以及远端单元时钟方案合理设计,采用单模拟pll,实现输出标准以太网时钟25mhz和无线通信系统时钟122.88mhz同源时钟,与传统时钟方案以及硬件架构一样,逻辑代码的时钟规划频率一样,极大的减少了逻辑代码开发工作量,并且模拟pll成本低廉,从而简化硬件电路并降低设备成本。

附图说明

32.为了更清楚地说明本发明或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

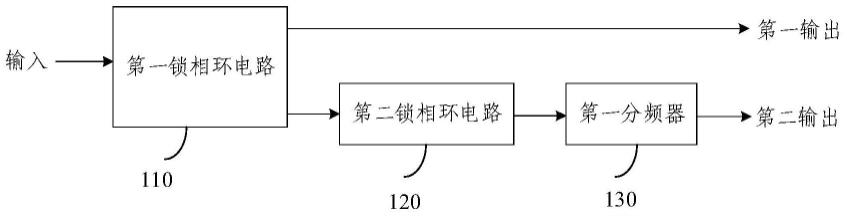

33.图1是本发明实施例提供的时钟同步电路的结构示意图之一;

34.图2是现有技术中无线通信系统的结构示意图;

35.图3是本发明实施例提供的时钟同步电路的结构示意图之二;

36.图4是本发明实施例提供的时钟同步电路的结构示意图之三。

具体实施方式

37.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明中的附图,对本发明中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.图1是本发明实施例提供的时钟同步电路的结构示意图之一,参考图1,本发明实施例提供的时钟同步电路,可以包括:第一锁相环电路、第二锁相环电路和第一分频器;

39.所述第一锁相环电路的第一端与输入端连接;

40.所述第一锁相环电路的第二端分别与所述第二锁相环电路的第一端和第一输出端连接;

41.所述第二锁相环电路的第二端与所述第一分频器的第一端连接;

42.所述第一分频器的第二端与第二输出端连接。

43.可选地,本发明实施例提供的时钟同步电路,包括:第一锁相环电路110、第二锁相环电路120和第一分频器130。

44.其连接关系如下:

45.第一锁相环电路110的第一端与输入端连接;

46.第一锁相环电路110的第二端分别与第二锁相环电路120的第一端和第一输出端连接;

47.第二锁相环电路120的第二端与第一分频器130的第一端连接;

48.第一分频器130的第二端与第二输出端连接。

49.需要说明的是,本发明实施例提供的时钟同步电路,应用于采用标准以太网传输无线通信小基站系统,实现扩展单元和远端单元的时钟与主机基带单元时钟同步。

50.可选地,在无线通信小基站系统中,主机单元与扩展单元通常采用光纤连接方式,便于长距离传输,扩展单元通过光纤中传输的数据,从数据中恢复时钟,从而实现主机单元和扩展单元的时钟同步。

51.远端单元和扩展单元采用poe传输方式,远端单元从拓展单元传输的标准以太网数据中恢复时钟,从而实现整个无线通信小基站系统的时钟同步。

52.图2是现有技术中无线通信系统的结构示意图,如图2所示,扩展单元与接入单元通过光纤连接,远端单元与扩展单元通过网线连接,扩展单元和远端单元中都有基带处理和以太网传输,都需要无线通信系统时钟122.88mhz和标准以太网时钟25mhz两类时钟源。

53.扩展单元从光纤恢复时钟,远端单元从网线恢复时钟,必须保证无线通信系统时钟122.88mhz和标准以太网时钟25mhz时钟同源,则整个系统时钟与基带单元的时钟同步。

54.可选地,锁相环(phase locked loop,pll)是一种利用相位同步产生的电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪。是无线电发射中使频率较为稳定的一种方法,主要有vco和锁相环集成电路(phase locked loop integrated circuit,pll ic),压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与pll ic所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则pll ic的电压输出端的电压发生变化,去控制vco,直到相位差恢复,达到锁相的目的。能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

55.(1)可选地,当本发明实施例提供的时钟同步电路应用于扩展单元时,时钟同步电路的输入为参考时钟频率,该参考时钟的频率是从光纤传输的数据中恢复的,参考时钟的频率为3.84mhz的整数倍,例如可以是153.6mhz。

56.将参考时钟的频率153.6mhz输入第一锁相环电路110中,得到第一锁相环电路输出的第一时钟频率,第一时钟频率与参考时钟的频率是同步的,即与无线通信系统的时钟频率是同步的。

57.第一时钟频率还同时作为第二锁相环电路120的输入,将第一时钟频率输入第二锁相环电路120中,得到第二锁相环电路输出的第二时钟频率。并通过第一分频器130对第二时钟频率进行分频,输出第三时钟频率。第三时钟频率与标准以太网系统的时钟频率是同步的。

58.通过以上方式在扩展单元得到了无线通信系统时钟122.88mhz和标准以太网时钟25mhz同源时钟,使得扩展单元与基带单元时钟同步。

59.(2)可选地,当本发明实施例提供的时钟同步电路应用于远端单元时,时钟同步电路的输入为参考时钟频率,该参考时钟的频率是从网线传输的数据中恢复的,参考时钟的频率为25mhz的整数倍,例如可以是25mhz。

60.将25mhz输入第一锁相环电路110中,得到第一锁相环电路输出的第一时钟频率,第一时钟频率与参考时钟的频率是同步的,即与标准以太网系统的时钟频率是同步的。

61.第一时钟频率还同时作为第二锁相环电路120的输入,将第一时钟频率输入第二锁相环电路120中,得到第二锁相环电路输出的第二时钟频率。

62.通过第一分频器130对第二时钟频率进行分频,输出第三时钟频率。第三时钟频率与与无线通信系统的时钟频率是同步的。

63.通过以上方式在远端单元得到了无线通信系统时钟122.88mhz和标准以太网时钟25mhz同源时钟,使得远端单元与扩展单元时钟同步。

64.本发明实施例提供的时钟同步电路,通过接入单元、拓展单元以及远端单元时钟方案合理设计,采用单模拟pll,实现输出标准以太网时钟25mhz和无线通信系统时钟122.88mhz同源时钟,与传统时钟方案以及硬件架构一样,逻辑代码的时钟规划频率一样,极大的减少了逻辑代码开发工作量,并且模拟pll成本低廉,从而简化硬件电路并降低设备成本。

65.在一些实施例中,所述第一锁相环电路包括:第一压控振荡器、第一鉴相器、第二分频器和第三分频器;

66.所述第二分频器的第一端和所述第一压控振荡器的第二端连接;

67.所述第二分频器的第二端和所述第一鉴相器的第一端连接;

68.所述第三分频器的第一端和所述输入端连接;

69.所述第三分频器的第二端和所述第一鉴相器的第一端连接;

70.所述第一鉴相器的第二端和所述第一压控振荡器的第一端连接;

71.所述第一压控振荡器的第二端和所述第一输出端连接。

72.可选地,第一锁相环电路可以包括:第一压控振荡器、第一鉴相器、第二分频器和第三分频器。

73.其连接关系如下:

74.第二分频器的第一端和第一压控振荡器的第二端连接;

75.第二分频器的第二端和第一鉴相器的第一端连接;

76.第三分频器的第一端和输入端连接;

77.第三分频器的第二端和第一鉴相器的第一端连接;

78.第一鉴相器的第二端和第一压控振荡器的第一端连接;

79.第一压控振荡器的第二端和第一输出端连接。

80.本发明实施例提供的时钟同步电路,通过将参考时钟频率输入第一锁相环电路,输出第一时钟频率,第一时钟频率与参考时钟频率同步,从而实现扩展单元与无线系统同步,或者远端单元与标准以太网系统同步。

81.在一些实施例中,所述第二锁相环电路包括:第二压控振荡器、第二鉴相器、第四分频器和第五分频器;

82.所述第四分频器的第一端和所述第一压控振荡器的第二端连接;

83.所述第四分频器的第二端和所述第二鉴相器的第一端连接;

84.所述第五分频器的第一端和所述第二压控振荡器的第二端连接;

85.所述第五分频器的第二端和所述第二鉴相器的第一端连接;

86.所述第二鉴相器的第二端和所述第二压控振荡器的第一端连接。

87.可选地,第二锁相环电路可以包括:第二压控振荡器、第二鉴相器、第四分频器和第五分频器。

88.其连接关系如下:

89.第四分频器的第一端和第一压控振荡器的第二端连接;

90.第四分频器的第二端和第二鉴相器的第一端连接;

91.第五分频器的第一端和第二压控振荡器的第二端连接;

92.第五分频器的第二端和第二鉴相器的第一端连接;

93.第二鉴相器的第二端和第二压控振荡器的第一端连接。

94.进一步地,所述第二压控振荡器的第二端和所述第一分频器的第一端连接。

95.本发明实施例提供的时钟同步电路,通过将第一锁相环电路输出的第一时钟频率输入第二锁相环电路,得到第二时钟频率。并通过第一分频器对第二时钟频率进行分频处理,输出第三时钟频率,可以实现扩展单元与标准以太网系统同步,或者远端单元与无线系统同步。

96.下面结合图3、图4以及具体实施例来详细说明本发明提供的时钟同步电路。

97.图3是本发明实施例提供的时钟同步电路的结构示意图之二,参考图3,详细说明扩展单元无线通信系统时钟122.88mhz和标准以太网时钟25mhz两类时钟同源的方法。

98.如图3所示:d1为第二分频器,r1为第三分频器,vcxo为第一压控振荡器,d1、r1、vcxo和第一鉴相器共同组成第一锁相环电路。

99.r2为第四分频器,d2为第五分频器,vco为第二压控振荡器,d2、r2、vco和第二鉴相器共同组成第二锁相环电路。

100.d为第一分频器,第一分频器的数量可以为多个。

101.各电路以及各器件的连接关系如图所示,在此不做赘述。

102.扩展单元锁相环芯片的第一级电压控制晶体振荡器(voltage controlled crystal oscillator,vcxo)采用122.88mhz,和光纤恢复的153.6mhz进行鉴相,使122.88mhz vcxo与恢复时钟同步。

103.该122.88mhz通过锁相环芯片的第一级时钟输出管脚输出,或通过第二级锁相环旁路功能从第二级时钟输出管脚输出,提供给基带处理部分使用。

104.下文将详细描述算法实现过程:

105.假设输入参考时钟为clk_ref_in,第一级参考分频为r1,第一级vcxo,第一级vcxo

参考分频为d1,第二级参考时钟为第一级的vcxo输出,第二级参考分频为r2,第二级vco,第二级vco参考分频为d2,根据锁相环的工作原理,需要满足下列公式:

[0106][0107]

为了实现同时输出无线通信系统时钟和标准以太网时钟两类时钟同源方法,需要将vcxo作为第二级pll的输入,同时需要满足下列公式:

[0108][0109]

无线通信系统中从基带中恢复的参考时钟clk_ref_in=153.6mhz,vcxo=122.88mhz,通过选取r1=120,d1=96,公式(1)计算出来的公约数为1.28mhz。

[0110]

vcxo=122.88mhz,vco=3000mhz,通过选取r2=128,d2=96,公式(2)计算出来的公约数为0.96mhz,通过将vco时钟输出分频器系数设置为120,得到25mhz时钟,提供给以太网器件。

[0111]

通过以上方式在扩展单元得到了无线通信系统时钟122.88mhz和标准以太网时钟25mhz同源时钟,使得扩展单元与基带单元时钟同步。

[0112]

通过更换vcxo的频率为30.72mhz、61.44mhz可以得到其它可被基带处理部分接受的时钟频率。

[0113]

通过将vco时钟输出分频器设置为60、24,分别得到50mhz和125mhz以太网器件接受的时钟频率。

[0114]

图4是本发明实施例提供的时钟同步电路的结构示意图之三,参考图4,详细说明远端单元无线通信系统时钟122.88mhz和标准以太网时钟25mhz两类时钟同源的方法。

[0115]

如图4所示:d1为第二分频器,r1为第三分频器,vcxo为第一压控振荡器,d1、r1、vcxo和第一鉴相器共同组成第一锁相环电路。

[0116]

r2为第四分频器,d2为第五分频器,vco为第二压控振荡器,d2、r2、vco和第二鉴相器共同组成第二锁相环电路。

[0117]

d为第一分频器,第一分频器的数量可以为多个。

[0118]

各电路以及各器件的连接关系如图所示,在此不做赘述。

[0119]

以太网器件从标准网线数据中恢复出25mhz时钟,锁相环芯片的第一级vcxo频率采用25mhz,和以太网器件恢复出来的25mhz频率进行鉴相,使25mhz vcxo与恢复时钟同步。

[0120]

该25mhz时钟通过锁相环芯片的第一级时钟输出管脚输出,或通过第二级锁相环旁路功能从第二级时钟输出管脚输出,提供给以太网器件使用。

[0121]

下文将详细描述算法实现过程:

[0122]

无线通信系统中从基带中恢复的参考时钟clk_ref_in=25mhz,vcxo=25mhz,通过选取r1=25,d1=25,公式(1)计算出来的公约数为1mhz。

[0123]

vcxo=25mhz,vco=3072mhz,通过选取r2=25,d2=3072,公式(2)计算出来的公约数为1mhz,通过将vco时钟输出分频器系数设置为100,得到30.72mhz时钟,提供给以太网器件。

[0124]

通过以上方式在远端单元得到了无线通信系统时钟122.88mhz和标准以太网时钟25mhz同源时钟,使得远端单元与扩展单元时钟同步。

[0125]

通过更换vcxo的频率为50mhz、125mhz或156.25mhz得其它可被以太网芯片接受的时钟频率。

[0126]

通过将第二级时钟输出分频器设置为160、100、50,分别得到19.2mhz、30.72mhz和61.44mhz能被基带处理部分接受的时钟频率。

[0127]

需要说明的是,图3和图4仅为其中一种实施例,上述描述中通过更改vcxo频率或者更改分频系数可以输出无线通信系统时钟19.2mhz、30.72mhz和61.44mhz和标准以太网时钟25mhz、50hmz、125mhz。

[0128]

本发明实施例提供的时钟同步电路,通过接入单元、拓展单元以及远端单元时钟方案合理设计,采用单模拟pll,实现输出标准以太网时钟25mhz(或25mhz整数倍)和无线通信系统时钟122.88mhz(或3.84mhz整数倍)同源时钟,具有以下有益效果:

[0129]

1、与传统时钟方案以及硬件架构一样,逻辑代码的时钟规划频率一样,极大的减少了逻辑代码开发工作量。

[0130]

2、模拟pll成本低廉,而且可以克服数字pll小数分频杂散,影响相躁指标的不足。

[0131]

本发明还提供一种芯片,包括上述实施例的时钟同步电路。

[0132]

本发明还提供一种电子设备,包括上述实施例的芯片。

[0133]

以上所描述的装置实施例仅仅是示意性的,其中所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。本领域普通技术人员在不付出创造性的劳动的情况下,即可以理解并实施。

[0134]

本发明实施例中术语“第一”、“第二”等是用于区别类似的对象,而不用于描述特定的顺序或先后次序。应该理解这样使用的术语在适当情况下可以互换,以便本技术的实施例能够以除了在这里图示或描述的那些以外的顺序实施,且“第一”、“第二”所区别的对象通常为一类,并不限定对象的个数,例如第一对象可以是一个,也可以是多个。

[0135]

通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到各实施方式可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件。基于这样的理解,上述技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品可以存储在计算机可读存储介质中,如rom/ram、磁碟、光盘等,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行各个实施例或者实施例的某些部分所述的方法。

[0136]

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。