1.本揭露涉及一种电子装置,尤其涉及一种可提高产品的良率的电子装置。

背景技术:

2.电子装置或拼接电子装置已广泛地应用于行动电话、电视、监视器、平板电脑、车用显示器、穿戴装置以及台式电脑中。随电子装置蓬勃发展,对于电子装置的质量要求越高,且这类电子产品通常可同时作为电子调制装置来使用,例如,作为可调制电磁波的天线装置。然而,现存的天线装置仍未在各个方面皆符合消费者的需求。

技术实现要素:

3.本揭露是提供一种电子装置,其可提高产品的良率(yield)。

4.根据本揭露的实施例,电子装置包括多个单元,且各个单元包括整合基板。整合基板包括第一介电层、第一导电层、第二介电层以及第二导电层。第一介电层具有第一侧以及与第一侧相对的第二侧。第一导电层设置于第一侧上。第二介电层具有面向第二侧的第三侧以及与第三侧相对的第四侧。第二导电层设置于第四侧上。第一介电层与第二介电层中的至少一个的损耗正切小于或等于0.1且大于0。

5.根据本揭露的实施例,电子装置包括多个导电结构。各个导电结构包括第三介电层、通孔、第三导电层、开口以及第四导电层。通孔设置于第三介电层中。第三导电层设置于第三介电层上。开口设置于第三导电层中。第四导电层设置于第三导电层上。第四导电层直接接触第三导电层的顶面并穿过开口。

附图说明

6.包含附图以便进一步理解本揭露,且附图并入本说明书中并构成本说明书的一部分。附图说明本揭露的实施例,并与描述一起用于解释本揭露的原理。

7.图1为本揭露一实施例的电子装置的功能示意图;

8.图2a至图2f为本揭露一实施例的电子装置的制造方法的剖面示意图;

9.图3为图2f的电子装置的上视示意图;

10.图4为本揭露另一实施例的电子装置的上视示意图;

11.图5a至图5d为本揭露多个实施例的导电结构的局部上视示意图。

12.附图标号说明

13.10、20、20a:电子装置;

14.11:基频电路;

15.13:相位阵列天线;

16.15:天线元件;

17.110:数字类比转换器;

18.120:类比数字转换器;

19.140:中频电路;

20.141、145、166:滤波器;

21.142、146:放大器;

22.143、161:混频器;

23.144、162:本地震荡器;

24.145:槽孔;

25.160:射频电路;

26.163:相移器;

27.164:功率放大器;

28.165:双工器;

29.167:低噪声放大器;

30.22:单元;

31.24、24a、24b、24c、24d:导电结构;

32.202:整合基板;

33.202a:第一组件;

34.202b:第二组件;

35.202c:第三组件;

36.210:第一介电层;

37.211:第一侧;

38.212:第二侧;

39.220、220a:第一导电层;

40.230:第二介电层;

41.231:第三侧;

42.232:第四侧;

43.240:第二导电层;

44.250:第三介电层;

45.251:第五侧;

46.252:第六侧;

47.254:通孔;

48.260、260a:第三导电层;

49.261:顶面;

50.262、263、2852、2853:缺口;

51.265:开口;

52.270、271、271a:第四导电层;

53.275:焊球;

54.280:导体;

55.285、285a:底部导电层;

56.2851:表面;

57.290:第四介电层;

58.300:晶片;

59.310:接垫;

60.is1、is2、is3:第一绝缘层;

61.op1、op2、op3、op4、op5:开口;

62.p:间距;

63.t1、t2:总厚度;

64.vb:偏压迹线。

具体实施方式

65.通过参考以下的详细描述并同时结合附图可以理解本揭露,须注意的是,为了使读者能容易了解及为了附图的简洁,本揭露中的多张附图只绘出电子装置的一部分,且附图中的特定元件并非依照实际比例绘图。此外,图中各元件的数量及尺寸仅作为示意,并非用来限制本揭露的范围。

66.在下文说明书与权利要求中,“含有”与“包括”等词为开放式词语,因此其应被解释为“含有但不限定为

…”

之意。

67.应了解到,当元件或膜层被称为在另一个元件或膜层“上”或“连接到”另一个元件或膜层时,它可以直接在此另一元件或膜层上或直接连接到此另一元件或层,或者两者之间存在有插入的元件或膜层(非直接情况)。相反地,当元件被称为“直接”在另一个元件或膜层“上”或“直接连接到”另一个元件或膜层时,两者之间不存在有插入的元件或膜层。

68.虽然术语“第一”、“第二”、“第三

”…

可用以描述多种组成元件,但组成元件并不以此术语为限。此术语仅用于区别说明书内单一组成元件与其他组成元件。权利要求中可不使用相同术语,而依照权利要求中元件宣告的顺序以第一、第二、第三

…

取代。因此,在下文说明书中,第一组成元件在权利要求中可能为第二组成元件。

69.于文中,“约”、“大约”、“实质上”、“大致上”的用语通常表示在一给定值或范围的10%内、或5%内、或3%之内、或2%之内、或1%之内、或0.5%之内。在此给定的数量为大约的数量,亦即在没有特定说明“约”、“大约”、“实质上”、“大致上”的情况下,仍可隐含“约”、“大约”、“实质上”、“大致上”的含义。

70.在本揭露中,长度、宽度、厚度、高度或面积、或元件之间的距离或间距的测量方式可以是采用光学显微镜(optical microscopy,om)、扫描式电子显微镜(scanning electron microscope,sem)、薄膜厚度轮廓测量仪(α-step)、椭圆测厚仪、或其它合适的方式测量而得,详细而言,根据一些实施例,可使用扫描式电子显微镜取得包含欲测量的元件的剖面结构图像,并测量各元件的宽度、厚度、高度或面积、或元件之间的距离或间距,但不以此为限。

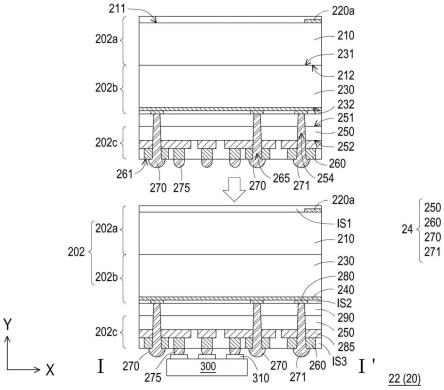

71.在本揭露一些实施例中,关于接合、连接的用语例如“连接”、“互连”等,除非特别定义,否则可指两个结构是直接接触,或者亦可指两个结构并非直接接触,其中有其它结构设于此两个结构之间。且此关于接合、连接的用语亦可包括两个结构都可移动,或者两个结构都固定的情况。此外,用语“耦接”包含任何直接及间接的电性连接手段。

72.本揭露的电子装置可包括显示装置、背光装置、天线装置、感测装置或拼接装置,但不以此为限。电子装置可为可弯折或可挠式电子装置。显示装置可为非自发光型显示装

置或自发光型显示装置。天线装置可为液晶型态的天线装置或非液晶型态的天线装置,感测装置可为感测电容、光线、热能或超声波的感测装置,但不以此为限。电子元件可包括被动元件与主动元件,例如电容、电阻、电感、二极管、晶体管等。二极管可包括发光二极管或光电二极管。发光二极管可例如包括有机发光二极管(organic light emitting diode,oled)、次毫米发光二极管(mini led)、微发光二极管(micro led)或量子点发光二极管(quantum dot led),但不以此为限。拼接装置可例如是显示器拼接装置或天线拼接装置,但不以此为限。需注意的是,电子装置可为前述的任意排列组合,但不以此为限。下文将以天线装置作为电子装置或拼接装置以说明本揭露内容,但本揭露不以此为限。

73.须知悉的是,以下所举实施例可以在不脱离本揭露的精神下,可将数个不同实施例中的特征进行替换、重组、混合以完成其他实施例。各实施例间特征只要不违背发明精神或相冲突,均可任意混合搭配使用。

74.现将详细地参考本揭露的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

75.图1为本揭露一实施例的电子装置的功能示意图。请参照图1,本实施例的电子装置10可视为是天线装置,包括基频电路(baseband circuit)11与相位阵列天线(phase array antenna)13。

76.具体来说,在本实施例中,相位阵列天线13可例如是采用类比波束成形(analog beamforming)技术,但不以此为限。其中,相位阵列天线13可包括多个单元22(图1示意地以1个天线为例),且多个单元22以阵列排列的方式配置(未示出)。各个单元22包括数字类比转换器110、类比数字转换器120、中频电路(intermediate frequency circuit)140、射频电路(radio frequency circuit)160以及天线元件15。中频电路140包括滤波器(filter)141、放大器(amplifier)142、混频器(mixer)143、本地震荡器(local oscillator)144、滤波器145以及放大器146。射频电路160包括混频器161、本地震荡器162、相移器(phase shifter)163、功率放大器(power amplifier)164、双工器(diplexer)165、滤波器166以及低噪声放大器(low noise amplifier)167。

77.在本实施例中,在电子装置10发射信号时,基频电路11可先通过单元22中的数字类比转换器110将低频数字信号转换成低频类比信号,并传递至中频电路140;接着,通过中频电路140中的滤波器141、放大器142、混频器143、本地震荡器144、滤波器145以及放大器146将低频类比信号转换成中频类比信号,并传递至射频电路160;接着,通过射频电路160中的混频器161、本地震荡器162、相移器163、功率放大器164以及双工器165将中频类比信号转换成高频类比信号,并传递至天线元件15;然后,通过天线元件15将高频类比信号(即,电磁波)发射至外界。

78.反之,在电子装置10接收信号时,先利用天线元件15接收来自外界的电磁波,并传递至单元22中的射频电路160;接着,通过射频电路160将高频类比信号转换成中频类比信号,并传递至中频电路140;接着,通过中频电路140将中频类比信号转换成低频类比信号,并传递至类比数字转换器120;然后,通过类比数字转换器120将低频类比信号转换成低频数字信号,并传递至基频电路11。

79.在一些实施例中,相位阵列天线也可以是采用数字波束成形(digital beamforming)技术(未示出),此时,相位阵列天线中的各个单元则可包括数字类比转换器、

类比数字转换器、功率放大器、双工器、滤波器以及低噪声放大器。

80.图2a至图2f为本揭露一实施例的电子装置的制造方法的剖面示意图。图3为图2f的电子装置的上视示意图。图2f为图3的电子装置沿剖面线

ⅰ‑ⅰ’

的剖面示意图。为了附图清楚及方便说明,图3省略示出电子装置20中的若干元件。

81.请先参照图2f与图3,本实施例的电子装置20包括多个单元22(图2f示意地以1个单元为例),单元22包含导电结构24(图2f示意地以1个导电结构为例)以及晶片300。具体来说,各个单元22包括整合基板202。整合基板202包括第一介电层210、第一导电层220a、第二介电层230以及第二导电层240。第一介电层210具有第一侧211以及与第一侧211相对的第二侧212。第一导电层220a设置于第一侧211上。第二介电层230具有面向第二侧212的第三侧231以及与第三侧231相对的第四侧232。第二导电层240设置于第四侧232上。由于第一介电层210与第二介电层230中的至少一个介电层的损耗正切(loss tangent)df小于或等于0.1且大于0(即0《df≦0.1),因而可以减少电磁波在第一介电层210与第二介电层230中的损耗,进而可使电磁波的发射效率较佳。

82.此外,各个导电结构24包括第三介电层250、通孔254、第三导电层260、开口265以及第四导电层270、271。第三介电层250具有面向第四侧232的第五侧251以及与第五侧251相对的第六侧252。通孔254设置于第三介电层250中。第三导电层260设置于第三介电层250上且设置于第六侧252上。开口265设置于第三导电层260中。第四导电层270、271设置于第三导电层260上。第四导电层270、271直接接触第三导电层260的顶面261并穿过开口265。其中,多个第四导电层270可围绕晶片300,且可用来将接地信号传送至第二导电层240。于其它实施例中,多个第四导电层270可不围绕晶片300。

83.在本实施例中,各个导电结构24还包括导体280、底部导电层285以及第四介电层290。导体280设置于第四介电层290上。导体280电性连接至第四导电层270、271。底部导电层285设置于第三介电层250与第三导电层260之间。底部导电层285可直接接触第三导电层260。第四介电层290与第三介电层250结合。

84.在本实施例中,方向x与电子装置20的法线方向y为不同方向,方向x垂直于法线方向y,且方向x大致上为剖面线

ⅰ‑ⅰ’

的的延伸方向,但不以此为限。

85.另外,在本实施例中,在电子装置20的法线方向y上,第三导电层260的形状可对应于第四导电层270、271的形状,第三导电层260的形状可以为封闭的环形或是有缺口的环形,且第四导电层270、271的形状可以为实心的图形。举例来说,如图3所示,在电子装置20的上视图中,第三导电层260的外轮廓例如是圆形,且第四导电层270与第四导电层271的外轮廓也对应地是圆形,但不以此为限。在本实施例中,第三导电层260的形状(或底部导电层285的形状)可以限制第四导电层270、271的形状及其范围,以使第四导电层270、271于制作时可以被限制在第三导电层260的形状的范围内(或在底部导电层285的形状的范围内),以减少第四导电层270、271于制作时有溢出于第三导电层260的形状的范围外(或底部导电层285的形状的范围外)的问题。在本实施例中,第四导电层270的形状可大致上相同于第四导电层271的形状,但不以此为限。在一些实施例中,第四导电层270的形状也可不同于第四导电层271的形状,如图5a至图5d所示。

86.请再参照图3,第二导电层240具有槽孔(slot)145,且槽孔145可对应于第一导电层220a设置。多个第四导电层271可围绕槽孔145以及天线元件15,以用来防止电磁干扰

(electromagnetic interference,emi),并确保来自晶片300所输出的信号质量。其中,所述电磁干扰例如是来自其他迹线(trace)所泄漏出的电磁波。在本实施例中,多个第四导电层271彼此分离,且相邻的两个第四导电层271之间具有间距p。其中,间距p为其中一个第四导电层271的中心至相邻的另一个第四导电层271的中心的距离。在本实施例中,间距p可例如是小于在底部导电层285与第二导电层240之间传递的电磁波的波长w1的一半,即p《1/2

×

w1,但不以此为限。

87.本实施例的电子装置20还包括偏压迹线(voltage bias trace)vb与导电层287。偏压迹线vb可以作为射频电路的信号线、中频电路的信号线、电源线或高速数字信号线(high speed digital signal line)。偏压迹线vb可以为单层或多层结构,且其材料可例如是包括铜、银、金、铝、锡、合金(例如:化镀镍金(enig))或前述的组合,但不以此为限。导电层287可将来自晶片300所输出的信号(例如是高频信号)传送至槽孔145,进而再将信号偶合(coupling)至第一导电层220a。

88.在本实施例中,一个晶片300可对应于一个天线元件15,但不以此为限。在一些实施例中,一个晶片300也可对应于多个天线元件15(未示出)。此外,在本实施例中,晶片300并未对应于第一导电层220a设置,且晶片300在电子装置20的法线方向y上并未重叠于第一导电层220a,但不以此为限。在一些实施例中,晶片也可以对应于第一导电层设置(未示出),且晶片在电子装置的法线方向上也可以重叠于第一导电层(未示出)。

89.请参照图2a至图2f,以下将针对本实施例的电子装置20的制造方法进行说明。其中,本实施例的电子装置20的制造方法以其中一单元22为例,可例如是包括但不限于以下步骤:

90.首先,请参照图2a,形成第一组件202a。具体来说,形成第一组件202a可例如是包括以下步骤:形成第一介电层210,其中第一介电层210具有第一侧211以及与第一侧211相对的第二侧212。第一介电层210的材料可例如是玻璃、印刷电路板(pcb)、低温共烧陶瓷(low temperature co-fired ceramic,ltcc)、液晶聚合物(liquid crystal polymer,lcp)、聚酰亚胺(polyimide,pi)、陶瓷、塑料薄膜(例如:环烯烃聚合物(cyclo olefin polymer,cop)、聚萘二甲酸乙二醇酯(polyethylene naphthalate,pen))、其它合适的介电材料、或前述的组合,但不以此为限。接着,形成第一导电层220于第一侧211上,并对第一导电层220进行图案化,以暴露出部分的第一介电层210,并形成经图案化的第一导电层220a。接着,形成第一绝缘层is1于第一导电层220a上,以覆盖第一导电层220a与由第一导电层220a暴露出的部分的第一介电层210。至此,已制作完成第一组件202a。

91.接着,请参照图2b,形成第二组件202b。具体来说,形成第二组件202b可例如是包括以下步骤:形成第二介电层230,其中第二介电层230具有第三侧231以及与第三侧231相对的第四侧232。第二介电层230的材料可例如是玻璃、印刷电路板(pcb)、低温共烧陶瓷(low temperature co-fired ceramic,ltcc)、液晶聚合物(liquid crystal polymer,lcp)、聚酰亚胺(polyimide,pi)、陶瓷、塑料薄膜(例如:环烯烃聚合物(cyclo olefin polymer,cop)、聚萘二甲酸乙二醇酯(polyethylene naphthalate,pen))、其它合适的介电材料、或前述的组合,但不以此为限。第一介电层和第二介电的层材料可以相同也可以不同。接着,形成第二导电层240于第四侧232上,并形成经图案化的第二绝缘层is2于第二导电层240上。第二绝缘层is2具有开口op1,以暴露出部分的第二导电层240。接着,形成导体

280于开口op1内,以使导体280可接触第二导电层240。至此,已制作完成第二组件202b。

92.接着,请参照图2c,形成第三组件202c。具体来说,形成第三组件202c可例如是包括以下步骤:形成第三介电层250,其中第三介电层250具有第五侧251以及与第五侧251相对的第六侧252。接着,形成经图案化的底部导电层285于第六侧252上,并形成经图案化的第三绝缘层is3于底部导电层285上。底部导电层285具有开口op2与开口op3,以暴露出部分的第三介电层250。第三绝缘层is3可设置于开口op3内,且具有开口op4与开口op5。开口op4对应于开口op2设置,且开口op4与开口op5可暴露出部分的底部导电层285远离第三介电层250的表面2851。接着,可选择地形成经图案化的第三导电层260于开口op4与开口op5内,以使第三导电层260设置在由开口op4与开口op5所暴露出的部分的底部导电层285的表面2851上。其中,底部导电层285可设置于第三介电层250与第三导电层260之间。第三导电层260可直接接触底部导电层285,以防止底部导电层285氧化。第三导电层260具有开口265,以连通开口op2。至此,已制作完成第三组件202c。

93.接着,请参照图2d,将第一组件202a接合至第二组件202b,以使第二组件202b中的第二介电层230的第三侧231可以面向第一组件202a中的第一介电层210的第二侧212,并使第三侧231可以与第二侧212结合。接着,形成第四介电层290于第二绝缘层is2远离第二导电层240的表面上,以使第四介电层290可覆盖导体280与第二绝缘层is2。在本实施例中,第三侧231可例如是通过胶体(未示出)并例如是以热压合制程(thermal compression process)直接粘附至第二侧212,但不以此为限。在本实施例中,第一介电层210与第二介电层230的总厚度t1可例如是小于电子装置20发射的电磁波的波长w2的一半且大于100微米(μm),即100μm《t1《1/2

×

w2,但不以此为限。其中,总厚度t1例如是第一介电层210与第二介电层230沿着电子装置20的法线方向y进行测量到的厚度。

94.在一些实施例中,第三侧231可例如是通过框胶(spacer)(未示出)并例如是以单滴填充(one drop filling,odf)制程间接接合至第二侧212,此时,在第二侧212、第三侧231以及框胶之间可具有间隙(未示出)。其中,所述间隙可以是空气间隙或真空间隙,也可以填入固体材料(例如胶体或粘着片)或液体(例如水),但不以此为限。所述间隙的厚度可例如是小于电子装置20发射的电磁波的波长w2的四分之一,即间隙的厚度《1/4

×

w2,但不以此为限。

95.接着,请参照图2e,将第三组件202c接合至第四介电层290,以使第三组件202c中的第三介电层250可与第四介电层290结合,并使第三介电层250的第五侧251可面向第二介电层230的第四侧232。接着,形成通孔254于第三介电层250与第四介电层290中,以使通孔254可连通开口op2与开口265并暴露出导体280。在本实施例中,通孔254的形成方法可例如是包括雷射钻孔、机械钻孔或化学蚀刻,但不以此为限。在本实施例中,第三介电层250与第四介电层290的总厚度为t2,且总厚度t1与总厚度t2的比值可例如是在2至20之间,即2≤t1/t2≤20,但不以此为限。其中,总厚度t2例如是第三介电层250与第四介电层290沿着电子装置20的法线方向y进行测量到的厚度。

96.接着,请参照图2f,形成第四导电层270、271与焊球275于第三导电层260远离第三介电层250的顶面261上,并形成第四导电层270、271于开口op2、开口265以及通孔254内,以使第四导电层270、271可电性连接至导体280,并使第四导电层270、271可通过导体280电性连接至第二导电层240。第四导电层270、271可直接接触第三导电层260的顶面261。在本实

施例中,第四导电层270、271的形成方法可例如是包括锡喷涂、电镀、溅镀或网版印刷(screen printing),但不以此为限。接着,设置晶片300于第三导电层260的顶面261上。晶片300具有接垫310,且晶片300可通过接垫310与焊球275电性连接至第三导电层260。在一些实施例中,晶片300可是图1中的相位阵列天线中的中频电路,射频电路或中频电路和射频电路的整合电路。

97.在本实施例中,通过第三导电层260的设置,可使第四导电层270、271于制作时可易于附着于第三导电层260的顶面261并形成球状,藉此,可用来限制第四导电层270、271于顶面261的范围内,以减少第四导电层270、271有溢出于顶面261的范围外的问题。在一些实施例中,第三导电层与第四导电层可以省略其中之一,当省略第三导电层时,第四导电层270、271则可形成于另一导电层的顶面上,此时,另一导电层也可以用来限制第四导电层270、271的范围,以减少第四导电层270、271溢出范围外的问题。

98.在本实施例中,通过至少两层介电层(即第一介电层210与第二介电层230)的设置,以及使第一导电层220a与第二导电层240分别设置于不同的介电层上的方式,可使第一导电层220a与第二导电层240不需设置在同一个介电层中,以降低第一导电层220a与第二导电层240在制作时有被损坏的问题。此外,通过调整两个金属版(即第一导电层220a与第二导电层240)之间的介电层(即第一介电层210与第二介电层230)的厚度,则可增加辐射出去的电磁波能量。至此,已制作完成本实施例的电子装置20。

99.以下将列举其他实施例以作为说明。在此必须说明的是,下述实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

100.图4为本揭露另一实施例的电子装置的上视示意图。请同时参照图3与图4,本实施例的电子装置20a大致相似于图3的电子装置20,因此两实施例中相同与相似的构件于此不再重述。本实施例的电子装置20a不同于电子装置20之处在于,在本实施例的电子装置20a的天线元件15中,第四导电层271a、第三导电层260a以及底部导电层285a分别为连续且不间断的图案,以共同围绕槽孔145。此外,第四导电层271a的形状可对应于第三导电层260a的形状,且第三导电层260a的形状也可对应于底部导电层285a的形状。

101.图5a至图5d为本揭露多个实施例的导电结构的局部上视示意图。请同时参照图3以及图5a至图5d,本实施例的导电结构24a、24b、24c、24d大致相似于图3的导电结构24,因此两实施例中相同与相似的构件于此不再重述。本实施例的导电结构24a、24b、24c、24d不同于导电结构24之处在于,在本实施例的导电结构24a、24b、24c、24d中,第四导电层270的形状与第四导电层271的形状可以为圆形以外的封闭的图形或部分封闭图形,以使第四导电层270、271于制作时可被限制在第三导电层260的形状的范围内或在底部导电层285的形状的范围内。

102.具体来说,请参照图5a,导电结构24a中的第三导电层260的形状为封闭的方形,且导电结构24a中的第四导电层270的形状也对应地为封闭的方形。

103.请参照图5b,导电结构24b中的第三导电层260的形状为封闭的五边形,且导电结构24b中的第四导电层270的形状也对应地为封闭的五边形。

104.请参照图5c,底部导电层285的形状为部分封闭的圆形并具有缺口2852。导电结构24c中的第三导电层260的形状为部分封闭的圆形并具有缺口262,且缺口262可连接缺口

2852。导电结构24c中的第四导电层271的形状为部分封闭的圆形并延伸至缺口262与缺口2852内。

105.请参照图5d,底部导电层285的形状为部分封闭的方形并具有缺口2852与缺口2853。导电结构24c中的第三导电层260的形状为部分封闭的方形并具有缺口262与缺口263,其中缺口262可连接缺口2852,且缺口263可连接缺口2853。导电结构24c中的第四导电层271的形状为部分封闭的方形并延伸至缺口262、缺口263、缺口2852以及缺口2853内。

106.在本实施例中,虽然第三导电层260的形状可以为圆形、方形或五边形,且第四导电层270的形状与第四导电层270的形状可以为圆形、方形或五边形,但本揭露并不对第三导电层260的形状、第四导电层270的形状以及第四导电层270的形状加以限制,只要使第四导电层270与第四导电层271于制作时可被限制在第三导电层260的形状的范围内或在底部导电层285的形状的范围内即可。

107.综上所述,在本揭露实施例的电子装置中,通过至少两层介电层(即第一介电层与第二介电层)的设置,以及使第一导电层与第二导电层分别设置于不同的介电层上的方式,因而可使第一导电层与第二导电层不需设置在同一个介电层中,以降低第一导电层与第二导电层在制作时有被损坏的问题。在本实施例中,由于第一介电层与第二介电层中的至少一个介电层的损耗正切df小于或等于0.1且大于0(即0《df≦0.1),因而可以减少电磁波在第一介电层与第二介电层中的损耗,进而可使电磁波的发射效率较佳。在本实施例中,由于第三导电层的形状(或底部导电层的形状)可以封闭第四导电层的形状,因而可使第四导电层于制作时可以被限制在第三导电层的形状的范围内(或在底部导电层的形状的范围内),进而可以减少第四导电层于制作时有溢出于第三导电层的形状的范围外(或底部导电层的形状的范围外)的问题。

108.最后应说明的是:以上各实施例仅用以说明本揭露的技术方案,而非对其限制;尽管参照前述各实施例对本揭露进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本揭露各实施例技术方案的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。