1.本发明涉及电力电子技术领域,特别涉及一种防止逆变系统中可控硅误导通的驱动电路及方法。

背景技术:

2.可控硅时ups及并网储能电路的常用保护器件,通常并联在继电器的两端进行保护,可以防止继电器在闭合瞬间产生拉弧损坏触点,提高了继电器的使用寿命及可靠性。同时可控硅还能解决继电器切换时间过长导致并离网切换时出现电压跌落,电压中断的问题。

3.但在usp及并网储能电路中将可控硅并联在继电器上后,如果外部通过空气开关、接触器、断路器等保护器件后,开关闭合时,市电瞬间会在可控硅两端产生很大的震荡电压波形,这个震荡波形瞬间产生的高达上百kv/us的dv/dt,一般而言,主回路中并联的rc吸收效果一般,并不能完全降低输入到光耦端的dv/dt,将会导致驱动光耦内部的可控硅误导通。

4.为了解决可控硅误导通的问题,中国专利cn2012204663880方案中增加了继电器,但无法保证对光耦控制的及时性,继电器本身闭合时间就需要5ms~15ms以上,导致可控硅不能有效实时进行闭合,从而在市电掉电时不能及时切换到离网状态,因此无法应用于ups、并网储能等电路中。

5.如图1,ac为交流市电或者电网经过变压器隔离之后参数的交流电,s1为电路中的断路器或者接触器,ry1、ry2分别为逆变器作用于市电及负载的旁路继电器,c2为逆变器自身及负载端的电容总和,与继电器ry1、ry2并联的可控硅及驱动电路分别由part1及parta组成。其中,part1由可控硅q1、q2及其驱动电路所需的光耦u1、u2,驱动电阻r2、r3,限流电阻r4、r5,光耦电压平衡电阻r6、r7,可控硅驱动负压钳位二极管d1、d2,可控硅尖峰抑制吸收电阻r1,电容c1组成。parta由可控硅q1a、q2a,驱动电路所需的光耦u1a、u2a及其驱动电路,驱动电阻r2a、r3a,限流电阻r4a、r5a,光耦电压平衡电阻r6a、r7a,可控硅驱动负压钳位二极管d1a、d2a,可控硅尖峰抑制吸收电阻r1a、电容c1a组成。

6.图2是现有技术中的包含可控硅模块的逆变系统的光耦模块误导通路径示意图,继电器ry1,ry2虽然断开了,但是s1闭合瞬间s1的触点之间会产生拉弧现象,依靠市电侧寄生参数(过于复杂,图2中并未展示)会与线路寄生漏感(ls1~ls10)及寄生电容(cs1,cs1a),形成输入在可控硅q1(q1a),q2(q2a)两端非常高的dv/dt。虽然电路中增加了可控硅尖峰抑制吸收电阻r1(r1a),电容c1(c1a),但是阻容参数不能无限过大,过大会产生rc阻容压降电路效应,只要s1闭合,即使继电器ry1,ry2没有闭合,线路端电容c2也会产生电压,造成误判。另外可控硅q1(q1a,q2(q2a)由于在驱动gk中存在泄放电阻,其耐受dv/dt是远远高于驱动光耦内部可控硅的dv/dt的。所以在实际中测试得到的结果是驱动光耦内部可控硅误导通后产生了图2的路径。

7.经过图2的路径参数后,如图3,图3现有技术中的包含可控硅模块的光耦内部可控

硅误导通后与逆变拓扑电路产生的回路路径示意图,光耦内部可控硅误导通后,又会导通主回路中的可控硅q1(q1a),q2(q2a),从而产生如图3的让市电经过可控硅q1(q1a),q2(q2a)与逆变拓扑产生回路,相当于直接让逆变拓扑短路市电,存在炸机风险。

技术实现要素:

8.现有技术中,在usp及并网储能电路中将可控硅并联在继电器上后,外部的空气开关、接触器、断路器等保护器件开关闭合时,市电瞬间会在可控硅两端产生很大的震荡电压波形,这个震荡波形瞬间产生的高达上百kv/us的dv/dt,将会导致驱动光耦内部的可控硅误导通,从而触发光耦控制的主回路可控硅导通,相当于直接让逆变拓扑短路市电,存在炸机风险。

9.针对上述问题,提出一种防止逆变系统中可控硅误导通的驱动电路及方法,通过在驱动电路的可控硅模块与光耦模块之间连接电压尖峰抑制模块,与可控硅模块组成rlc低通滤波电路,使得光耦模块内部的可控硅对瞬间高dv/dt震荡电压波形的抗干扰能力提升数十倍以上,并且电压尖峰抑制模块中电感为mh级别、电容值为百pf级别,对光耦控制的驱动电路主回路中可控硅控制不会造成延时,兼顾了及时性与高抗干扰性。

10.第一方面,一种防止逆变系统中可控硅误导通的驱动电路,与逆变系统中的开关器件并联,包括:可控硅模块;电压尖峰抑制模块;光耦模块;所述可控硅模块与所述开关器件并联,所述可控硅模块的第一端、第二端分别与所述开关器件的第一端、第二端电连接;所述电压尖峰抑制模块的第一端与所述可控硅模块的第三端电连接;所述电压尖峰抑制模块的第二端与所述光耦模块的第一端电连接;所述光耦模块用于驱动可控硅模块中的可控硅导通;所述电压尖峰抑制模块用于与所述可控硅模块组成rlc滤波电路,以抑制所述开关器件闭合瞬间传输到所述光耦模块的高dv/dt震荡电压波形。

11.结合本发明所述的防止逆变系统中可控硅误导通的驱动电路,第一种可能的实施方式中,所述可控硅模块包括:第一电阻、第二电阻、第三电阻、第四电阻、第五电阻、第一二极管、第二二极管、第一电容;所述开关器件的第一端、所述第一电阻的第一端、第一可控硅的阴极、第二可控硅的阳极、第一二极管的阴极、第二电阻的第一端共接;所述第一电阻的第二端与所述第一电容的第一端电连接;所述第一电容的第二端、所述开关器件的第二端、第一可控硅的阳极、第二可控硅的阴极、第二二极管的阳极第三电阻的第一端共接;所述第一二极管的阳极、第二电阻的第二端、第四电阻的第一端、第一可控硅的控制端共接;第三电阻的第二端、第二二极管的阴极、第五电阻的第一端、第二可控硅的控制端

共接。

12.结合本发明第一种可能的实施方式,第二种可能的实施方式中,所述电压尖峰抑制模块包括:第一电感;第二电感;第二电容;所述第一电感的第一端与所述第四电阻的第二端电连接;所述第一电感的第二端与所述第二电容的第一端电连接;所述第二电感的第一端与所述第五电阻的第二端电连接;所述第二电感的第二端与所述第二电容的第二端电连接;其中,所述第一电感、第二电感的单位为mh级别,所述第二电容容值为百pf级别。

13.结合本发明第一种可能的实施方式,第三种可能的实施方式中,所述电压尖峰抑制模块包括:第一电感;第二电感;第二电容;第三电容;所述第一电感的第一端与所述第四电阻的第二端电连接;所述第一电感的第二端与所述第二电容的第一端电连接;所述第二电容的第二端与所述第三电容的第一端电连接;所述第二电感的第一端与所述第五电阻的第二端电连接;所述第二电感的第二端与所述第三电容的第二端电连接;其中,所述第一电感、第二电感的单位为mh级别,所述第二电容、第三电容容值为百pf级别。

14.结合本发明第二种可能的实施方式,第四种可能的实施方式中,所述光耦模块包括:第一光耦电路;第六电阻;所述第一光耦电路的第一端、所述第六电阻的第一端与所述第二电容的第一端电连接;所述第一光耦电路的第二端、所述第六电阻的第二端与所述第二电容的第二端电连接。

15.结合本发明第三种可能的实施方式,第五种可能的实施方式中,所述光耦模块包括:第一光耦电路;第二光耦电路;第六电阻;第七电阻;所述第一光耦电路的第一端、所述第六电阻的第一端与所述第二电容的第一端电

连接;所述第一光耦电路的第二端、第二光耦电路的第一端、所述第六电阻的第二端、第七电阻的第一端、第二电容的第二端、第三电容的第一端电连接;所述第二光耦电路的第二端、第七电阻的第二端、第三电容的第二端电连接。

16.结合本发明所述的防止逆变系统中可控硅误导通的驱动电路,第六种可能的实施方式中,所述逆变系统为单相逆变系统、split-phase逆变系统、三相逆变系统中的一种。

17.第二方面,一种防止逆变系统中可控硅误导通的驱动方法,采用第一方面所述的驱动电路,包括:步骤100、将驱动电路与逆变系统中的开关器件并联;步骤200、在所述驱动电路中可控硅模块与所述光耦模块之间连接电压尖峰抑制模块,所述电压尖峰抑制模块与所述可控硅模块组成rlc滤波电路,以抑制所述开关器件闭合瞬间光耦模块传输到所述可控硅模块的高dv/dt震荡电压波形。

18.结合第二方面所述的驱动方法,第一种可能的实施方式中,所述电压尖峰抑制模块中电感为mh级别、电容值为百pf级别。

19.结合第二方面第一种可能的实施方式,第二种可能的实施方式中,所述逆变系统为单相逆变系统、split-phase逆变系统、三相逆变系统中的一种。

20.实施本发明所述的防止逆变系统中可控硅误导通的驱动电路及方法,通过在驱动电路的可控硅模块与光耦模块之间连接电压尖峰抑制模块,与可控硅模块组成rlc低通滤波电路,使得光耦模块内部的可控硅对瞬间高dv/dt震荡电压波形的抗干扰能力提升数十倍以上,并且电压尖峰抑制模块中电感为mh级别、电容值为百pf级别,对光耦控制的驱动电路主回路中可控硅控制不会造成延时,兼顾了及时性与高抗干扰性。

附图说明

21.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

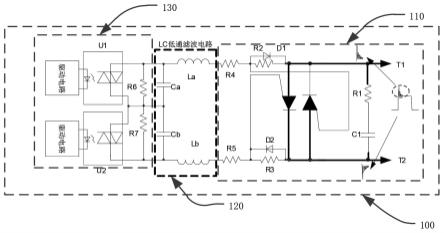

22.图1是现有技术中的包含可控硅模块的逆变系统示意图;图2是现有技术中的包含可控硅模块的逆变系统的光耦模块误导通路径示意图;图3是现有技术中的包含可控硅模块的可控硅误导通后与逆变拓扑电路产生的回路路径示意图;图4是本发明中防止逆变系统中可控硅误导通的驱动电路模块连接示意图;图5是本发明防止逆变系统中可控硅误导通的驱动电路实施例1电路示意图;图6是本发明防止逆变系统中可控硅误导通的驱动电路实施例2电路示意图;图7是本发明中的单相逆变系统框图第一示意图;图8是本发明中的单相逆变系统框图第二示意图;图9是本发明中的split-phase逆变系统框图示意图;图10是本发明中的三相逆变系统框图示意图;图11是本发明防止逆变系统中可控硅误导通的驱动方法示意图。

具体实施方式

23.下面将结合发明中的附图,对本发明中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有付出创造性劳动前提下所获得的其他实施例,都属于本发明保护的范围。

24.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/ 或”包括一个或多个相关的所列项目的任意的和所有的组合。

25.现有技术中,在usp及并网储能电路中将可控硅并联在继电器上后,外部的空气开关、接触器、断路器等保护器件开关闭合时,市电瞬间会在可控硅两端产生很大的震荡电压波形,这个震荡波形瞬间产生的高达上百kv/us的dv/dt,将会导致驱动光耦内部的可控硅误导通,从而触发光耦控制的主回路可控硅导通,相当于直接让逆变拓扑短路市电,存在炸机风险。

26.针对上述问题,提出一种防止逆变系统中可控硅误导通的驱动电路100及方法。

27.驱动电路100实施方式实施例1如图4,图4是本发明中防止逆变系统中可控硅误导通的驱动电路模块连接示意图;一种防止逆变系统中可控硅误导通的驱动电路100,与逆变系统中的开关器件并联,包括可控硅模块110、电压尖峰抑制模块120及光耦模块130;可控硅模块110与开关器件并联,可控硅模块110的第一端、第二端分别与开关器件的第一端、第二端电连接;电压尖峰抑制模块120的第一端与可控硅模块110的第三端电连接;电压尖峰抑制模块120的第二端与光耦模块130的第一端电连接;光耦模块130用于驱动可控硅模块110中的可控硅导通;电压尖峰抑制模块120用于与可控硅模块110组成rlc低通滤波电路,以抑制开关器件闭合瞬间传输到光耦模块130的高dv/dt震荡电压波形,从而避免光耦内部的可控硅及其控制的主回路可控硅(q1,q2)误导通。

28.本技术中的开关器件可以为逆变系统中的断路器、继电器或者其他开关器件。

29.进一步地,可控硅模块110包括第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、第一二极管d1、第二二极管d2、第一电容c1;开关器件的第一端、第一电阻r1的第一端、第一可控硅q1的阴极、第二可控硅q2的阳极、第一二极管d1的阴极、第二电阻r2的第一端共接;第一电阻r1的第二端与第一电容c1的第一端电连接;第一电容c1的第二端、开关器件的第二端、第一可控硅q1的阳极、第二可控硅q2的阴极、第二二极管d2的阳极第三电阻r3的第一端共接;第一二极管d1的阳极、第二电阻r2的第二端、第四电阻r4的第一端、第一可控硅q1的控制端共接;第三电阻r3的第二端、第二二极管d2的阴极、第五电阻r5的第一端、第二可控硅q2的控制端共接。

30.在本实施例1中,电压尖峰抑制模块120包括第一电感la、第二电感lb、第二电容ca、第三电容cb;第一电感la的第一端与第四电阻r4的第二端电连接;第一电感la的第二端与第二电容ca的第一端电连接;第二电容ca的第二端与第三电容cb的第一端电连接;第二电感lb的第一端与第五电阻r5的第二端电连接;第二电感lb的第二端与第三电容cb的第二

端电连接;其中,第一电感la、第二电感lb的单位为mh级别,第二电容ca、第三电容cb容值为百pf级别。

31.在本实施例1中,光耦模块130包括第一光耦电路u1、第二光耦电路u2、第六电阻r6、第七电阻r7;第一光耦电路u1的第一端、第六电阻r6的第一端与第二电容ca的第一端电连接;第一光耦电路u1的第二端、第二光耦电路u2的第一端、第六电阻r6的第二端、第七电阻r7的第一端、第二电容ca的第二端、第三电容cb的第一端电连接;第二光耦电路u2的第二端、第七电阻r7的第二端、第三电容cb的第二端电连接。

32.如图5,图5是本发明防止可控硅q驱动光耦误导通的驱动电路100实施例1电路示意图;本技术中的驱动电路100包括可控硅模块110、电压尖峰抑制模块120及光耦模块130,光耦模块130驱动可控硅模块110中的可控硅(q1,q2)导通。可控硅模块110中的第一电阻r1为可控硅 (q1,q2)尖峰抑制吸收电阻,第二电阻r2、第三电阻r3为驱动电阻,第四电阻r4、第五电阻r5为限流电阻,第一二极管d1、第二二极管d2用于电压波形钳位,光耦模块130中的第六电阻r6、第七电阻r7为光耦电压平衡电阻,在本实施例1中采用双光耦(u1、u2)驱动。

33.本技术实施例1中的电压尖峰抑制模块120用于抑制进入光耦模块130前端的瞬间高dv/dt震荡电压波形,包括第二电容ca、第三电容cb、第一电感la、第二电感lb,它们与可控硅模块中的第二电阻r2/第三电阻r3 第四电阻r4 第五电阻r5构成rlc低通滤波电路。在本技术实施方式中,将第二电容ca、第三电容cb的电容值取为百pf级别,将第一电感la、第二电感lb的电感取为mh级别,从而可以基本上忽略线路的其它寄生参数。

34.由于在高频时,等效的阻抗,[r为r2/r3 r4 r5],[l为la lb], 从而可以忽略电阻r的在高频滤波的作用,则输入光耦内部可控硅的尖峰电压波形被滤波的截止频率为:在正常时候,市电频率仅为50hz/60hz,所以切换时造成正常波形的相位延迟基本可以忽略不计。也就是说光耦模块130能及时触发可控硅模块110中的可控硅(q1,q2)且能及时输出关闭信号。

[0035]

逆变系统为单相逆变系统、split-phase逆变系统、三相逆变系统中的一种。

[0036]

在本技术实施方式中,逆变系统可以选择单相逆变系统、split-phase逆变系统或者三相逆变系统。

[0037]

如图7中,图7是本发明中的单相逆变系统框图第一示意图;由单相逆变系统组成的电路框图,ac为交流市电或者电网经过变压器隔离之后参数的交流电。s1为电路中的断路器或者接触器,ry2为逆变器作用于市电及负载的旁路继电器,c2为逆变器自身及负载端的电容总和。继电器ry2与本实施例1中的驱动电路100并联。

[0038]

如图8中的单相逆变系统包括两个作用于市电及负载的旁路继电器ry1、ry2为逆变器,c2为逆变器自身及负载端的电容总和。继电器ry1、ry2分别与本技术实施例1中的驱动电路100并联,图8是本发明中的单相逆变系统框图第二示意图。

[0039]

如图9为split-phase逆变系统组成的电路框图,其中的ac为交流市电或者电网经过变压器隔离之后参数的split-phase交流电,s1为电路中的断路器或者接触器,ry1、ry2

为逆变器作用于市电及负载的旁路继电器,c2、c3为逆变器自身及负载端的电容总和。继电器ry1、ry2分别与本技术实施例1中的驱动电路100并联,图9是本发明中的split-phase逆变系统框图示意图。

[0040]

如图10为三相逆变系统组成的电路框图,其中的ac为交流市电或者电网经过变压器隔离之后参数的三相交流电。s1为电路中的断路器或者接触器,ry1、ry、ry3为逆变器作用于市电及负载的旁路继电器,c2、c3、c4为逆变器自身及负载端的电容总和。继电器ry1、ry2、ry3分别与本技术实施例1中的驱动电路100并联,图10是本发明中的三相逆变系统框图示意图。

[0041]

值得注意的是,在逆变器或者逆变系统内部因保护开关器件(继电器/断路器)增加的抗dv/dt措施电路,由此构成的逆变电路,该逆变电路可以以其它电路形式及更多相组成的逆变桥臂形式组合而成的变形衍生拓扑电路,也属于在本专利范围内。

[0042]

通过在驱动电路的可控硅模块110与光耦模块130之间连接电压尖峰抑制模块,与可控硅模块组成rlc低通滤波电路,使得光耦模块130内部的可控硅对瞬间高dv/dt震荡电压波形的抗干扰能力提升数十倍以上,并且电压尖峰抑制模块120中电感为mh级别、电容值为百pf级别,对光耦控制的驱动电路主回路中可控硅(q1,q2)控制不会造成延时,兼顾了及时性与高抗干扰性。

[0043]

实施例2在本实施例2中,与实施例1不同的是,如图6,图6是本发明防止逆变系统中可控硅误导通的驱动电路100’实施例2电路示意图;本实施例2中采用单光耦驱动可控硅,对应的电路组成及结构为:电压尖峰抑制模块120’包括第一电感la、第二电感lb、第二电容ca;第一电感la的第一端与第四电阻r4的第二端电连接;第一电感la的第二端与第二电容ca的第一端电连接;第二电感lb的第一端与第五电阻r5的第二端电连接;第二电感lb的第二端与第二电容ca的第二端电连接;其中,第一电感la、第二电感lb的单位为mh级别,第二电容ca容值为百pf级别。

[0044]

在本实施例2中,光耦模块130’包括第一光耦电路u1、第六电阻r6;第一光耦电路u1的第一端、第六电阻r6的第一端与第二电容cb的第一端电连接;第一光耦电路u1的第二端、第六电阻r6的第二端与第二电容cb的第二端电连接。

[0045]

驱动方法实施方式一种防止逆变系统中可控硅误导通的驱动方法,采用第一方面的驱动电路(100/100’),如图11,图11是本发明防止逆变系统中可控硅误导通的驱动方法示意图,包括:步骤100、将驱动电路(100/100’)与逆变系统中的开关器件并联;步骤200、在驱动电路中可控硅模块110与光耦模块130之间连接电压尖峰抑制模块120,电压尖峰抑制模块120与可控硅模块110组成rlc滤波电路,以抑制开关器件闭合瞬间产生的高dv/dt震荡电压波形。电压尖峰抑制模块120中的第二电容ca、第三电容cb、第一电感la、第二电感lb,它们与可控硅模块110中的第二电阻r2/第三电阻r3 第四电阻r4 第五电阻r5构成rlc低通滤波电路。

[0046]

进一步地,电压尖峰抑制模块120中电感l为mh级别、电容值为百pf级别。

[0047]

优选地,逆变系统为单相逆变系统、split-phase逆变系统、三相逆变系统中的一种。

[0048]

实施本发明的防止逆变系统中可控硅误导通的驱动电路及方法,通过在驱动电路的可控硅模块110与光耦模块130之间连接电压尖峰抑制模块,与可控硅模块组成rlc低通滤波电路,使得光耦模块130内部的可控硅对瞬间高dv/dt震荡电压波形的抗干扰能力提升数十倍以上,并且电压尖峰抑制模块120中电感为mh级别、电容值为百pf级别,对光耦控制的驱动电路主回路中可控硅(q1,q2)控制不会造成延时,兼顾了及时性与高抗干扰性。

[0049]

以上仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。