技术特征:

1.一种加解密架构,其特征在于,包括:控制器,所述控制器通过总线与外部连接,实现与外部通信;数据流控制模块,所述数据流控制模块连接所述控制器;算法引擎核模块,所述算法引擎核模块连接所述数据流控制模块;以及寄存器堆模块,所述寄存器堆模块通过总线与外部连接,且所述寄存器堆模块还与所述数据流控制模块连接;其中,所述算法引擎核模块利用所述数据流控制模块提供的分组待运算数据和所述寄存器堆模块中配置的加解密运算所需要的密钥和初始向量进行加解密运算并将所述加解密运算的运算结果数据反馈给所述数据流控制模块,所述数据流控制模块通过所述控制器将所述运算结果数据输出。2.根据权利要求1所述的加解密架构,其特征在于,算法引擎核模块内部集成了能独立完成各自的算法运算的sm4算法引擎与aes算法引擎。3.根据权利要求2所述的加解密架构,其特征在于,sm4算法引擎内部包括sm4字节替换单元、sm4加密/解密运算单元和sm4密钥扩展单元,sm4字节替换单元用来做字节替换操作,通过查找第一查找表将输入数据以字节为单位替换为对应的数据并输出;sm4加密/解密运算单元内部集成了32级流水的轮函数,可实现单个时钟周期的输入输出,sm4密钥扩展模块产生的轮密钥供sm4加密/解密运算单元使用;aes算法引擎单元集成了aes-128、aes-192、aes-256这3种算法独立的aes加密/解密运算单元和aes密钥扩展单元,aes列混淆单元、aes字节替换单元,aes字节替换单元主要用来做字节替换操作,通过查找第二查找表将输入数据以字节为单位替换为对应的数据并输出,aes列混淆单元经行移位后的状态矩阵与固定的矩阵相乘,得到混淆后的状态矩阵来实列混淆变换。4.根据权利要求1所述的加解密架构,其特征在于,所述控制器内部集成包括dma寄存器和dma读写数据流控制单元;dma寄存器经一ahb从接口连接ahb总线;dma读写数据流控制单元经一ahb主接口连接ahb总线,dma读写数据流控制单元连接数据流控制模块;dma读写数据流控制单元根据dma寄存器中的配置通过ahb总线获取待运算数据并传输给数据流控制模块。5.根据权利要求1所述的加解密架构,其特征在于,所述寄存器堆模块通过一ahb从接口连接对外连接的ahb总线,所述寄存器堆模块经内部总线连接数据流控制模块;寄存器堆模块针对算法引擎核模块实现的aes算法配置第一密钥寄存器、第一初始向量寄存器,寄存器堆模块针对算法引擎核模块实现的sm4算法配置第二密钥寄存器、第二初始向量寄存器;寄存器堆模块配置多组通道状态寄存器,用于记录运算状态;寄存器堆模块配置一组指令寄存器。6.根据权利要求4或5所述的加解密架构,其特征在于,对应寄存器堆模块和dma寄存器的ahb从接口经ahb总线连接设置相应ahb主接口的cpu。7.根据权利要求1所述的加解密架构,其特征在于,所述数据流控制模块包括内部缓存和流控制单元;其中,内部缓存包括输入fifo缓存和输出fifo缓存,输入fifo缓存用于缓存控制器利用总线读取的待运算数据,输出fifo用于缓存算法引擎核模块输出到待运算数据的运算结果数据;流控制单元包括:用于将输入fifo缓存中数据串并转换的串并转换逻辑电路,用于将运算结果数据进行并串转换的并串转换逻辑电路,用于对指令寄存器中指令进行译码的指令译码器,用于对指令进行解析的指令解析器,用于根据内部缓存中数据缓存状态控制控制器数据读写的流量控制器,用于与算法引擎核模块交互的数据下发回收接

口,连接到所述寄存器堆模块的调试追踪信号输出接口、状态机fsm状态输出接口和通道状态监控器,用于对待运算数据中不足一个分组的数据进行暂存的数据暂存器,用于检测内部缓存中等待一个分组长度的数据是否超时的超时检测器。8.根据权利要求7所述的加解密架构,其特征在于,流控制单元实现状态机fsm,状态机fsm根据算法种类启动算法引擎核模块相应的算法引擎,状态机fsm控制读取输入fifo缓存中的数据,并经过串并转换逻辑电路串并转换后通过数据下发回收接口写入到算法引擎核模块中进行加解密业务运算,运算完成后状态机fsm获取运算结果数据经数据下发回收接口回收到流控制单元,并经过并串转换后写入到输出fifo缓存中等待控制器从输出fifo缓存中读取。9.根据权利要求7所述的加解密架构,其特征在于,流量控制器在输出fifo缓存有数据时请求控制器读输出fifo缓存,并根据控制器的响应信号产生输出fifo缓存的读使能;流控制单元在输入fifo缓存非空时产生一个脉冲用来启动输入fifo缓存的读使能,读取输入fifo缓存的数据;在输入fifo缓存中数据满时,流量控制器向控制器的dma读写数据流控制单元发送停止数据读入的信息。10.根据权利要求7所述的加解密架构,其特征在于,流控制单元收到的数据无法实现一个分组时,数据暂存器将不足一个分组的数据进行暂存,流控制单元收到后续数据时,提取暂存的数据与后续数据组合成一个分组。11.一种加解密控制方法,应用于如权利要求1-10任一所述的加解密架构,其特征在于,包括:对控制器和寄存器堆模块进行配置;检测加解密架构是否空闲;空闲则启动控制器,控制器根据控制器的配置获取待运算数据传输给数据流控制模块;数据流控制模块根据寄存器堆模块的配置确定算法类型,数据流控制模块控制对待运算数据进行串并转换后通过数据下发回收接口写入到算法引擎核模块中进行对应相应算法类型的加解密业务运算;数据流控制模块回收算法引擎核模块的运算结果数据并经并串转换后发送给控制器,控制器根据控制器的配置将运算结果数据输出到相应的存储位置。12.根据权利要求11所述的加解密控制方法,其特征在于,对控制器的配置包括:配置控制器的dma寄存器中的数据起始地址寄存器、数据长度寄存器、数据标志位寄存器,运算结果起始地址寄存器和dma启动寄存器;控制器根据dma启动寄存器的启动指示而启动,控制器根据数据起始地址寄存器的数据起始地址和数据长度寄存器的数据长度通过总线获取待运算数据;当运算结束,控制器根据运算结果起始地址寄存器的地址将从数据流控制模块获取运算后的运算结果数据通过ahb主接口输出通道写回到对应的存储地址。13.根据权利要求11所述的加解密控制方法,其特征在于,对寄存器堆模块的配置包括:配置寄存器堆模块的第一密钥寄存器、第一初始向量寄存器,第二密钥寄存器、第二初始向量寄存器和指令寄存器,在第一密钥寄存器、第一初始向量寄存器,第二密钥寄存器、第二初始向量寄存器配置sm4算法和aes算法所需的密钥和初始向量;在指令寄存器配置加解密运算次数、使用的算法类型、算法模式和算法启动比特位。14.根据权利要求11所述的加解密控制方法,其特征在于,检测加解密架构是否空闲包括:数据流控制模块配置连接到寄存器堆模块中通道状态寄存器的调试追踪信号输出接

口、状态机fsm状态输出接口和通道状态监控器,将调试追踪信号状态机fsm状态和通道状态输出到通道状态寄存器中,获取通道状态寄存器中的通道状态监控器数据检测加解密架构是否空闲。15.根据权利要求11所述的加解密控制方法,其特征在于,数据流控制模块的流控制单元基于寄存器堆模块的配置判断算法是否需要进行密钥拓展,若需要进行密钥拓展则先进行密钥拓展再进行加解密处理。16.根据权利要求10所述的加解密控制方法,其特征在于,数据流控制模块的流控制单元的流量控制器在输出fifo缓存有数据时请求控制器读输出fifo缓存,并根据控制器的响应信号产生输出fifo缓存的读使能;流控制单元在输入fifo缓存非空时产生一个脉冲用来启动输入fifo缓存的读使能,读取输入fifo缓存的数据;在输入fifo缓存中数据满时,流量控制器向控制器的dma读写数据流控制单元发送停止数据读入的信息。17.根据权利要求10所述的加解密控制方法,其特征在于,数据流控制模块的流控制单元按设定数据长度对待运算数据进行分组,对无法组成完整分组的数据通过数据暂存器暂存以等待后续数据,并通过超时检测器对等待分组数据进行计时。18.根据权利要求17所述的加解密控制方法,其特征在于,数据流控制模块的流控制单元对待运算数据和密钥处理过程中错误和分组数据等到超时进行监测并产生相应中断。19.一种处理器,其特征在于,所述处理器配置如权利要求1-10任一所述的加解密架构。20.一种服务器,其特征在于,所述服务器包括:至少一cpu,至少一配置如权利要求1-10任一所述的加解密架构的处理器,所述处理器通过ahb总线连接cpu。

技术总结

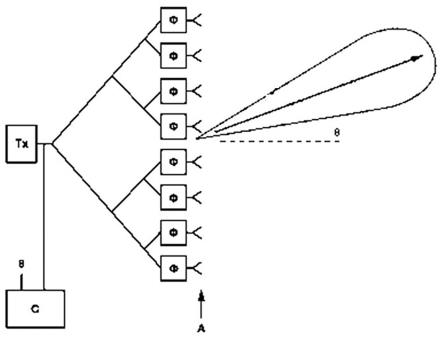

本发明涉及一种加解密架构、方法、处理器和服务器。加解密架构中,控制器连接数据流控制模块,将待运算数据传输给数据流控制模块;数据流控制模块将待运算数据分组发送给算法引擎核模块,算法引擎核模块内部集成了能独立完成各自的算法运算的SM4算法引擎与AES算法引擎,数据流控制模块判断执行算法种类后控制算法引擎核模块启动相应算法引擎,算法引擎核模块利用数据流控制模块提供的待运算数据和寄存器堆模块中配置的加解密运算所需要的密钥和初始向量进行加解密运算并将运算结果反馈给数据流控制模块,数据流控制模块通过控制器将运算结果数据输出,实现对SM4算法和AES算法兼容的加解密处理。法兼容的加解密处理。法兼容的加解密处理。

技术研发人员:赵新宇 孙旭 周玉龙 刘刚

受保护的技术使用者:苏州浪潮智能科技有限公司

技术研发日:2022.11.28

技术公布日:2022/12/30

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。