技术特征:

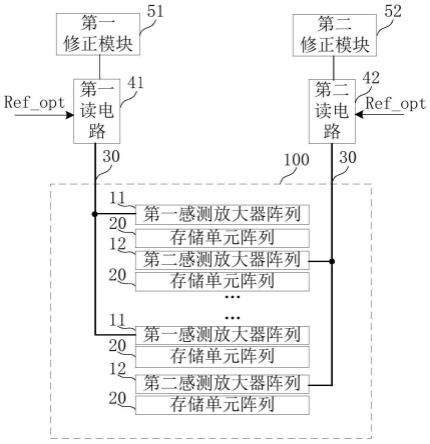

1.一种存储器,其特征在于,包括:存储模块,包括多个感测放大器阵列和多个存储单元阵列,所述感测放大器阵列与所述存储单元阵列交替排布,所述感测放大器阵列用于对所述存储单元阵列进行数据读写,其中,所述感测放大器阵列包括相邻的第一感测放大器阵列及第二感测放大器阵列,第一读电路,经由第一数据线与所述第一感测放大器阵列电连接,用于比较参考电压信号与对应的第一数据线上的信号,并输出比较结果作为读出数据;第二读电路,经由第一数据线与所述第二感测放大器阵列电连接,用于比较所述参考电压信号与对应的第一数据线上的信号,并输出比较结果作为读出数据;多个修正模块,用于对所述读出数据进行检错/纠错,其中,所述第一读电路与所述第二读电路被配置为将其输出的读出数据分别传输至不同的修正模块。2.根据权利要求1所述的存储器,其特征在于,所述第一读电路包括多个第一读电路单元,每一所述第一读电路单元经由对应的第一数据线电连接所述第一感测放大器阵列;所述第一读电路单元包括:第一输入电路,与所述第一数据线电连接,用于接收所述第一数据线上的信号;第一参考电路,用于接收所述参考电压信号;第一放大电路,与所述第一输入电路、所述第一参考电路均电连接,用于比较所述参考电压信号与对应的第一数据线上的信号,并将比较结果放大;第一输出电路,与所述第一放大电路电连接,用于输出放大后的比较结果。3.根据权利要求2所述的存储器,其特征在于,所述第一放大电路包括:第一晶体管,被配置为:源极与第一电压电连接;第二晶体管,被配置为:源极与第一电压节点电连接,漏极与所述第一晶体管的漏极电连接;第三晶体管,被配置为:源极与所述第一电压电连接,漏极与所述第一晶体管的栅极电连接,栅极与所述第一晶体管的漏极电连接;第四晶体管,被配置为:源极与第二电压节点电连接,漏极与所述第三晶体管的漏极及所述第二晶体管的栅极均电连接,栅极与所述第一晶体管的漏极电连接。4.根据权利要求3所述的存储器,其特征在于,所述第一读电路单元还包括第一预充电模块,所述第一预充电模块与所述第一晶体管的漏极和所述第三晶体管的漏极均电连接,用于预充电。5.根据权利要求3所述的存储器,其特征在于,所述第一输入电路包括:第五晶体管,被配置为:源极与第二电压电连接,漏极与所述第一电压节点电连接,栅极与所述第一数据线电连接。6.根据权利要求5所述的存储器,其特征在于,所述第一参考电路包括:第六晶体管,被配置为:源极与第三电压节点电连接,漏极与所述第二电压节点电连接,栅极与参考电压电连接;第七晶体管,被配置为:源极与所述第二电压电连接,漏极与所述第三电压节点电连接,栅极与所述第六晶体管的栅极及所述参考电压均电连接;第八晶体管,被配置为:源极与所述第二电压电连接,漏极与所述第三电压节点电连接,栅极与所述参考电压信号电连接。

7.根据权利要求3-6任一项所述的存储器,其特征在于,所述第一输出电路还包括:第一子输出电路,与所述第二电压节点、第二数据线及第二互补数据线均电连接,用于输出所述放大后的比较结果;第二子输出电路,与所述第一电压节点、所述第二数据线及所述第二互补数据线均电连接,用于输出所述放大后的比较结果,并匹配所述第一放大电路的输出负载,其中,所述第二数据线及所述第二互补数据线传输互为反相的数据。8.根据权利要求3-6任一项所述的存储器,其特征在于,所述第一输出电路还包括:第一开关单元,所述第一电压节点经由所述第一开关单元与均衡信号电连接;第二开关单元,所述第二电压节点经由所述第二开关单元与所述均衡信号电连接。9.根据权利要求8所述的存储器,其特征在于,所述第一开关单元包括第九晶体管,所述第二开关单元包括第十晶体管;所述第九晶体管被配置为:源极与所述第一电压电连接,漏极与所述第一电压节点电连接,栅极与所述均衡信号电连接;所述第十晶体管被配置为:源极与所述第一电压电连接,漏极与所述第二电压节点电连接,栅极与所述均衡信号电连接。10.根据权利要求7所述的存储器,其特征在于,所述第一子输出电路包括:第十一晶体管,被配置为:源极与第一电压电连接,栅极与所述第二电压节点电连接;第十二晶体管,被配置为:漏极与所述第十一晶体管的漏极电连接,栅极与所述第二电压节点及所述第十一晶体管的栅极均电连接;第十三晶体管,被配置为:源极接地,漏极与所述第十二晶体管的源极电连接,栅极与所述第二数据线电连接;第十四晶体管,被配置为:源极与所述第一电压电连接,漏极与第二互补数据线及所述第十一晶体管的漏极均电连接,栅极与所述第二数据线电连接。11.根据权利要求7所述的存储器,其特征在于,所述第二子输出电路包括:第十五晶体管,被配置为:源极与第一电压电连接,漏极与所述第二数据线电连接,栅极与所述第一电压节点电连接;第十六晶体管,被配置为:漏极与所述第十五晶体管的漏极电连接,栅极与所述第一电压节点及所述第十五晶体管的栅极均电连接;第十七晶体管,被配置为:漏极与所述第十六晶体管的源极电连接,栅极与所述第二互补数据线电连接;第十八晶体管,被配置为:源极接地,漏极与所述第十七晶体管的源极电连接,栅极与复位信号电连接;第十九晶体管,被配置为:源极与所述第一电压电连接,漏极与所述第二数据线电连接,栅极与所述第二互补数据线及所述第十七晶体管的栅极均电连接;第二十晶体管,被配置为:源极与所述第一电压电连接,漏极与所述第二数据线电连接,栅极与所述复位信号及所述第十八晶体管的栅极均电连接。12.根据权利要求7所述的存储器,其特征在于,所述第一读电路单元还包括:调整电路,与所述第一数据线、读选择信号、所述第一放大电路及所述第一输入电路均电连接,用于调整所述第一输入电路的驱动能力。

13.根据权利要求12所述的存储器,其特征在于,所述调整电路包括:第二十一晶体管,被配置为:源极与第二电压电连接,漏极与第一电压节点电连接,栅极与所述读选择信号电连接;第二十二晶体管,被配置为:源极与所述第二电压电连接,漏极与所述第一电压节点电连接,栅极经由第三开关单元与所述第一数据线电连接。14.根据权利要求12所述的存储器,其特征在于,所述第一读电路单元还包括第一写电路单元,所述第一写电路单元电连接所述第二数据线、写使能信号、均衡信号及所述第一数据线,所述第一写电路单元用于根据所述写使能信号及所述均衡信号向所述第一数据线写入数据。15.根据权利要求14所述的存储器,其特征在于,所述第一写电路单元包括:第二十三晶体管,被配置为:源极与第一电压电连接,漏极与所述第一数据线电连接;第二十四晶体管,被配置为:源极接地,漏极与所述第二十三晶体管的漏极及所述第一数据线均电连接;第一或非门,被配置为:输出端与所述第二十三晶体管的栅极电连接;第二或非门,被配置为:输出端与所述第二十四晶体管的栅极电连接;第一与非门,被配置为:输出端与所述第二或非门的第一输入端电连接,第一输入端与所述写使能信号电连接,第二输入端与所述均衡信号电连接;第一与门,被配置为:输出端与所述第一或非门的第二输入端电连接,第一输入端与所述写使能信号电连接,第二输入端与所述第二或非门的第二输入端及所述第二数据线均电连接;第一反向器,被配置为:输出端与所述第一或非门的第一输入端电连接,输入端与所述均衡信号电连接。

技术总结

本申请涉及一种存储器,包括存储模块、第一读电路、第二读电路及多个修正模块,存储模块包括多个感测放大器阵列和多个存储单元阵列,感测放大器阵列与所述存储单元阵列交替排布,感测放大器阵列用于对所述存储单元阵列进行数据读写;第一读电路用于比较参考电压信号与对应的第一数据线上的信号,并输出比较结果作为读出数据;第二读电路用于比较参考电压信号与对应的第一数据线上的信号,并输出比较结果作为读出数据;其中,第二感测放大器阵列与第一感测放大器阵列相邻;第一读电路与第二读电路被配置为将其输出的读出数据分别传输至不同的修正模块以进行检错/纠错。本申请能够及时发现并修复半导体存储装置中相邻存储单元失效缺陷。元失效缺陷。元失效缺陷。

技术研发人员:王佳

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2021.06.01

技术公布日:2022/12/5

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。