技术特征:

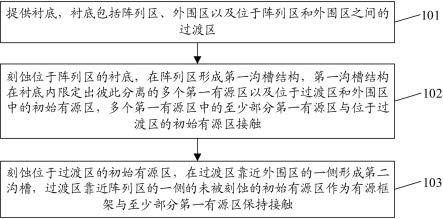

1.一种半导体结构,其特征在于,至少包括:衬底;浅槽隔离结构,设置在所述衬底中,且所述浅槽隔离结构包括凸部,且所述凸部超出所述衬底的表面;堆叠结构,设置在所述衬底上和所述浅槽隔离结构上;沉积通道,穿过所述堆叠结构与所述衬底和/或所述凸部的表面接触,所述沉积通道设置在所述衬底的高压器件区;台阶结构,设置在所述凸部上,且所述台阶结构位于所述沉积通道内,所述台阶结构的表面高于所述衬底的表面,且所述台阶结构的高度小于所述凸部的高度;栅氧化层,设置在所述衬底上,所述栅氧化层位于所述沉积通道内,且所述栅氧化层和所述台阶结构之间具有间隙;以及多晶硅层,覆盖在所述栅氧化层和所述台阶结构上。2.根据权利要求1所述的一种半导体结构,其特征在于,所述沉积通道的一侧壁设置在所述凸部上。3.根据权利要求1所述的一种半导体结构,其特征在于,所述堆叠结构包括衬底氧化层,所述衬底氧化层设置在所述衬底上,且所述衬底氧化层的厚度小于所述台阶结构的表面与所述衬底表面的高度差。4.根据权利要求3所述的一种半导体结构,其特征在于,所述堆叠结构包括保护层,所述保护层设置在所述衬底氧化层上,且所述衬底氧化层和所述保护层的厚度之和小于所述栅氧化层的厚度。5.根据权利要求4所述的一种半导体结构,其特征在于,所述堆叠结构包括硬掩膜层,所述硬掩膜层设置在所述保护层上。6.根据权利要求1所述的一种半导体结构,其特征在于,所述凸部的高度是所述浅槽隔离结构深度的1/10~1/5。7.一种半导体结构的制造方法,其特征在于,包括:提供一衬底;在所述衬底上形成衬底氧化层;在所述衬底上形成浅槽隔离结构,且所述浅槽隔离结构包括凸部,所述凸部超出所述衬底的表面;于所述衬底氧化层上和所述浅槽隔离结构上形成保护层,并于所述保护层上形成硬掩膜层;多次蚀刻所述硬掩膜层、所述保护层和所述衬底氧化层,形成沉积通道,并于所述凸部上形成台阶结构,其中,所述沉积通道与所述衬底和/或所述凸部的表面接触,所述台阶结构的表面高于所述衬底的表面;以及于所述衬底上形成栅氧化层,并于所述栅氧化层上和所述台阶结构上形成多晶硅层。8.根据权利要求7所述的一种半导体结构的制造方法,其特征在于,形成所述沉积通道的步骤包括:通过第一等离子气体减薄所述硬掩膜层,且减薄所述硬掩膜层的蚀刻量为所述硬掩膜层厚度的3/5~4/5。9.根据权利要求8所述的一种半导体结构的制造方法,其特征在于,在减薄所述硬掩膜

层后,通过第二等离子气体蚀刻所述硬掩膜层和所述保护层,直到位于所述衬底和所述凸部接缝处的所述硬掩膜层被移除。10.根据权利要求9所述的一种半导体结构的制造方法,其特征在于,在移除位于所述衬底和所述凸部接缝处的所述硬掩膜层前,通过所述第二等离子气体蚀刻所述硬掩膜层,直到位置对应所述衬底表面的所述硬掩膜层被移除。11.根据权利要求10所述的一种半导体结构的制造方法,其特征在于,在移除所述硬掩膜层后,蚀刻所述衬底氧化层和所述保护层,并同时蚀刻所述凸部,直到移除所述衬底氧化层。

技术总结

本发明公开了一种半导体结构及其制造方法,所述半导体结构至少包括:衬底;浅槽隔离结构,设置在衬底上,且浅槽隔离结构包括凸部,且凸部超出衬底的表面;堆叠结构,设置在衬底上和浅槽隔离结构上;沉积通道,穿过堆叠结构与衬底和/或凸部的表面接触,沉积通道设置在衬底的高压器件区上;台阶结构,设置在凸部上,且台阶结构位于沉积通道内,台阶结构的表面高于衬底的表面,且台阶结构的高度小于凸部的高度;栅氧化层,设置在衬底上,栅氧化层位于沉积通道内,且栅氧化层和台阶结构之间具有间隙;以及多晶硅层,覆盖在栅氧化层和台阶结构上。本发明提供了一种半导体结构及其制造方法,能够提升半导体器件的电学性能。够提升半导体器件的电学性能。够提升半导体器件的电学性能。

技术研发人员:刘洋 吴建兴

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:2022.10.21

技术公布日:2022/11/18

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。