半导体器件

1.相关申请的交叉引用

2.本技术要求于2021年6月4日在韩国知识产权局提交的韩国专利申请no.10-2021-0072834的优先权的权益,其公开内容通过引用整体合并于此。

技术领域

3.本公开涉及半导体器件。

背景技术:

4.半导体器件可以包括其中设置有向其写入数据的存储单元的单元区域以及其中设置有控制单元区域的电路的外围电路区域。外围电路区域可以包括行译码器、页缓冲器、电压发生器、控制逻辑电路等。行译码器可以通过字线、接地选择线、串选择线等连接到单元区域。为了提高半导体器件的集成度,已经提出了用于增加外围电路区域以及单元区域的集成度的各种方法。

技术实现要素:

5.示例实施例提供了通过在从外围电路区域被输入了负电压的第一区域中将高电压元件和低电压元件一起形成并且还在围绕第一阱区的第二阱区中形成低电压元件而具有提高的性能和/或集成度的半导体器件。

6.根据示例实施例,一种半导体器件包括:外围电路区域,所述外围电路区域包括位于衬底上的电路元件,所述电路元件是用于提供页缓冲器和行译码器的元件;以及单元区域,所述单元区域包括栅电极层和沟道结构,所述栅电极层在与所述衬底的上表面垂直的第一方向上堆叠并连接到所述行译码器,所述沟道结构在所述第一方向上延伸以穿透所述栅电极层并连接到所述页缓冲器。所述行译码器的所述电路元件包括在第一电源电压下操作的高电压元件和在比所述第一电源电压低的第二电源电压下操作的低电压元件。在所述高电压元件当中,至少一个第一高电压元件位于掺杂有具有第一导电类型的杂质的第一阱区中。至少一个所述低电压元件位于围绕所述第一阱区并掺杂有具有与所述第一导电类型不同的第二导电类型的杂质的第二阱区中。

7.根据示例实施例,一种半导体器件包括:外围电路区域,所述外围电路区域包括具有第一阱区和第二阱区的衬底、位于所述第一阱区中的nmos元件和位于所述第二阱区中的pmos元件,所述第一阱区掺杂有具有第一导电类型的杂质,所述第二阱区掺杂有具有与所述第一导电类型不同的第二导电类型的杂质;以及单元区域,所述单元区域包括栅电极层和沟道结构,所述栅电极层在与所述衬底的上表面垂直的第一方向上堆叠,所述沟道结构在所述第一方向上延伸以穿透所述栅电极层。所述第一阱区中的至少一个所述nmos元件中包括的栅极绝缘层的厚度与所述第二阱区中的至少一个所述pmos元件中包括的栅极绝缘层的厚度相同。

8.根据示例实施例,一种半导体器件包括:单元区域,所述单元区域包括多个存储单

元串,每个所述存储单元串包括连接在位线和公共源极线之间的沟道层、共享所述沟道层并彼此串联连接的存储单元以及连接到所述存储单元的字线;以及外围电路区域,所述外围电路区域包括连接到所述字线的行译码器和连接到所述位线的页缓冲器。在所述行译码器的nmos元件和pmos元件当中,在第一电源电压下操作并具有被输入负电压的主体的高电压nmos元件和在比所述第一电源电压低的第二电源电压下操作并具有被输入负电压的主体的第一低电压nmos元件位于单个第一阱区中。所述高电压nmos元件连接到所述字线。

9.根据示例实施例,一种半导体器件包括:衬底,所述衬底包括第一阱区和第二阱区,所述第一阱区掺杂有具有第一导电类型的杂质,所述第二阱区围绕所述第一阱区并掺杂有具有与所述第一导电类型不同的第二导电类型的杂质;多个nmos元件,所述多个nmos元件位于所述第一阱区中;以及多个pmos元件,所述多个pmos元件位于所述第二阱区中。所述第一阱区是袋状p阱。所述多个nmos元件包括至少一个第一nmos元件和至少一个第二nmos元件,并且所述至少一个第二nmos元件在与所述多个pmos元件相同的电源电压下操作。

附图说明

10.根据以下结合附图进行的详细描述,将更清楚地理解本公开的以上以及其他方面、特征和优点。

11.图1是根据示例实施例的半导体器件的示意性框图。

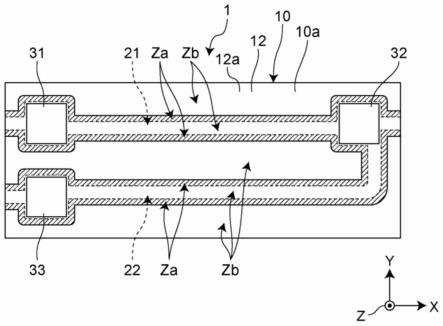

12.图2是根据示例实施例的半导体器件的示意图。

13.图3是根据示例实施例的半导体器件的存储块的示意性电路图。

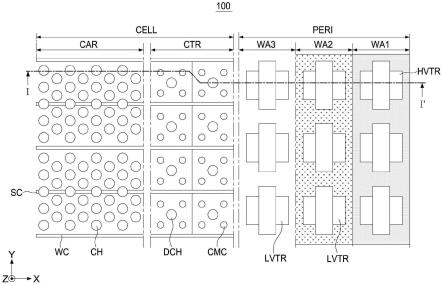

14.图4是示出了根据示例实施例的半导体器件中的单元区域和外围电路区域的布局的示意图。

15.图5是示出了根据示例实施例的半导体器件的结构的示图。

16.图6是沿着图5的线i-i'截取的截面图。

17.图7是示出了根据示例实施例的半导体器件的结构的示图。

18.图8是沿着图7的线ii-ii'截取的截面图。

19.图9至图11分别是示出了根据示例实施例的半导体元件的外围电路区域的示意图。

20.图12是示出了根据示例实施例的行译码器的示意性框图。

21.图13是根据示例实施例的行译码器的示意性电路图。

22.图14是示出了图13中示出的行译码器的操作的定时图。

23.图15是示出了根据示例实施例的半导体器件的结构的示意图。

24.图16是示出了根据示例实施例的半导体器件的结构的示图。

25.图17是沿着图16的线iii-iii'截取的截面图。

26.图18是示出了根据示例实施例的半导体器件的结构的示意图。

27.图19是示出了根据示例实施例的半导体器件的结构的示图。

28.图20至图23是示出了根据示例实施例的半导体器件的示图。

29.图24是根据示例实施例的包括半导体器件的存储设备的示意性框图。

具体实施方式

30.在下文中,将参考附图描述示例实施例。

31.图1是根据示例实施例的半导体器件的示意性框图。

32.参照图1,半导体器件10可以包括控制逻辑电路12、单元区域13、页缓冲单元14、电压发生器15和/或行译码器16。半导体器件10还可以包括接口电路11,并且还可以包括列逻辑、预译码器、温度传感器、命令译码器、地址译码器、源极驱动器等。半导体器件10可以是存储数据的存储器件,例如,即使当其电力供应被中断时也保持所存储的数据的非易失性存储器件。

33.控制逻辑电路12可以控制半导体器件10中的总体操作。控制逻辑电路12可以响应于来自接口电路11的命令cmd和/或地址addr输出各种控制信号。例如,控制逻辑电路12可以输出电压控制信号ctrl_vol、行地址x-addr和列地址y-addr。

34.单元区域13可以包括多个存储块blk1至blkz(其中,z是正整数),并且多个存储块blk1至blkz均可以包括多个存储单元。例如,多个存储块blk1至blkz可以包括存储数据的主块和存储半导体器件10的操作所需的数据的至少一个备用块。单元区域13可以通过位线bl连接到页缓冲单元14,并可以通过字线wl、串选择线ssl和接地选择线gsl连接到行译码器16。

35.在示例实施例中,单元区域13可以包括三维存储单元阵列,并且三维存储单元阵列可以包括多个nand串。每个nand串可以包括分别连接到垂直堆叠在衬底上的字线的存储单元。美国专利公布no.7,679,133、美国专利公布no.8,553,466、美国专利公布no.8,654,587、美国专利公布no.8,559,235和美国专利申请公布no.2011/0233648通过引用整体合并于此。在示例实施例中,单元区域13可以包括二维存储单元阵列,并且二维存储单元阵列可以包括在行方向和列方向上布置的多个nand串。

36.页缓冲单元14可以包括多个页缓冲器pb1至pbn(其中,n是大于或等于3的整数)。多个页缓冲器pb1至pbn可以包括可以分别连接到存储单元的多条位线bl。页缓冲单元14可以响应于列地址y-addr选择至少一条位线bl。页缓冲单元14可以根据操作模式而操作为写驱动器或读出放大器。例如,在编程操作期间,页缓冲单元14可以在选定位线中施加与将编程的数据对应的位线电压。在读取操作期间,页缓冲单元14可以感测选定位线的电流或电压,以感测存储在存储单元中的数据。将通过编程操作在单元区域13中编程的数据和通过读取操作从单元区域13读取的数据可以通过接口电路11输入/输出。

37.电压发生器15可以基于电压控制信号ctrl_vol来生成用于执行编程操作、读取操作和擦除操作的各种类型的电压。例如,电压发生器15可以生成编程电压、读取电压、通过电压、编程验证电压、擦除电压等。在示例实施例中,控制逻辑电路12可以控制电压发生器15使用存储在备用块中的数据生成用于执行编程操作、读取操作和擦除操作的电压。由电压发生器15生成的一些电压可以由行译码器16作为字线电压vwl输入到字线wl,并且一些电压可以由源极驱动器输入到公共源极线。

38.行译码器16可以响应于行地址x-addr选择多条字线wl之一并选择多条串选择线ssl之一。例如,行译码器16可以在编程操作期间将编程电压和编程验证电压施加到选定字线,并可以在读取操作期间将读取电压施加到选定字线。

39.图2是根据示例实施例的半导体器件的示意图。

40.参照图2,根据示例的半导体器件50可以包括诸如第一垫(mat)51、第二垫52、第三垫53和第四垫54的多个垫和/或逻辑电路55。作为示例,多个垫51至54均可以包括参考图1描述的单元区域13、页缓冲单元14和行译码器16,并且逻辑电路55可以包括控制逻辑电路12和电压发生器15等。

41.根据示例实施例,多个垫51至54均可以彼此独立地操作。例如,当第一垫51执行编程操作以写入从外部存储控制器接收的数据时,逻辑电路55可以读取存储在第二垫52中的数据并将所读取的数据输出到外部实体。

42.多个垫51至54均可以包括单元区域51a、52a、53a或54a和外围电路区域51b、52b、53b或54b。单元区域可以包括存储单元,并且外围电路区域可以包括用于控制单元区域的电路,例如行译码器、页缓冲单元等。

43.在示例实施例中,多个垫51至54中的每一者的单元区域可以包括多个块。如上所述,多个块包括响应于来自逻辑电路55的命令而存储数据并输出所存储的数据的主块以及存储半导体器件50的操作所需的数据的备用块。

44.图3是根据示例实施例的半导体器件的存储块的示意性电路图。

45.图3中示出的存储块blki表示以三维结构形成在衬底上的三维存储块。例如,存储块blki中包括的多个nand串可以在垂直于衬底的方向上形成。

46.参照图3,存储块blki可以包括连接在位线bl1、bl2和bl3与公共源极线csl之间的多个nand串ns11至ns33。多个nand串ns11至ns33均可以包括串选择晶体管sst、多个存储单元mc1、mc2、...和mc8以及接地选择晶体管gst。在图3中,多个存储器nand串ns11至ns33均被示出为包括八个存储单元mc1、mc2、...和mc8,但是示例实施例不限于此。

47.串选择晶体管sst可以连接到对应的串选择线ssl1、ssl2和ssl3。多个存储单元mc1、mc2、...和mc8可以分别连接到对应的字线wl1、wl2、...和wl8。根据示例实施例,字线wl1、wl2、...和wl8中的至少一者可以被设置为虚设字线。接地选择晶体管gst可以连接到对应的接地选择线gsl1、gsl2和gsl3。串选择晶体管sst可以连接到对应的位线bl1、bl2和bl3,并且接地选择晶体管gst可以连接到公共源极线csl。

48.设置在相同的高度水平上的字线(例如,wl1)可以被公共地连接,并且接地选择线gsl1、gsl2和gsl3与串选择线ssl1、ssl2和ssl3可以分别彼此分开。在图3中,存储块blki被示出为连接到八条字线wl1、wl2、

…

和wl8以及三条位线bl1、bl2和bl3,但是示例实施例不限于此。

49.图4是示出了根据示例实施例的半导体器件中的单元区域和外围电路区域的布局的示意图。

50.图4是示出了根据示例实施例的半导体器件70中包括的垫当中的单个垫中的单元区域和外围电路区域的布局的示图。参照图4,外围电路区域可以围绕单元区域71a和71b设置。作为示例,行译码器72可以设置在与单元区域71a和71b中的每一者相邻的相对侧。页缓冲器73a和73b可以分别设置在单元区域71a和71b下方。行译码器72以及页缓冲单元73a和73b可以通过输入/输出电路74a和74b连接到控制半导体器件70的总体操作的逻辑电路和与外部设备通信的输入/输出接口。

51.作为示例,单元区域71a和71b中的每一者中包括的字线可以在水平方向上延伸,以连接到与单元区域71a和71b相邻的行译码器72。单元区域71a和71b中的每一者中包括的

位线可以在垂直方向上延伸,以连接到分别设置在单元区域71a和71b下方的页缓冲单元73a和73b。在图4中示出的示例实施例中,单元区域71a和71b、行译码器72、页缓冲器73a和73b、输入/输出电路74a和74b等可以形成在单个衬底上。

52.图5是示出了根据示例实施例的半导体器件的结构的示图,并且图6是沿着图5的线i-i'截取的截面图。

53.图5是示出了根据示例实施例的半导体器件100的一部分的俯视图。参照图5,半导体器件100可以包括单元区域cell和外围电路区域peri,并且单元区域cell可以包括单元阵列区域car和单元接触区域ctr。作为示例,单元阵列区域car可以是其中设置有沟道结构ch的区域,并且单元接触区域ctr可以是其中设置有单元接触cmc的区域。在图5中示出的示例实施例中,单元接触区域ctr可以设置在单元阵列区域car和外围电路区域peri之间。

54.一起参照图5和图6,单元阵列区域car可以包括在与衬底101的上表面垂直的第一方向(z轴方向)上堆叠的栅电极层110和绝缘层120、在第一方向上延伸以穿透栅电极层110和绝缘层120的沟道结构ch等。例如,栅电极层110和绝缘层120可以由字线切割口wc划分为多个块。另外,栅电极层110的一部分可以由上分隔层sc划分为多个单元电极层。每个沟道结构ch可以包括连接到衬底101的沟道层102、设置在沟道层102和栅电极层120之间的栅极电介质层103、漏极区104等。栅极电介质层103可以包括隧穿层、电荷存储层、阻挡层等,并且栅极电介质层103中包括的至少一个层可以被形成为围绕栅电极层110。漏极区104可以通过位线接触105连接到至少一条位线bl,并且位线bl可以连接到形成在外围电路区域peri中的页缓冲器。

55.单元接触区域ctr可以包括连接到栅电极层110的单元接触cmc、虚设沟道结构dch等。虚设沟道结构dch可以具有与沟道结构ch相同的结构。然而,与沟道结构ch不同,虚设沟道结构dch可以不连接到位线bl。栅电极层110可以在单元接触区域ctr中在与衬底101的上表面平行的第二方向(x轴方向)和第三方向(y轴方向)中的至少一者上形成台阶。单元接触cmc可以连接到栅电极层110,并可以通过字线173连接到形成在外围电路区域peri中的行译码器。字线173可以形成在层间绝缘层180中,层间绝缘层180形成在单元区域cell和外围电路区域peri中。

56.形成在外围电路区域peri中的行译码器可以设置为在第二方向上与单元区域cell相邻。行译码器可以包括在第一电源电压下操作的高电压元件hvtr以及在比第一电源电压低的第二电源电压下操作的低电压元件lvtr。高电压元件hvtr可以设置在第一阱区wa1中,并且低电压元件lvtr可以设置在第二阱区wa2和第三阱区wa3中。然而,根据示例实施例,高电压元件hvtr可以设置在掺杂有具有不同导电类型的杂质的多个阱区中。

57.第一阱区wa1可以是掺杂有具有第一导电类型的杂质(例如,p型杂质)的区域,并且第二阱区wa2可以是掺杂有具有与第一导电类型不同的第二导电类型的杂质(例如,n型杂质)的区域。第二阱区wa2可以围绕第一阱区wa1,使得第一阱区wa1可以被设置为袋状p阱。在图5和图6的示例实施例中示出的高电压元件hvtr是高电压nmos元件。当高电压元件hvtr还包括高电压pmos元件时,与第一阱区wa1不同,高电压pmos元件可以形成在掺杂有具有第二导电类型的杂质的单独的阱区中。

58.至少一个低电压元件lvtr可以形成在围绕第一阱区wa1的第二阱区wa2中。作为示例,在第二阱区wa2中形成的低电压元件lvtr可以是低电压pmos元件。在低电压元件lvtr当

中,低电压pmos元件可以设置在围绕设置为袋状p阱的第一阱区wa1的第二区域wa2中,因此,可以增加行译码器和外围电路区域peri的集成度。

59.在示例实施例中,一些低电压元件lvtr可以形成在第三阱区wa3中。第三阱区wa3可以是掺杂有与第一阱区wa1具有相同的第一导电类型的杂质的阱区,但可以具有与第一阱区wa1的掺杂浓度不同的掺杂浓度。形成在第三阱区wa3中的低电压元件lvtr可以是低电压nmos元件。

60.作为示例,在行译码器中包括的元件hvtr和lvtr当中,形成在第一阱区wa1中的高电压元件hvtr可以提供通过垂直接触vc直接连接到字线173的通路元件(pass element),并且低电压元件lvtr可以提供驱动通路元件的驱动器电路。在示例实施例中,驱动器电路可以包括块译码器、高电压开关电路、上拉电路等,并且稍后将描述驱动器电路的配置和操作。

61.参照图6,每个高电压元件hvtr可以包括栅极结构130和源极/漏极区140,并且每个低电压元件lvtr可以包括栅极结构150和源极/漏极区160。元件接触171和下互连件172可以连接到源极/漏极区140和160,并且栅极结构130和150也可以连接到栅极接触。

62.每个高电压元件hvtr的栅极结构130可以包括高电压栅极绝缘层131、高电压栅极132、栅极间隔物133等,并且高电压栅极绝缘层131可以设置在高电压栅极132和衬底101之间。每个低电压元件lvtr的栅极结构150可以包括低电压栅极绝缘层151、低电压栅极152和栅极间隔物153,并且低电压栅极绝缘层151可以设置在低电压栅极152和衬底101之间。

63.在示例实施例中,高电压栅极绝缘层131的厚度可以大于低电压栅极绝缘层151的厚度。高电压栅极132和低电压栅极152可以具有相同的结构。因此,高电压栅极132的上表面可以设置为高于低电压栅极152的上表面,或者衬底101的一部分可以在其中形成有高电压元件hvtr的区域中凹进,使得高电压栅极132的上表面和低电压栅极152的上表面可以设置在相同的高度水平处。稍后将描述其中形成有高电压元件hvtr和低电压元件lvtr的结构。

64.在图5和图6中示出的示例实施例中,第一阱区wa1可以设置为在第二方向上距离单元区域cell最远。然而,这仅是示例实施例,并且第一阱区wa1可以设置为靠近单元区域cell。在下文中,将参考图7和图8对此进行描述。

65.图7是示出了根据示例实施例的半导体器件的结构的示图,并且图8是沿着图7的线ii-ii'截取的截面图。

66.参照图7和图8,半导体器件200中包括的单元区域cell的结构可以类似于以上参考图5和图6描述的结构。作为示例,单元区域cell可以包括在第一方向(z方向)上堆叠的栅电极层210和绝缘层220以及通过栅电极层210和绝缘层220连接到衬底201的沟道结构ch。沟道结构ch可以通过位线接触205连接到位线bl,并且每个沟道结构ch可以包括沟道层202、栅极电介质层203、漏极区204等。栅电极层210可以连接到单元接触cmc,并且虚设沟道结构dch可以形成在单元接触cmc之间。

67.在图7和图8中示出的示例实施例中,外围电路区域peri的第一阱区wa1可以设置为靠近单元区域cell。因此,可以缩短连接提供通路元件的高电压元件hvtr和单元接触cmc的字线273的长度。例如,在图7和图8中示出的示例实施例中,提供通路元件的高电压元件hvtr可以设置在提供驱动器电路的低电压元件lvtr与单元区域cell之间。

68.在外围电路区域peri中,高电压元件hvtr可以形成在第一阱区wa1中,至少一个低电压元件lvtr可以形成在围绕第一阱区wa1的第二阱区wa2中,并且一些低电压元件lvtr可以形成在第三阱区wa3中。高电压元件hvtr和低电压元件lvtr中的每一者的配置可以类似于以上参考图6描述的示例实施例的配置。

69.此外,在图6和图8中,类似的附图标记(例如,130和230;131和231;132和232;133和233;150和250;151和251;152和252;153和253;171和271;172和272;180和280;等等)指示相同的构成组件。

70.图9至图11分别是示出了根据示例实施例的半导体元件的外围电路区域的示意图。

71.参照图9,根据示例实施例的半导体器件300的外围电路区域可以包括多个电路元件hvtr和lvtr1至lvtr3。作为示例,多个电路元件hvtr和lvtr1至lvtr3可以是连接到字线以提供用于驱动存储单元的行译码器的元件,并且可以包括在第一电源电压下操作的高电压元件hvtr和在比第一电源电压低的第二电源电压下操作的低电压元件lvtr1至lvtr3。元件隔离层303可以形成在至少一些电路元件hvtr和lvtr1至lvtr3之间。

72.高电压元件hvtr可以包括栅极结构310和源极/漏极区320,并且栅极结构310可以包括高电压栅极绝缘层311、高电压栅极312、栅极间隔物313等。低电压元件lvtr1至lvtr3均可以包括栅极结构330和源极/漏极区340,并且栅极结构330可以包括低电压栅极绝缘层331、低电压栅极332、栅极间隔物333等。

73.高电压元件hvtr可以设置在掺杂有具有第一导电类型的杂质的第一阱区wa1中,并且第一阱区wa1可以是掺杂有p型杂质的区域。第一阱区wa1可以是被第二阱区wa2围绕的袋状p阱区,并且第二阱区wa2可以掺杂有具有第二导电类型的杂质。具有第二导电型的杂质可以是n型杂质。

74.在低电压元件lvtr1至lvtr3当中,第一低电压元件lvtr1可以设置在第一阱区wa1中,并且第二低电压元件lvtr2可以设置在第二阱区wa2中。由于除了高电压元件hvtr之外,第一低电压元件lvtr1也设置在第一阱区wa1中,因此形成在第一阱区wa1中的nmos元件hvtr和lvtr1中的至少一者中包括的栅极绝缘层的厚度可以与形成在第二阱区wa2中的第二低电压元件lvtr2中包括的栅极绝缘层的厚度相同。

75.如上所述,与高电压栅极绝缘层311的厚度相比,低电压栅极绝缘层331可以具有相对小的厚度。参照图9,衬底301可以在其中设置有高电压元件hvtr的区域中具有第一厚度t1,并且可以在其中设置有第一低电压元件lvtr1的区域中具有大于第一厚度t1的第二厚度t2,因此,第一阱区wa1和第二阱区wa2可以具有不同的厚度。

76.作为示例,第一厚度t1与第二厚度t2之间的差可以对应于高电压栅极绝缘层311的厚度t

ox1

与低电压栅极绝缘层331的厚度t

ox2

之间的差。因此,高电压栅极绝缘层311的上表面和低电压栅极绝缘层331的上表面可以设置在相同的高度水平上。在示例实施例中,可以通过在其中将形成高电压元件hvtr的区域中去除衬底301的一部分并且形成阱区wa1至wa3和电路元件hvtr和lvtr1至lvtr3来形成外围电路区域,如图10中示出地。

77.第三低电压元件lvtr3可以设置在第三阱区wa3中。第三阱区wa3可以是与第一阱区wa1和第二阱区wa2分开的区域,并且可以掺杂有具有与第一阱区wa1相同的第一导电类型的杂质。然而,第三阱区wa3的杂质掺杂浓度可以不同于第一阱区wa1的杂质掺杂浓度。另

外,负电压可以作为高电压元件hvtr和第一低电压元件lvtrl的体偏置电压输入到第一阱区wa1,并且接地电压可以作为第三低电压元件lvtr3的体偏置电压施加到第三阱区wa3。

78.因为负电压输入到第一阱区wa1,所以第一低电压元件lvtr1可以被选择为行译码器中包括的低电压nmos元件当中的其中体偏置电压为负电压的元件。作为示例,第一低电压元件lvtr1可以是高电压开关电路中包括的元件。

79.参照图10,根据示例实施例的半导体器件300a的外围电路区域可以包括多个电路元件hvtr和lvtr1至lvtr4。与图9中示出的示例实施例相比,多个电路元件hvtr和lvtr1至lvtr4可以是提供连接到字线的行译码器的元件,并且还可以包括第四低电压元件lvtr4。

80.第四低电压元件lvtr4可以形成在与第一阱区wa1至第三阱区wa3分开的第四阱区wa4中,并且第四阱区wa4可以掺杂有具有与第二阱区wa2相同的第二导电类型的杂质。因此,第四低电压元件lvtr4可以是低电压pmos元件。第四阱区wa4的杂质浓度可以与第二阱区wa2的杂质浓度相同或不同。作为示例,第四阱区wa4的杂质浓度可以高于第二阱区wa2的杂质浓度。

81.在参考图9和图10描述的示例实施例中,衬底301可以在其中形成有高电压元件hvtr的区域中具有第一厚度t1,并且可以在另一区域中具有大于第一厚度t1的第二厚度t2。如图9和图10所示,第一阱区wa1的下表面可以形成在与第三阱区wa3和第四阱区wa4的下表面相同的高度水平上,并且第二阱区wa2的下表面可以设置为相对较低。另外,第一阱区wa1在其中形成有高电压元件hvtr的区域中的厚度可以小于第一阱区wa1在其中形成有第一低电压元件lvtr1的区域中的厚度。然而,这仅是示例,并且根据半导体器件300的制造方法等,第一阱区wa1的下表面可以在其中形成有高电压元件hvtr的区域中形成在相对较低的位置。

82.参照图11,根据示例实施例的半导体器件400的外围电路区域可以包括多个电路元件hvtr和lvtr1至lvtr3。多个电路元件hvtr和lvtr1至lvtr3可以是提供连接到字线的行译码器的元件。

83.与图9和图10中示出的示例实施例不同,在图11中示出的示例实施例中,衬底301可以具有一致的厚度。因此,衬底301的上表面可以在其中形成有高电压元件hvtr的区域和其中形成有低电压元件lvtr1至lvtr3的区域中没有台阶。因此,第一阱区wa1也可以具有一致的厚度。

84.如上所述,高电压元件hvtr中包括的高电压栅极绝缘层411的厚度可以大于低电压元件lvtr1至lvtr3中的每一者中包括的低电压栅极绝缘层431的厚度。参照图11,高电压栅极绝缘层411的第一厚度t

ox1

可以大于低电压栅极绝缘层431的第二厚度t

ox2

,因此,高电压栅极绝缘层411的上表面可以设置为高于低电压栅极绝缘层431的顶表面。此外,因为高电压栅极412和低电压栅极432具有相同的结构,所以高电压栅极412的上表面可以设置为高于低电压栅极432的上表面。

85.参照图9至图11,在平行于衬底301和401的上表面的一个方向(x轴方向)上,第一低电压元件lvtr1可以形成于在第一阱区wa1中形成的高电压元件hvtr和在第二阱区wa2中形成的第二低电压元件lvtr2之间。另外,第一低电压元件lvtr1可以设置为比高电压元件hvtr更靠近第一阱区wa1和第二阱区wa2之间的边界。然而,这仅仅是示例,并且元件的布置可以进行各种改变。作为示例,高电压元件hvtr可以设置为比第一低电压元件lvtr1更靠近

第一阱区wa1和第二阱区wa2之间的边界。

86.此外,在图10和图11中,类似的附图标记(例如,310和410;311和411;312和412;313和413;330和430;331和431;332和432;333和433;340和440;303和403;320和420;等等)指示相同的构成组件。

87.图12是示出了根据示例实施例的行译码器的示意性框图。

88.参照图12,在根据示例实施例的半导体器件500中,行译码器510可以通过接地选择线gsl、字线wl和/或串选择线ssl连接到单元区域520。作为示例,行译码器510可以通过接地选择线gsl、字线wl和串选择线ssl电连接到单元区域520中包括的存储单元的栅电极。

89.行译码器510可以包括块译码器511、高电压开关电路512、上拉电路513和/或通路元件单元514。块译码器511可以是选择单元区域520中的单个存储块的电路。高电压开关电路512可以提高从块译码器511输出的逻辑值的电平以输出块选择信号,并且通路元件单元514中包括的通路元件可以通过块选择信号而切换。

90.通路元件单元514可以包括通过接地选择线gsl、字线wl和串选择线ssl连接到单元区域520的多个通路元件。通常,与用于驱动电路的电压相比,由通路元件供应到单元区域520的电压可以具有相对高的电平。因此,通路元件可以被实现为可以耐受相对高的电压电平的高电压元件,并且每个通路元件的栅极绝缘层可以具有相对大的厚度,以耐受栅极结构与源极/漏极区之间的高电压差。上拉电路513可以响应于从块译码器511输出的信号将高电压输入到通路元件的栅极。

91.负电压vneg可以被输入到高电压开关电路512和通路元件单元514。作为示例,负电压vneg可以作为体偏置电压被输入到高电压开关电路512和通路元件单元514中包括的至少一些元件。

92.在示例实施例中,提供通路元件的高电压nmos元件可以形成在掺杂有p型杂质的第一阱区中并形成为袋状p阱区。另外,包括在高电压开关电路512中并接收作为体偏置电压的负电压vneg的低电压nmos元件中的至少一者可以一起形成在第一阱区中。至少一个低电压pmos元件可以形成在围绕第一阱区并掺杂有n型杂质的第二阱区中,以提高包括在行译码器510中的电路元件的集成度并且缩短电路元件之间的连接路径,从而可以改善半导体器件500的性能。

93.图13是根据示例实施例的行译码器的示意性电路图,并且图14是示出了图13中示出的行译码器的操作的定时图。

94.首先参照图13,行译码器600可以包括块译码器610、高电压开关电路620、上拉电路630、通路元件单元640等。块译码器610可以包括nand门611和/或反相器612,并且可以对由行地址提供的译码信号o、p、q和r执行与非逻辑运算。作为示例,块译码器610还可以包括确定从行地址选择的块是否是坏块并且中断nand门的输出的电路。反相器612可以使nand门611的输出反相。

95.高电压开关电路620可以响应于nand门611和反相器612的输出信号而操作。高电压开关电路620可以包括pmos元件pm1和pm2、nmos元件nm1至nm5和/或耗尽模式nmos元件nm6。

96.作为示例,当nand门611的输出具有低电平时,第一pmos元件pm1可以导通并且第二pmos元件pm2可以断开。因此,低电源电压vdd可以输入到第二nmos元件nm2和第四nmos元

件nm4中的每一者的栅极,并且第二nmos元件nm2和第四nmos元件nm4可以导通。因此,低电源电压vdd可以输入到第三nmos元件nm3和第四nmos元件nm4之间的节点。

97.当第三nmos元件nm3和第四nmos元件nm4之间的节点上的电压可以升高至耗尽模式nmos元件nm6的阈值电压时,耗尽模式nmos元件nm6可以断开。因此,当nand门611的输出处于低电平状态时,高电压开关电路620可以与通路元件pt的栅极所连接的块字线blkwl电隔离。在一些示例实施例中,通路元件pt可以由通过上拉电路630输入到块字线blkwl的高电源电压vpp而导通。

98.相比之下,当nand门611的输出处于高电平状态时,高电压开关电路620可以连接到块字线blkwl。当nand门611的输出处于高电平状态时,第一pmos元件pm1可以断开,同时反相器612的输出具有低电平,使得第二pmos元件pm2可以导通。因此,低电源电压vdd可以输入到第一nmos元件nm1和第三nmos元件nm3中的每一者的栅极,以使第一nmos元件nm1和第三nmos元件nm3导通。

99.因为第三nmos元件nm3导通,所以与其中nand门611的输出处于低电平状态的示例实施例不同,负电压vneg可以输入到第三nmos元件nm3和第四nmos元件nm4之间的节点。负电压vneg可以通过耗尽模式元件nm6输入到块字线blkwl。作为示例,当块字线blkwl上的电压是接地电压时,负电压vneg可以通过耗尽模式元件nm6输入到块字线blkwl。当块字线blkwl上的电压为高电源电压vpp时,块字线blkwl上的电压可以通过耗尽模式元件nm6放电。

100.负电压vneg可以作为偏置电压输入到通路元件pt的主体。当nand门611的输出处于高电平状态时,通过高电压开关电路620连接到通路元件pt的栅极的块字线blkwl上的电压可以降低至负电压vneg,使得通路元件pt可以断开。根据示例实施例,负电压vneg可以供应到串选择线ssl和接地选择线gsl中的至少一者。在高电压开关电路620中,pmos元件pm1和pm2以及第一nmos元件nm1至第四nmos元件nm4可以操作为电平移位器。

101.上拉电路630可以连接在高电源电压vpp和块字线blkwl之间,并可以响应于nand门611的输出将高电源电压vpp输入到块字线blkwl。参照图13,上拉电路630可以包括耗尽模式元件nh1和高电压pmos元件ph1。耗尽模式元件nh1的漏极可以接收高电源电压vpp,并且耗尽模式元件nh1的栅极可以连接到块字线blkwl。高电压pmos元件ph1的漏极可以连接到块字线blkwl,并且高电压pmos元件ph1的栅极可以连接到nand门611的输出端子。

102.当nand门611的输出处于低电平状态时,高电压pmos元件ph1可以导通,并且耗尽模式元件nh1的阈值电压可以输入到块字线blkwl。因此,块字线blkwl上的电压可以升高。块字线blkwl上的电压可以输入到耗尽模式元件nh1的栅极,以使耗尽模式元件nh1导通。结果,高电源电压vpp可以输入到块字线blkwl。如上所述,当nand门611的输出处于低电平状态时,高电压开关电路620可以与块字线blkwl隔离,从而负电压vneg不会输入到块字线blkwl。因此,通路元件pt可以由输入到块字线blkwl的高电源电压vpp而导通。

103.当nand门611的输出处于高电平状态时,高电压pmos元件ph1可以断开,并且高电压vpp不会输入到块字线blkwl。如上所述,当nand门611的输出处于高电平状态时,高电压开关电路620可以连接到块字线blkwl,并且负电压vneg可以输入到块字线blkwl,从而通路元件pt可以由输入到块字线blkwl的负电压vneg而断开。

104.在图13中示出的电路图中,负电压vneg可以作为偏置电压输入到一些nmos元件

(例如,通路元件pt和第一nmos元件nm1至第五nmos元件nm5)的主体。根据示例实施例,第一nmos元件nm1至第五nmos元件nm5可以是高电压nmos元件或低电压nmos元件。当第一nmos元件nm1至第五nmos元件nm5为高电压nmos元件时,第一nmos元件nm1至第五nmos元件nm5可以与通路元件pt一起形成在单个袋状p阱区中。

105.在示例实施例中,即使当高电压开关电路620中包括的第一nmos元件nm1至第五nmos元件nm5为低电压nmos元件时,作为高电压nmos元件的通路元件pt以及作为低电压nmos元件的第一nmos元件nm1至第五nmos元件nm5也可以形成在单个袋状p阱区中,如以上参考图5至图11描述的。因此,可以减小其中设置有行译码器600的区域的面积,并且可以提高包括行译码器600的半导体器件的集成度。

106.例如,参照图9,形成在作为袋状p阱区的第一阱区wa1中的高电压元件hvtr可以是一个通路元件pt,并且形成在第一阱区wa1中的第一低电压元件lvtr1可以是第一nmos元件nm1至第五nmos元件nm5之一。另外,形成在围绕第一阱区wa1的第二阱区wa2中的第二低电压元件lvtr2可以是高电压开关电路620的pmos元件pm1和pm2之一,并且形成在第三阱区wa3中的第三低电压元件lvtr3可以是包括在反相器612中的pmos元件。

107.图14是示出了图13中示出的行译码器600的操作的定时图。参照图14,输入到块译码器610的nand门611的译码信号o、p、q和r可以在编程操作期间具有高电平。译码信号o、p、q和r的高电平可以是低电源电压vdd。因此,nand门611的输出可以具有低电平,并且可以选择连接到行译码器600的存储块。

108.如上所述,当nand门611的输出处于低电平状态时,高电压开关电路620可以通过耗尽模式元件nm6与块字线blkwl隔离,因此,负电压vneg不会输入到块字线blkwl。另一方面,因为nand门611的输出处于低电平状态,所以高电源电压vpp可以通过上拉电路630输入到块字线blkwl并且通路元件pt可以导通。在这种情况下,负电压vneg可以作为偏置电压输入到通路元件pt的主体。

109.当通路元件pt导通时,编程电压vpgm可以作为用于编程操作的选定字线信号sn输入到选定字线wln。当用于输入编程电压vpgm的编程操作完成时,可以执行验证操作。在验证操作期间,输入到选定字线wln的选定字线信号sn的电平可以为负电压vneg。

110.图15是示出了根据示例实施例的半导体器件的结构的示意图。

111.参照图15,半导体器件700可以包括在第一方向(z轴方向)上堆叠的第一区域710和第二区域720。第一区域710可以是外围电路区域,并且可以包括形成在第一衬底上的行译码器dec、页缓冲器pb和/或外围电路pc。作为示例,外围电路pc可以包括电压发生器、源极驱动器、输入/输出电路等。

112.第二区域720可以是单元区域,并且可以包括形成在第二衬底上的存储单元阵列mca以及第一贯通互连区域tb1和第二贯通互连区域tb2。将第一区域710和第二区域720彼此连接并在垂直方向上延伸的贯通互连件可以设置在第一贯通互连区域tb1和第二贯通互连区域tb2中的每一者中。包括在每个存储单元阵列mca中的单元块cbk可以在第二方向(x轴方向)上延伸,并可以在第三方向(y轴方向)上布置。根据示例实施例,至少一个虚设块可以设置在至少一些单元块cbk之间。

113.第一区域710可以包括用于实现包括在外围电路区域中的行译码器dec、页缓冲器pb、外围电路pc等的多个电路元件以及将电路元件彼此连接的互连图案。电路元件可以分

为低电压元件和高电压元件。然而,根据示例实施例,还可以提供在与输入到低电压元件的低电源电压和输入到高电压元件的高电源电压不同的电源电压下操作的元件。

114.在第一区域710中,在高电压元件当中,高电压nmos元件可以被掺杂有n型杂质的n阱区围绕,并且可以形成在掺杂有p型杂质的袋状p阱区中。在示例实施例中,包括在低电压元件中的低电压nmos元件中的至少一者可以与高电压nmos元件一起形成在袋状p阱区中。一起形成在袋状p阱区中的高电压nmos元件和低电压nmos元件可以接收相同的体偏置电压。

115.每个低电压nmos元件的栅极绝缘层的厚度可以小于每个高电压nmos元件的栅极绝缘层的厚度。因此,当低电压nmos元件与高电压nmos元件一起形成在具有平坦的上表面的袋状p阱区中时,高电压nmos元件的栅极上表面可以设置在比低电压nmos元件的栅极上表面高的高度水平上。或者,可以在其中形成有高电压nmos元件的区域中预先去除衬底的一部分,以使高电压nmos元件的栅极上表面和低电压nmos元件的栅极上表面形成在相同或基本上相同的高度水平上。

116.图16是示出了根据示例实施例的半导体器件的结构的示图,并且图17是沿着图16的线iii-iii'截取的截面图。

117.参照图16和图17,单元区域cell和外围电路区域peri可以在第一方向(z轴方向)上堆叠。半导体器件800的单元区域cell可以包括单元阵列区域car和单元接触区域ctr。作为示例,单元阵列区域car可以是其中设置有沟道结构ch的区域,并且单元接触区域ctr可以是其中设置有单元接触cmc的区域。每个沟道结构ch可以包括沟道层802、栅极电介质层803、漏极区804等。漏极区804可以通过位线接触805连接到至少一条位线bl。

118.外围电路区域peri可以包括第一衬底801a、形成在第一衬底801a上的多个电路元件hvtr和lvtr和/或连接到多个电路元件hvtr和lvtr的互连图案871和872。多个电路元件hvtr和lvtr可以包括高电压元件hvtr和低电压元件lvtr,并且互连图案871和872可以包括元件接触871和下互连件872。

119.高电压元件hvtr可以在相对高的电源电压下操作,并可以包括栅极结构830和源极/漏极区840。低电压元件lvtr可以在相对低的电源电压下操作,并可以包括栅极结构850和源极/漏极区860。高电压元件hvtr的栅极结构830可以包括高电压栅极绝缘层831、高电压栅极832、栅极间隔物833等。低电压元件lvtr的栅极结构850可以包括低电压栅极绝缘层851、低电压栅极852、栅极间隔物853等。

120.高电压栅极绝缘层831的厚度可以大于低电压栅极绝缘层851的厚度,并且高电压栅极832和低电压栅极852可以具有相同的结构。因此,高电压栅极832的上表面可以设置在比低电压栅极852的上表面高的高度水平上。或者,可以去除第一衬底801a的一部分,以在其中形成有高电压元件hvtr的区域中形成凹进区域,以使高电压栅极832的上表面和低电压栅极852的上表面处于相同的高度水平上。

121.单元阵列区域car可以包括在与第二衬底801b的上表面垂直的第一方向上堆叠的栅电极层810和绝缘层820、穿透栅电极层810和绝缘层820的沟道结构ch等。每个沟道结构ch的配置可以类似于以上参考图6描述的配置。

122.单元接触区域ctr可以包括连接到栅电极层810的单元接触cmc和贯通互连件tvc。在其中设置有贯通互连件tvc的区域中,牺牲层815可以保留而不替换为栅电极层810。因

此,贯通互连件tvc可以与栅电极层810分开,并且可以穿透牺牲层815和绝缘层820,以连接到设置在单元接触区域ctr下方的外围电路区域peri的电路元件hvtr和lvtr。在图17中示出的示例实施例中,具有连接到贯通互连件tvc的源极/漏极区的高电压元件hvtr可以是外围电路区域peri中的行译码器中包括的通路元件当中的单个通路元件。

123.此外,在图6和图17中,类似的附图标记(例如,173和873;180、880和870;等等)指示相同的构成组件。

124.图18是示出了根据示例实施例的半导体器件的结构的示意图。

125.参照图18,半导体器件900可以包括在第一方向(z轴方向)上堆叠的第一区域910和第二区域920。第一区域910可以是外围电路区域,并且第二区域920可以是单元区域。第一区域910和第二区域920中的每一者的配置可以类似于以上参考图15描述的配置。

126.与以上参考图15描述的示例实施例不同,在图18中示出的示例实施例中,包括外围电路区域的第一区域910可以在倒置的同时结合到第二区域920。因此,包括在第一区域910中并提供行译码器dec、页缓冲器pb和外围电路pc的电路元件以及包括在第二区域920中的栅电极层、沟道结构、位线等可以在第一方向上设置在第一区域910的第一衬底和第二区域920的第二衬底之间。

127.设置在第一区域910中的电路元件可以包括高电压元件和低电压元件。高电压元件当中的至少一些高电压nmos元件可以被掺杂有n型杂质的n阱区围绕,并可以形成在掺杂有p型杂质的p阱区中。在示例实施例中,包括在低电压元件中的低电压nmos元件中的至少一者可以与高电压nmos元件一起形成在袋状p阱区中,以提高半导体器件900的集成度。考虑到操作特性,接收相同的体偏置电压的高电压nmos元件和低电压nmos元件可以一起形成在一个袋状p阱区中。

128.图19是示出了根据示例实施例的半导体器件的结构的示图。

129.参照图19,半导体器件1000可以包括在第一方向(z轴方向)上堆叠的单元区域cell和外围电路区域peri。与以上参考图17描述的示例实施例不同,外围电路区域peri可以在倒置的同时与单元区域cell堆叠。因此,外围电路区域peri的电路元件hvtr和lvtr以及单元区域cell的栅电极层1010和沟道结构ch等可以设置在外围电路区域peri的第一衬底1001a和单元区域cell的第二衬底1001b之间。每个沟道结构ch可以包括沟道层1002、栅极电介质层1003、漏极区1004等。漏极区1004可以通过位线接触1005连接到至少一条位线bl。

130.作为示例,半导体器件1000可以具有芯片到芯片(c2c)结构。c2c结构可以是指通过下述步骤所形成的结构:在第一晶片上制造包括外围电路区域peri的第一芯片,在与第一晶片不同的第二晶片上制造包括单元区域cell的第二芯片,然后使用接合方式将第一芯片与第二芯片彼此连接。作为示例,接合方式可以是指将形成在第一芯片的最上面的互连图案层上的接合焊盘与形成在第二芯片的最上面的互连图案层上的接合焊盘彼此物理连接且电连接的方式。例如,当接合焊盘由铜(cu)形成时,接合方式可以是cu与cu接合方式。接合焊盘也可以由铝(al)或钨(w)形成。

131.外围电路区域peri可以包括多个电路元件hvtr和lvtr以及连接到多个电路元件hvtr和lvtr的互连图案1071和1072。多个电路元件hvtr和lvtr可以包括高电压元件hvtr和低电压元件lvtr,并且互连图案1071和1072可以包括元件接触1071和下互连件1072。下互

连件1072可以连接到用于将单元区域cell与外围电路区域peri彼此耦接的接合焊盘1110。

132.单元区域cell可以包括单元阵列区域car和单元接触区域ctr。单元阵列区域car可以是其中设置有沟道结构ch的区域,并且单元接触区域ctr可以是其中设置有单元接触cmc的区域。单元阵列区域car可以包括在与第二衬底1001b的上表面垂直的第一方向上堆叠的栅电极层1010和绝缘层1020、穿透栅电极层1010和绝缘层1020的沟道结构ch以及连接到沟道结构ch的位线bl。沟道结构ch的配置可以类似于以上参考图6描述的配置。单元接触区域ctr可以包括连接到栅电极层1010的单元接触cmc。

133.位线bl和单元接触cmc可以连接到形成在单元区域cell上的接合焊盘1120。如上所述,在c2c结构中,外围电路区域peri的接合焊盘1110与单元区域cell的接合焊盘1120可以以接合方式彼此连接。

134.为了将外围电路区域peri和单元区域cell高效地彼此连接,可以根据单元阵列区域car和单元接触区域ctr的布置来确定包括在外围电路区域peri中的电路的布置。作为示例,通过位线bl连接到沟道结构ch的页缓冲器可以在外围电路区域peri中设置在与单元阵列区域car堆叠的区域中。另外,连接到栅电极层1010的行译码器可以在外围电路区域peri中设置在与单元接触区域ctr堆叠的区域中。

135.在外围电路区域peri中,高电压元件hvtr可以在相对高的电源电压下操作,并且低电压元件lvtr可以在相对较低的电源电压下操作。高电压元件hvtr和低电压元件lvtr的配置可以类似于以上参考图17描述的配置。

136.作为示例,高电压栅极绝缘层1031的厚度可以大于低电压栅极绝缘层1051的厚度,并且高电压栅极1032和低电压栅极1052可以具有相同的结构。因此,高电压栅极1032的上表面可以设置在比低电压栅极1052的上表面高的高度水平上。或者,可以通过在其中形成有高电压元件hvtr的区域中去除第一衬底1001a的一部分来形成凹进区域,使得高电压栅极1032的上表面和低电压栅极1052的上表面处于相同的高度水平上。在图19中示出的示例实施例中,通过接合焊盘1110和1120以及互连图案1071和1072直接连接到一个单元接触cmc的高电压元件hvtr可以是包括在行译码器中的通路元件。

137.此外,在图6和图19中,类似的附图标记(例如,140和1040;153和1053;133和1033;130和1030;160和1060;等等)指示相同的构成组件。

138.图20至图23是示出了根据示例实施例的半导体器件的示图。

139.图20和图21可以示出为了描述根据示例实施例的半导体器件而提供的比较示例,并且图22和图23可以是示出了根据示例实施例的半导体器件的示图。

140.参照图20和图21,根据比较示例的半导体器件2000可以包括多个电路元件hvtr、lvtr1和lvtr2,并且多个电路元件hvtr、lvtr1和lvtr2可以设置在多个阱区wa1至wa4中。作为示例,高电压元件hvtr可以设置在第一阱区wa1中,并且第一阱区wa1可以设置为被第二阱区wa2围绕的袋状p阱。因此,高电压元件hvtr可以是高电压nmos元件。

141.在低电压元件lvtr1和lvtr2当中,第一低电压元件lvtr1可以是在掺杂有p型杂质的第三阱区wa3中形成的低电压nmos元件。第二低电压元件lvtr2可以是在掺杂有n型杂质的第四阱区wa4中形成的低电压pmos元件。第三阱区wa3的杂质浓度可以低于第一阱区wa1的杂质浓度。

142.参照图21,高电压元件hvtr可以包括栅极结构2030和源极/漏极区2040,并且栅极

结构2030可以包括高电压栅极绝缘层2031、高电压栅极2032、栅极间隔物2033等。高电压栅极绝缘层2031可以设置在高电压栅极2032和衬底2001之间。低电压元件lvtr1和lvtr2均可以包括栅极结构2050和源极/漏极区2060,并且栅极结构2050可以包括低电压栅极绝缘层2051、低电压栅极2052、栅极间隔物2053等。在示例实施例中,高电压栅极绝缘层2031的厚度t

ox1

可以等于低电压栅极绝缘层2051的厚度t

ox2

。

143.参照图20和图21,在围绕第一阱区wa1的第二阱区wa2中没有形成元件,并且第二阱区wa2和第四阱区wa4可以通过预定的或可选地期望的间隙彼此分开。因此,在有限区域中应该尽可能多地设置电路元件hvtr、lvtr1和lvtr2的半导体器件2000的集成度会降低。

144.参照图22和图23,根据示例实施例的半导体器件2100可以包括多个电路元件hvtr和lvtr1至lvtr3,并且多个电路元件hvtr和lvtr1至lvtr3可以设置在多个阱区wa1至wa3中。作为示例,高电压元件hvtr可以设置在第一阱区wa1中,并且第一阱区wa1可以设置为围绕第二阱区wa2的袋状p阱。因此,类似于参考图20和图21描述的示例实施例,高电压元件hvtr可以是高电压nmos元件。

145.在低电压元件lvtr1至lvtr3中,第一低电压元件lvtr1可以与高电压元件hvtr一起形成在第一阱区wa1中。作为示例,在低电压元件lvtr1至lvtr3当中,可以选择具有与高电压元件hvtr相同的体偏置电压的元件作为第一低电压元件lvtr1。第二低电压元件lvtr2可以是在围绕第一阱区wa1并形成在掺杂有n型杂质的第二阱区wa2中的低电压pmos元件。

146.第三低电压元件lvtr3可以是在掺杂有p型杂质的第三阱区wa3中形成的低电压nmos元件。在图22和图23中示出的示例实施例中,在低电压nmos元件当中,可以选择具有与高电压元件hvtr相同的体偏置电压的元件作为将形成在第一阱区wa1中的第一低电压元件lvtr1。另外,可以选择具有与高电压元件hvtr的体偏置电压不同的体偏置电压的元件作为将形成在第三阱区wa3中的第三低电压元件lvtr3。

147.参照图23,高电压元件hvtr可以包括栅极结构2130和源极/漏极区2140,并且栅极结构2130可以包括高电压栅极绝缘层2131、高电压栅极2132、栅极间隔物2133等。高电压栅极绝缘层2131可以设置在高电压栅极2132和衬底2101之间。低电压元件lvtr1至lvtr3中的每一者可以包括栅极结构2150和源极/漏极区2160,并且栅极结构2150可以包括低电压栅极绝缘层2151、低电压栅极2152、栅极间隔物2153等。

148.在示例实施例中,高电压栅极绝缘层2131的厚度t

ox1

可以大于低电压栅极绝缘层2151的厚度t

ox2

。高电压栅极2132和低电压栅极2152可以具有相同的结构。参照图23,高电压栅极2132的上表面和低电压栅极2152的上表面可以因在其中形成有高电压元件hvtr的区域中去除了衬底2101的一部分而处于相同的高度水平上。因此,如图23所示,衬底可以在其中形成有第一阱区wa1和第二阱区wa2的区域中具有第一厚度t1,而衬底可以在其中形成有第三阱区wa3的区域中具有大于第一厚度t1的第二厚度t2。然而,根据示例实施例,由于未去除衬底的一部分,高电压栅极2132的上表面可以处于比低电压栅极2152的上表面高的高度水平上。

149.参照图22和图23,高电压nmos元件和低电压nmos元件可以一起设置在第一阱区wa1中,并且低电压pmos元件也可以设置在围绕第一阱区wa1的第二阱区wa2中。因此,与以上参考图20和图21描述的比较示例相比,可以在较小区域中设置许多电路元件hvtr和lvtr1至lvtr3,并且可以提高半导体器件2100的集成度。

150.图24是根据示例实施例的包括半导体器件的存储设备的示意性框图。

151.参照图24,存储系统2200可以包括存储装置2210和/或存储控制器2220。存储系统2200可以支持多个通道ch1至chm,并且存储装置2210和存储控制器2220可以通过多个通道ch1至chm彼此连接。例如,存储系统2200可以被实现为诸如固态硬盘(ssd)之类的存储设备。

152.存储装置2210可以包括多个存储元件nvm11至nvmmn。存储元件nvm11至nvmmn中的每一者可以通过对应的通路连接到多个通道ch1至chm之一。例如,存储元件nvm11至nvm1n可以通过通路w11至w1n连接到第一通道ch1,并且存储元件nvm21至nvm2n可以通过通路w21至w2n连接到第二通道ch2。在示例实施例中,存储元件nvm11至nvmmn均可以被实现为可以根据来自存储控制器2220的单独的命令而操作的任何存储单元。例如,存储元件nvm11至nvmmn均可以被实现为芯片或裸片,但是示例实施例不限于此。

153.存储控制器2220可以通过多个通道ch1至chm将信号发送到存储装置2210并且从存储装置2210接收信号。例如,通过通道ch1至chm,存储控制器2220可以将命令cmda至cmdm、地址addra至addrm和数据dataa至datam发送到存储装置2210,或者可以从存储装置2210接收数据dataa至datam。

154.存储控制器2220可以在通过每个通路连接到相应通道的存储元件当中选择存储元件,并可以向选择的存储元件发送信号并从选择的存储元件接收信号。例如,存储控制器2220可以在连接到第一通道ch1的存储元件nvm11至nvm1n当中选择存储器件nvm11。存储控制器2220可以通过第一通道ch1将命令cmda、地址addra和数据dataa发送到选择的存储元件nvm11,或者可以从选择的存储元件nvm11接收数据dataa。

155.存储控制器2220可以通过不同的通道并行地将信号发送到不同的通道并从不同的通道接收信号。例如,存储控制器2220可以通过第二通道ch2将命令cmdb发送到存储装置2210,同时通过第一通道ch1将命令cmda发送到存储装置2210。例如,存储控制器2220可以通过第二通道ch2从存储装置2210接收数据datab,同时通过第一通道ch1从存储装置2210接收数据dataa。

156.存储控制器2220可以控制存储装置2210的总体操作。存储控制器2220可以将信号发送到通道ch1至chm,以控制连接到通道ch1至chm的存储元件nvm11至nvmmn之一。例如,存储控制器2220可以将命令cmda和地址addra发送到第一通道ch1,以控制存储元件nvm11至nvmmn中的所选择的一者。

157.存储元件nvm11至nvmmn均可以在存储控制器2220的控制下操作。例如,存储元件nvm11可以基于提供到第一通道ch1的命令cmda、地址addra和数据dataa对数据dataa进行编程。例如,存储元件nvm21可以基于提供到第二通道ch2的命令cmda和地址addrb来读取数据datab,并可以将所读取的数据datab发送到存储控制器2220。

158.在图24中,存储装置2210被示出为通过m个通道与存储控制器2220通信并包括与每个通道对应的n个存储元件。然而,通道的数目和连接到单个通道的存储元件的数目可以变化。

159.存储装置2210和存储控制器2220可以被实现为根据示例实施例的半导体器件。作为示例,在存储装置2210和存储控制器2220中,高电压nmos元件和低电压nmos元件可以一起形成在单个袋状p阱区中,并且低电压pmos元件可以形成在围绕袋状p阱区的n阱区中。因

此,可以提高存储装置2210和存储控制器2220的集成度,并且也可以改善其操作性能。

160.如上所述,高电压元件和低电压元件二者都可以形成于形成在外围电路区域中并接收作为体偏置电压的负电压的第一阱区中,并且低电压元件还可以形成在围绕第一阱区的第二阱区中。因此,可以提高形成在外围电路区域中的电路元件的集成度,以提高半导体器件的集成度,并且可以高效地设置电路元件之间的电气路径,以改善半导体器件的性能。

161.以上公开的一个或更多个元件可以包括一个或更多个处理电路,诸如包括逻辑电路的硬件、诸如执行软件的处理器的硬件/软件组合或者它们的组合,或者在该一个或更多个处理电路中实现。例如,处理电路更具体地可以包括但不限于中央处理单元(cpu)、算术逻辑单元(alu)、数字信号处理器、微型计算机、现场可编程门阵列(fpga)、片上系统(soc)、可编程逻辑单元、微处理器、专用集成电路(asic)等。

162.虽然以上已经示出并描述了示例实施例,但对于本领域技术人员将明显的是,在不脱离随附权利要求限定的本发明构思的范围的情况下,可以进行修改和变化。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。