1.本发明属于微电子技术领域,具体涉及一种横向同质异质结存储器器件及制备方法。

背景技术:

2.以石墨烯、过渡金属硫属化物(transition metal dichalcogenides,tmds)为代表的二维材料具有原子级的厚度,良好的理化性质,超大的比表面积等特点,可以作为导电沟道广泛应用在半导体电子器件中。在存储器件中,二维材料独特的原子级厚度可以有效减小器件尺寸,避免由于尺寸缩小产生的短沟道效应,且二维器件工作时的小电流使其具有小的工作功耗,因此成为新一代半导体存储器件。

3.传统二维材料垂直堆叠形成的异质结界面接触面积大,界面陷阱多,而二维材料形成的横向异质结具有更小的接触界面,从而减少了界面缺陷对器件的影响,提高了器件的电学性能。因此制备一个尺寸小,功耗低的存储器件成为存储器件研究的关键问题。

4.现有研究公开了一种二维材料异质结浮栅存储器,包括:栅层、多个浮栅层、阻挡层、沟道层、电极层。但是,该存储器的制备方法需要对二维材料进行多次堆叠、光刻、刻蚀等一系列工艺步骤,这些过程会对二维材料界面和质量造成不同程度的损伤,从而进一步影响存储器的电学性能。

技术实现要素:

5.为了解决现有技术中存在的上述问题,本发明提供了一种横向同质异质结存储器器件及制备方法。本发明要解决的技术问题通过以下技术方案实现:

6.本发明实施例提供了一种横向同质异质结存储器器件,包括:衬底栅层、第一介质层、第二介质层、二维半导体沟道层和欧姆电极,其中,

7.所述第一介质层和所述第二介质层均位于所述衬底栅层上,且所述第一介质层和所述第二介质层相接触;

8.所述二维半导体沟道层位于所述第一介质层和所述第二介质层上;

9.所述欧姆电极位于所述二维半导体沟道层的两端。

10.在本发明的一个实施例中,所述衬底栅层的材料包括重掺杂硅,所述重掺杂硅的掺杂浓度为1

×

10

17-1

×

10

19

cm-3

。

11.在本发明的一个实施例中,所述第一介质层的厚度和所述第二介质层的厚度均为10-100nm。

12.在本发明的一个实施例中,所述第一介质层和所述第二介质层中至少一种介质层的材料为铁电介质材料。

13.在本发明的一个实施例中,所述铁电介质材料包括铪锆氧、钛酸钡、α相三硒化二铟中的一种或多种。

14.在本发明的一个实施例中,所述二维半导体沟道层的材料包括若干层二维半导体

材料,所述若干层二维半导体材料的层数小于等于10层。

15.在本发明的一个实施例中,所述二维半导体沟道层的厚度为0.35-10nm。

16.在本发明的一个实施例中,所述欧姆电极的材料包括金属x、金属au中的一种或多种,所述金属x包括ti、cr、pt、pd中的任一种,且所述金属x的厚度为5-10nm,所述金属au的厚度为30-80nm。

17.本发明的另一实施例提供了一种横向同质异质结存储器器件的制备方法,包括步骤:

18.s1、在衬底栅层上制备第一介质层、第二介质层,使得所述第一介质层和所述第二介质层相接触;

19.s2、将所述二维半导体沟道层转移至所述第一介质层和所述第二介质层上;

20.s3、在所述二维半导体沟道层的两端制备欧姆电极。

21.在本发明的一个实施例中,步骤s1包括:

22.s11、在所述衬底栅层上生长第一介质材料;

23.s12、对所述第一介质材料进行光刻和图形化刻蚀,露出部分所述衬底栅层的表面,得到第一介质层;

24.s13、在露出的所述衬底栅层的表面和所述第一介质层上生长第二介质材料;

25.s14、对所述第一介质层上的所述第二介质材料进行图形化刻蚀,得到第二介质层。

26.与现有技术相比,本发明的有益效果:

27.本发明的横向同质异质结存储器器件通过第一介质层和第二介质层形成复合介质层,复合介质层对堆叠在其上方的二维半导体沟道层进行介质调控和静电栅调控,使得二维半导体沟道层的同质材料中形成横向异质结,形成的横向异质结截面处于第一介质层和第二介质层的交界处,且形成的横向异质结界面只有一条线,减少了界面处的缺陷,并且由于是采用同种材料形成的异质结,所以不存在不同材料间的晶格失配问题,提高了存储器电学性能。

附图说明

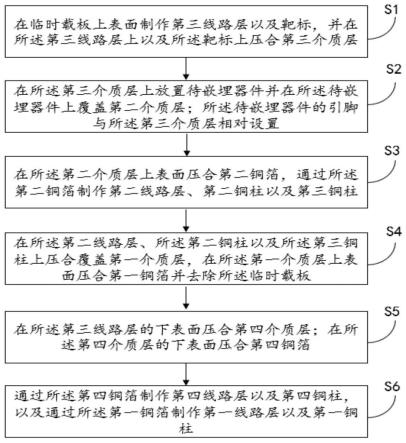

28.图1为本发明实施例提供的一种横向同质异质结存储器器件的结构示意图;

29.图2为本发明实施例提供的一种横向同质异质结存储器器件的制备方法的流程示意图;

30.图3a-图3g为本发明实施例提供的一种横向同质异质结存储器器件的制备方法的过程示意图。

具体实施方式

31.下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

32.实施例一

33.请参见图1,图1为本发明实施例提供的一种横向同质异质结存储器器件的结构示意图。

34.该横向同质异质结存储器器件包括:衬底栅层1、第一介质层2、第二介质层3、二维半导体沟道层4和欧姆电极5。其中,第一介质层2和第二介质层3均位于衬底栅层1上,且第一介质层2和第二介质层3相接触;二维半导体沟道层4位于第一介质层2和第二介质层3上;欧姆电极5位于二维半导体沟道层4的两端。

35.衬底栅层1作为衬底层,同时作为栅极,起到栅极调控的作用。衬底栅层1的材料包括重掺杂硅,重掺杂硅的掺杂浓度为1

×

10

17-1

×

10

19

cm-3

。

36.第一介质层2和第二介质层3共同形成复合介质层。第一介质层2和第二介质层3的厚度可以相等,也可以为纳米级别的不相等;优选的,第一介质层2和第二介质层3的厚度相等。第一介质层2的厚度和第二介质层3的厚度均为10-100nm。

37.第一介质层2和第二介质层3中,至少一种介质层的材料为铁电介质材料,即,第一介质层2和第二介质层3的材料可以都为铁电介质材料,也可以第一介质层2的材料为铁电介质材料,第二介质层3的材料不为铁电介质材料,也可以第一介质层2的材料不为铁电介质材料,第二介质层3的材料为铁电介质材料。具体的,铁电介质材料包括铪锆氧、钛酸钡、α相三硒化二铟(α-in2se3)中的一种或多种。

38.本发明通过制备复合介质层,避免了异质结材料接触形成的晶格失配问题,减小了界面的缺陷,从而提高了存储的电学性能。

39.二维半导体沟道层4位于复合介质层的上方,覆盖第一介质层2和第二介质层3相接触的位置。二维半导体沟道层4的材料包括若干层二维半导体材料,二维半导体材料包括二硫化钼、二硫化钨、二硒化钨等中的任一种;若干层二维半导体材料的层数小于等于10层,即,二维半导体沟道层4的材料为单层二维半导体材料或少层二维半导体材料,其中,少层是指层数小于等于10层。二维半导体沟道层4的厚度为0.35-10nm。

40.欧姆电极5的材料包括金属x、金属au中的一种或多种,金属x包括ti、cr、pt、pd中的任一种,且金属x的厚度为5-10nm,金属au的厚度为30-80nm。

41.本实施例的横向同质异质结存储器器件通过第一介质层和第二介质层形成复合介质层,复合介质层中至少一种介质层的材料为铁电介质材料,从而复合介质层对堆叠在其上方的二维半导体沟道层进行介质调控和静电栅调控,使得二维半导体沟道层的同质材料中形成横向异质结,形成的横向异质结截面处于第一介质层和第二介质层的交界处,且形成的横向异质结界面只有一条线,该条线与第一介质层和第二介质层的交界处对应,进而减少了界面处的缺陷,并且由于是采用同种材料形成的异质结,所以不存在不同材料间的晶格失配问题,提高了存储器电学性能。综上,本实施例采用同质横向异质结,可以避免晶格失配、界面缺陷等不足对存储器电学性能的影响,提高存储器的电学性能。

42.实施例二

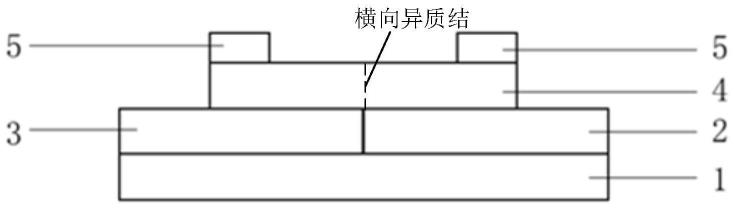

43.在实施例一的基础上,本实施例提供了一种横向同质异质结存储器器件的制备方法。请参见图2和图3a-图3g,图2为本发明实施例提供的一种横向同质异质结存储器器件的制备方法的流程示意图,图3a-图3g为本发明实施例提供的一种横向同质异质结存储器器件的制备方法的过程示意图。

44.该制备方法包括步骤:

45.s1、在衬底栅层1上制备第一介质层2、第二介质层3,使得第一介质层2和第二介质层3相接触。具体包括步骤:

46.s11、在衬底栅层1上生长第一介质材料,请参见图3a和图3b。

47.具体的,首先清洗衬底栅层1,然后,在衬底栅层1上生长第一介质材料。

48.s12、对第一介质材料进行光刻和图形化刻蚀,露出部分衬底栅层1的表面,得到第一介质层2,请参见图3c。

49.具体的,对第一介质材料进行光刻、图形化刻蚀,露出部分衬底栅层1的表面,用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干形成图形化的第一介质层2;

50.s13、在露出的衬底栅层1的表面和第一介质层2上生长第二介质材料,请参见图3d。

51.具体的,用原子层沉积法在露出的衬底栅层1的表面和第一介质层2上生长第二介质材料。

52.s14、对第一介质层2上的第二介质材料进行图形化刻蚀,得到第二介质层3,请参见图3e。

53.具体的,对第一介质层2上方的第二介质材料进行图形化刻蚀,用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干形成,第二介质层,从而使得第一介质层2和第二介质层3相接触,二者共同形成复合介质层。

54.s2、将二维半导体沟道层4转移至第一介质层2和第二介质层3上,请参见图3f。

55.具体的,将二维半导体沟道层4转移至第一介质层2和第二介质层3上,使得二维半导体沟道层4与第一介质层2和第二介质层3均接触。

56.s3、在二维半导体沟道层4的两端制备欧姆电极5,请参见图3g。

57.具体的,在二维半导体沟道层4上方进行金属蒸镀形成欧姆接触,并对金属层进行退火合金化,形成欧姆电极5,完成器件制备。

58.本实施例的制备方法工艺步骤简单,减少了对二维材料的处理,为后续的器件制备提供了便利。

59.实施例三

60.在实施例二的基础上,本实施例以制备第一介质层2的材料为二氧化硅,第二介质层3的材料为铪锆氧,复合介质层厚度为10nm、二维材料半导体层4的材料为单层二硫化钼的横向同质异质结存储器器件为例进行说明。

61.s1、在衬底栅层1上制备第一介质层2、第二介质层3,使得第一介质层2和第二介质层3相接触。

62.首先清洗衬底栅层1,请参见图3a。具体的,将衬底栅层1用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干。

63.然后,在衬底栅层1上制备复合介质层。具体的,在衬底栅层1上用原子沉积法生长第一介质材料二氧化硅10nm,请参见图3b;对第一介质材料二氧化硅层进行光刻、图形化刻蚀10nm,用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干形成图形化的二氧化硅介质层,得到第二介质层2,请参见图3c;再用原子层沉积法在器件表面生长第二介质层材料铪锆氧10nm,请参见图3d;对二氧化硅上方的第二介质层材料铪锆氧层进行图形化刻蚀10nm,用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干形成第二介质层3,得到复合介质层,请参见图3e。

64.s2、将二维半导体沟道层4转移至第一介质层2和第二介质层3上,请参见图3f。

65.具体的,将机械剥离的单层二硫化钼纳米片用干法转移法转移到复合介质层上,使得单层二硫化钼纳米片与第一介质层2和第二介质层3均接触。

66.s3、在二维半导体沟道层4的两端制备欧姆电极5,请参见图3g。

67.具体的,在单层二硫化钼上进行光刻、金属蒸镀,并进行退火合金化形成欧姆接触电极。所用金属为ti/au,且金属ti的生长厚度为5nm,金属au的生长厚度为30nm,完成单层二硫化钼的横向同质异质结存储器件制备。

68.实施例四

69.在实施例二的基础上,本实施例以制备第一介质层2的材料为二氧化铪,第二介质层3的材料为铪锆氧,复合介质层厚度为50nm、二维材料半导体层4为少层二硒化钨的横向同质异质结存储器器件为例进行说明。

70.s1、在衬底栅层1上制备第一介质层2、第二介质层3,使得第一介质层2和第二介质层3相接触。

71.首先清洗衬底栅层1,请参见图3a。具体的,将衬底栅层1用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干。

72.然后,在衬底栅层1上制备复合介质层。具体的,在衬底栅层1上用原子沉积法生长第一介质材料二氧化铪50nm,请参见图3b;对第一介质材料二氧化铪进行光刻、图形化刻蚀50nm,用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干形成图形化的二氧化铪介质层,得到第二介质层2,请参见图3c;再用原子层沉积法在器件表面生长第二介质层材料铪锆氧50nm,请参见图3d;对二氧化硅上方的第二介质层材料铪锆氧层进行图形化刻蚀50nm,用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干形成第二介质层3,得到复合介质层,请参见图3e。

73.s2、将二维半导体沟道层4转移至第一介质层2和第二介质层3上,请参见图3f。

74.具体的,将机械剥离的少层二硒化钨纳米片用干法转移法转移到复合介质层上,使得少层二硒化钨纳米片与第一介质层2和第二介质层3均接触。

75.s3、在二维半导体沟道层4的两端制备欧姆电极5,请参见图3g。

76.具体的,在少层二硒化钨上进行光刻、金属蒸镀,并进行退火合金化形成欧姆接触电极。所用金属为cr/au,且金属cr的生长厚度为10nm,金属au的生长厚度为60nm,完成少层二硒化钨的横向同质异质结存储器件制备。

77.实施例五

78.在实施例二的基础上,本实施例以制备第一介质层2的材料为二氧化铪,第二介质层3的材料为铪锆氧,复合介质层厚度为100nm、二维材料半导体层4为单层二硫化钼薄膜的横向同质异质结存储器器件为例进行说明。

79.s1、在衬底栅层1上制备第一介质层2、第二介质层3,使得第一介质层2和第二介质层3相接触。

80.首先清洗衬底栅层1,请参见图3a。具体的,将衬底栅层1用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干。

81.然后,在衬底栅层1上制备复合介质层。具体的,在衬底栅层1上用原子沉积法生长第一介质材料二氧化铪100nm,请参见图3b;对第一介质材料二氧化铪进行光刻、图形化刻蚀100nm,用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干形成图形化的二氧化

铪介质层,得到第二介质层2,请参见图3c;再用原子层沉积法在器件表面生长第二介质层材料铪锆氧100nm,请参见图3d;对二氧化硅上方的第二介质层材料铪锆氧层进行图形化刻蚀100nm,用丙酮、酒精、去离子水分别超声清洗5分钟,并用氮气吹干形成第二介质层3,得到复合介质层,请参见图3e。

82.s2、将二维半导体沟道层4转移至第一介质层2和第二介质层3上,请参见图3f。

83.具体的,将机械剥离的单层二硫化钼薄膜用干法转移法转移到复合介质层上,使得单层二硫化钼薄膜与第一介质层2和第二介质层3均接触。

84.s3、在二维半导体沟道层4的两端制备欧姆电极5,请参见图3g。

85.具体的,在单层二硫化钼薄膜上进行光刻、金属蒸镀,并进行退火合金化形成欧姆接触电极。所用金属为pd/au,且金属pd的生长厚度为10nm,金属au的生长厚度为80nm,完成单层二硫化钼的横向同质异质结存储器件制备。

86.以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。