adas控制电路的控制方法以及其控制装置

技术领域

1.本技术涉及电路领域,具体而言,涉及一种adas控制电路的控制方法、其控制装置、计算机可读存储介质、处理器以及adas控制系统。

背景技术:

2.adas(advanced driving assistance system,高级驾驶辅助系统)域控制器系统中,主控板完成多个感知摄像头的图像采集处理,为了满足算法算力需求,通常处理视频信号由主控板上soc(system on chip,系统级芯片)芯片完成。

3.但是,由于soc芯片自身多核结构及其复杂的电源系统设计,首次上电启动会需要比较长的时间,这样会导致域控制器上电后,soc启动到正常工作会存在一定的延时,不能及时处理摄像头的图像。

4.在背景技术部分中公开的以上信息只是用来加强对本文所描述技术的背景技术的理解,因此,背景技术中可能包含某些信息,这些信息对于本领域技术人员来说并未形成在本国已知的现有技术。

技术实现要素:

5.本技术的主要目的在于提供一种adas控制电路的控制方法、其控制装置、计算机可读存储介质、处理器以及adas控制系统,以解决现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题。

6.根据本发明实施例的一个方面,提供了一种adas控制电路的控制方法,所述adas控制电路的控制方法用于第一控制器,所述adas控制电路包括解串器、加串器以及第二控制器,其中,所述第二控制器与所述解串器连接,所述解串器与所述加串器连接,所述第二控制器用于控制所述解串器进行解串处理,所述方法包括:在满足第一预定条件的情况下,控制所述解串器进行所述解串处理,且控制所述加串器进行加串处理,所述第一预定条件为:所述第一控制器启动成功且所述第二控制器未启动成功;在满足第二预定条件的情况下,控制所述加串器进行所述加串处理,且对所述第二控制器以及所述解串器进行预定处理,使得所述第二控制器控制所述解串器进行所述解串处理,所述第二预定条件为:所述第二控制器以及所述第一控制器均启动成功,所述预定处理包括配置处理。

7.可选地,在满足第二预定条件的情况下,控制所述加串器进行所述加串处理,且对所述第二控制器以及所述解串器进行预定处理,使得所述第二控制器控制所述解串器进行所述解串处理,包括:在满足所述第二预定条件的情况下,通过控制总线对所述第二控制器与所述解串器进行所述配置处理,使得在所述解串器接收到原始图像信号的情况下,所述第二控制器控制所述解串器对所述原始图像信号进行所述解串处理,得到预备图像信号,其中,所述原始图像信号为预定设备发出的原始的图像信号;在所述加串器接收到所述预备图像信号的情况下,控制所述加串器对所述预备图像信号进行所述加串处理,得到目标图像信号。

8.可选地,在满足第一预定条件的情况下,控制所述解串器进行所述解串处理,且控制所述加串器进行加串处理,包括:在满足所述第一预定条件的情况下,控制所述解串器对所述原始图像信号进行所述解串处理,得到所述预备图像信号;在所述加串器接收到所述预备图像信号的情况下,控制所述加串器对所述预备图像信号进行所述加串处理,得到所述目标图像信号。

9.可选地,所述方法还包括:控制所述加串器发出所述目标图像信号,使得关联设备接收到所述目标图像信号,所述关联设备与所述加串器连接。

10.可选地,所述控制总线包括iic(inter integrated circuit,集成电路总线)。

11.可选地,所述第二控制器包括soc,第一控制器包括mcu(micro control unit,微控制单元)。

12.根据本发明实施例的另一方面,还提供了一种adas控制电路的控制装置,所述adas控制电路的控制装置用于第一控制器,所述adas控制电路包括解串器、加串器以及第二控制器,其中,所述第二控制器与所述解串器连接,所述解串器与所述加串器连接,所述第二控制器用于控制所述解串器进行解串处理,所述装置包括第一控制单元以及第二控制单元,其中,所述第一控制单元用于在满足第一预定条件的情况下,控制所述解串器进行所述解串处理,且控制所述加串器进行加串处理,所述第一预定条件为:所述第一控制器启动成功且所述第二控制器未启动成功;所述第二控制单元用于在满足第二预定条件的情况下,控制所述加串器进行所述加串处理,且通过对所述第二控制器以及所述解串器进行预定处理,使得所述第二控制器可以控制所述解串器进行所述解串处理,所述第二预定条件为:所述第二控制器以及所述第一控制器均启动成功,所述预定处理包括配置处理。

13.根据本发明实施例的又一方面,还提供了一种计算机可读存储介质,所述计算机可读存储介质包括存储的程序,其中,所述程序用于执行任一种所述的方法。

14.根据本发明实施例的再一方面,还提供了一种处理器,所述处理器用于运行程序,其中,所述程序运行时执行任一种所述的方法。

15.根据本发明实施例的又一方面,还提供了一种adas控制系统,所述adas控制系统包括adas控制电路以及第一控制器,其中,所述adas控制电路包括解串器、加串器以及第二控制器,其中,所述第二控制器与所述解串器连接,所述解串器与所述加串器连接,所述第二控制器用于控制所述解串器进行解串处理;所述第一控制器分别与所述解串器以及所述加串器连接,所述第一控制器用于执行任一种所述的方法。

16.在本发明实施例中,所述adas控制电路的控制方法中,首先,在所述第一控制器启动成功且所述第二控制器未启动成功的情况下,控制所述解串器进行所述解串处理,且控制所述加串器进行加串处理;然后,在所述第一控制器以及所述第二控制器均启动成功情况下,控制所述加串器进行所述加串处理,且对所述第二控制器以及所述解串器进行配置处理,使得所述第二控制器控制所述解串器进行所述解串处理。相比现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题,本技术的所述adas控制电路的控制方法,在所述第一控制器启动成功且所述第二控制器未启动成功的情况下,通过所述第一控制器控制所述解串器进行所述解串处理,且所述第一控制器控制所述加串器进行所述加串处理,使得在所述第二控制器未启动成功的情况下,所述第一控制器可以同时控制所述解串器以及所述加串器进行相应处理,再在所述第一控制器以及所述第二控制器均启动成功的

情况下,所述第一控制器一方面控制所述加串器进行所述加串处理,另一方面,所述第一控制器对所述第二控制器以及所述解串器进行所述配置处理,使得所述第二控制器可以控制所述解串器,保证了可以通过两个控制器分别控制所述解串器以及所述加串器,解决了现有技术中由于soc上电后启动较慢导致不能及时处理图像的问题,使得所述adas控制电路可以计时且效率较高的处理信息,保证了所述adas控制电路的效率较高。

附图说明

17.构成本技术的一部分的说明书附图用来提供对本技术的进一步理解,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

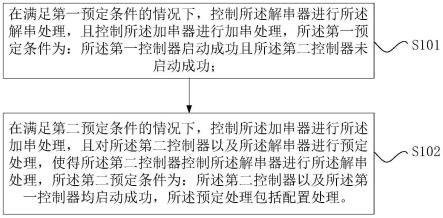

18.图1示出了根据本技术的实施例的adas控制电路的控制方法流程示意图;

19.图2示出了根据本技术的实施例的adas控制电路的控制装置的示意图;

20.图3示出了根据本技术的实施例的adas控制系统的结构示意图。

21.其中,上述附图包括以下附图标记:

22.30、第一控制器;40、解串器;50、加串器;60、第二控制器;70、预定设备;80、关联设备。

具体实施方式

23.需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本技术。

24.为了使本技术领域的人员更好地理解本技术方案,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分的实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本技术保护的范围。

25.需要说明的是,本技术的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本技术的实施例。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

26.应该理解的是,当元件(诸如层、膜、区域、或衬底)描述为在另一元件“上”时,该元件可直接在该另一元件上,或者也可存在中间元件。而且,在说明书以及权利要求书中,当描述有元件“连接”至另一元件时,该元件可“直接连接”至该另一元件,或者通过第三元件“连接”至该另一元件。

27.正如背景技术中所说的,现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题,为了解决上述问题,本技术的一种典型的实施方式中,提供了一种adas控制电路的控制方法、其控制装置、计算机可读存储介质、处理器以及adas控制系统。

28.根据本技术的实施例,提供了一种adas控制电路的控制方法,上述adas控制电路的控制方法用于第一控制器,上述adas控制电路包括解串器、加串器以及第二控制器,其

中,上述第二控制器与上述解串器连接,上述解串器与上述加串器连接,上述第二控制器用于控制上述解串器进行解串处理。

29.图1是根据本技术实施例的adas控制电路的控制方法的流程图。如图1所示,该方法包括以下步骤:

30.步骤s101,在满足第一预定条件的情况下,控制上述解串器进行上述解串处理,且控制上述加串器进行加串处理,上述第一预定条件为:上述第一控制器启动成功且上述第二控制器未启动成功;

31.步骤s102,在满足第二预定条件的情况下,控制上述加串器进行上述加串处理,且对上述第二控制器以及上述解串器进行预定处理,使得上述第二控制器控制上述解串器进行上述解串处理,上述第二预定条件为:上述第二控制器以及上述第一控制器均启动成功,上述预定处理包括配置处理。

32.上述adas控制电路的控制方法中,首先,在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,控制上述解串器进行上述解串处理,且控制上述加串器进行加串处理;然后,在上述第一控制器以及上述第二控制器均启动成功情况下,控制上述加串器进行上述加串处理,且对上述第二控制器以及上述解串器进行配置处理,使得上述第二控制器控制上述解串器进行上述解串处理。相比现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题,本技术的上述adas控制电路的控制方法,在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,通过上述第一控制器控制上述解串器进行上述解串处理,且上述第一控制器控制上述加串器进行上述加串处理,使得在上述第二控制器未启动成功的情况下,上述第一控制器可以同时控制上述解串器以及上述加串器进行相应处理,再在上述第一控制器以及上述第二控制器均启动成功的情况下,上述第一控制器一方面控制上述加串器进行上述加串处理,另一方面,上述第一控制器对上述第二控制器以及上述解串器进行上述配置处理,使得上述第二控制器可以控制上述解串器,保证了可以通过两个控制器分别控制上述解串器以及上述加串器,解决了现有技术中由于soc上电后启动较慢导致不能及时处理图像的问题,使得上述adas控制电路可以计时且效率较高的处理信息,保证了上述adas控制电路的效率较高。

33.上述adas控制电路的控制过程,在不增加额外成本的基础上,通过电路逻辑控制上的修改,即在满足上述第一预定条件的情况下,通过上述第一控制器同时控制上述解串器以及上述加串器,在满足上述第二预定条件的额情况下,上述第一控制器控制上述加串器,另外,上述第一控制器还对上述第二控制器以及上述解串器进行配置,实现上述第二控制器控制上述解串器,即根据上述第二控制器是否上电启动成功,设定两种控制方式,实现了adas域控制器的快速图像输出需求。

34.为了进一步保证上述adas控制电路的效率较高,根据本技术的一种具体实施例,在满足第二预定条件的情况下,控制上述加串器进行上述加串处理,且对上述第二控制器以及上述解串器进行预定处理,使得上述第二控制器控制上述解串器进行上述解串处理,包括:在满足上述第二预定条件的情况下,通过控制总线对上述第二控制器与上述解串器进行上述配置处理,使得在上述解串器接收到原始图像信号的情况下,上述第二控制器控制上述解串器对上述原始图像信号进行上述解串处理,得到预备图像信号,其中,上述原始图像信号为预定设备发出的原始的图像信号;在上述加串器接收到上述预备图像信号的情

况下,控制上述加串器对上述预备图像信号进行上述加串处理,得到目标图像信号。在上述第二控制器以及上述第一控制器均启动成功的情况下,上述第一控制器通过上述控制总线对上述第二控制器与上述解串器进行上述配置处理,使得上述解串器在接收到上述原始图像信号的情况下,上述第二控制器控制上述解串器对上述原始图像信号进行上述解串处理,保证了可以较快的得到上述预备图像信号,再通过上述第一控制器控制上述加串器对上述预备图像信号进行上述加串处理,保证了可以较快的得到上述目标图像信号,使得上述第一控制器以及上述第二控制器可以分别控制上述加串器以及上述解串器,进一步保证了上述adas控制电路的效率较高。

35.具体地,上述解串器的上述解串处理主要用于上述原始图像信号的接口转换,上述加串器的上述加串处理主要用于上述目标图像信号输出的接口转换。

36.为了进一步保证上述adas控制电路的效率较高,根据本技术的另一种具体实施例,在满足第一预定条件的情况下,控制上述解串器进行上述解串处理,且控制上述加串器进行加串处理,包括:在满足上述第一预定条件的情况下,控制上述解串器对上述原始图像信号进行上述解串处理,得到上述预备图像信号;在上述加串器接收到上述预备图像信号的情况下,控制上述加串器对上述预备图像信号进行上述加串处理,得到上述目标图像信号。在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,上述第一控制器通过控制上述解串器对上述原始图像信号进行上述解串处理,保证了可以较快的得到上述预备图像信号,上述第一控制器再通过控制上述加串器对上述预备图像信号进行上述加串处理,保证了可以较快的得到上述目标图像信号,即在上述第二控制器未启动成功的情况下,上述第一控制器可以同时控制上述解串器以及上述加串器,进一步保证了上述adas控制电路的效率较高。

37.根据本技术的又一种具体实施例,上述方法还包括:控制上述加串器发出上述目标图像信号,使得关联设备接收到上述目标图像信号,上述关联设备与上述加串器连接。通过上述第一控制器控制上述加串器发出上述目标图像信号,保证了上述关联设备可以较快的接收到上述目标图像信号,进一步保证了上述adas控制电路的效率较高。

38.具体地,上述关联设备用于表征需要上述目标图像信号的设备,上述关联设备用于对上述目标图像信号进行相应的处理,更加方面后续的使用。

39.根据本技术的一种具体实施例,上述控制总线包括iic。上述控制总线包括iic,即上述第一控制器通过iic配置上述第二控制器以及上述解串器。

40.根据本技术的另一种具体实施例,上述解串器与上述加串器通过第一通信方式进行连接,上述第一通信方式包括mipi(mobile industry processor interface,移动产业处理器接口)。

41.具体地,上述解串器以及上述加串器通过mipi传输上述预备图像信号。

42.根据本技术的又一种具体实施例,上述解串器与上述第二控制器通过第二通信方式进行连接,上述第二通信方式包括mipi以及gpio(general purpose input/output)中至少之一。

43.具体地,上述解串器还通过mipi传输上述预备图像信号至上述第二控制器,另外,上述解串器与上述第二控制器还通过控制总线iic进行连接。

44.一种具体的实施例中,上述第一控制器是通过iic配置上述第二控制器与上述解

串器。

45.具体地,当域控制器刚上电时,上述第一控制器首先启动,上述解串器以及上述加串器上电,上述第一控制器通过iic通讯实现对上述加串器以及上述解串器的配置,上述解串器将上述预定设备发出的上述原始图像信号转换为mipi信号,即转换为上述预备图像信号传输给上述加串器,上述加串器实现对上述目标图像信号的快速输出,当上述第二控制器完成上电启动后,上述第一控制器将上述解串器与上述第二控制器相连的功能gpio配置为iic引脚,从而完成对上述解串器的iic控制的切换,后续由上述第二控制器完成对上述原始图像信号的采集处理。

46.根据本技术的一种具体实施例,上述第二控制器包括soc,第一控制器包括mcu。

47.具体地,上述第一控制器与上述加串器通过iic以及gpio连接。

48.现有技术中,上述第二控制器soc由于其自身多核结构及其复杂的电源系统设计,导致在上电初期,不能很快的启动成功,即不能很快的正常工作,会存在一定的延时,而上述第一控制器mcu启动较快,因此,本技术的上述adas控制电路的控制过程中,在上电启动初期,通过上述第一控制器同时控制上述解串器以及上述加串器,并且在上述第二控制器上电且启动成功后,上述第一控制器通过对上述解串器以及上述第二控制器进行上述配置处理,使得上述第二控制器控制上述解串器,上述第一控制器控制上述加串器,保证了上述adas控制电路无论在启动初期还是之后,都可以较快的处理上述原始图像信号,保证了可以较快的得到上述目标图像信号,进一步保证了上述adas控制电路的效率较高。

49.一种具体的实施例中,上述adas控制电路的控制过程中,通过修改上述控制电路的上电逻辑控制,由启动更快的mcu先控制处理视频信号的上述加串器以及上述解串器,保证了在soc上电过程中即可实现图像的快速输出,并且等soc启动完成后,上述解串器的控制从mcu切换为soc,完成后续的视频信号融合算法处理,保证了通过修改上述adas控制电路的控制逻辑,可以效率较高的完成对原始信号的处理。

50.本技术实施例还提供了一种adas控制电路的控制装置,上述adas控制电路的控制装置用于第一控制器,上述adas控制电路包括解串器、加串器以及第二控制器,其中,上述第二控制器与上述解串器连接,上述解串器与上述加串器连接,上述第二控制器用于控制上述解串器进行解串处理,需要说明的是,本技术实施例的adas控制电路的控制装置可以用于执行本技术实施例所提供的用于adas控制电路的控制方法。以下对本技术实施例提供的adas控制电路的控制装置进行介绍。

51.图2是根据本技术实施例的adas控制电路的控制装置的示意图。如图2所示,该装置包括第一控制单元10以及第二控制单元20,其中,上述第一控制单元10用于在满足第一预定条件的情况下,控制上述解串器进行上述解串处理,且控制上述加串器进行加串处理,上述第一预定条件为:上述第一控制器启动成功且上述第二控制器未启动成功;上述第二控制单元20用于在满足第二预定条件的情况下,控制上述加串器进行上述加串处理,且通过对上述第二控制器以及上述解串器进行预定处理,使得上述第二控制器可以控制上述解串器进行上述解串处理,上述第二预定条件为:上述第二控制器以及上述第一控制器均启动成功,上述预定处理包括配置处理。

52.上述adas控制电路的控制装置中,通过上述第一控制单元在满足第一预定条件的情况下,控制上述解串器进行上述解串处理,且控制上述加串器进行加串处理,上述第一预

定条件为:上述第一控制器启动成功且上述第二控制器未启动成功;通过上述第二控制单元在满足第二预定条件的情况下,控制上述加串器进行上述加串处理,且对上述第二控制器以及上述解串器进行预定处理,使得上述第二控制器控制上述解串器进行上述解串处理,上述第二预定条件为:上述第二控制器以及上述第一控制器均启动成功,上述预定处理包括配置处理。相比现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题,本技术的上述adas控制电路的控制装置,在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,通过上述第一控制器控制上述解串器进行上述解串处理,且上述第一控制器控制上述加串器进行上述加串处理,使得在上述第二控制器未启动成功的情况下,上述第一控制器可以同时控制上述解串器以及上述加串器进行相应处理,再在上述第一控制器以及上述第二控制器均启动成功的情况下,上述第一控制器一方面控制上述加串器进行上述加串处理,另一方面,上述第一控制器对上述第二控制器以及上述解串器进行上述配置处理,使得上述第二控制器可以控制上述解串器,保证了可以通过两个控制器分别控制上述解串器以及上述加串器,解决了现有技术中由于soc上电后启动较慢导致不能及时处理图像的问题,使得上述adas控制电路可以计时且效率较高的处理信息,保证了上述adas控制电路的效率较高。

53.上述adas控制电路的控制过程,在不增加额外成本的基础上,通过电路逻辑控制上的修改,即在满足上述第一预定条件的情况下,通过上述第一控制器同时控制上述解串器以及上述加串器,在满足上述第二预定条件的额情况下,上述第一控制器控制上述加串器,另外,上述第一控制器还对上述第二控制器以及上述解串器进行配置,实现上述第二控制器控制上述解串器,即根据上述第二控制器是否上电启动成功,设定两种控制方式,实现了adas域控制器的快速图像输出需求。

54.为了进一步保证上述adas控制电路的效率较高,根据本技术的一种具体实施例,上述第二控制单元包括第一控制模块以及第二控制模块,其中,上述第一控制模块用于在满足上述第二预定条件的情况下,通过控制总线对上述第二控制器与上述解串器进行上述配置处理,使得在上述解串器接收到原始图像信号的情况下,上述第二控制器控制上述解串器对上述原始图像信号进行上述解串处理,得到预备图像信号,其中,上述原始图像信号为预定设备发出的原始的图像信号;上述第二控制模块用于在上述加串器接收到上述预备图像信号的情况下,控制上述加串器对上述预备图像信号进行上述加串处理,得到目标图像信号。在上述第二控制器以及上述第一控制器均启动成功的情况下,上述第一控制器通过上述控制总线对上述第二控制器与上述解串器进行上述配置处理,使得上述解串器在接收到上述原始图像信号的情况下,上述第二控制器控制上述解串器对上述原始图像信号进行上述解串处理,保证了可以较快的得到上述预备图像信号,再通过上述第一控制器控制上述加串器对上述预备图像信号进行上述加串处理,保证了可以较快的得到上述目标图像信号,使得上述第一控制器以及上述第二控制器可以分别控制上述加串器以及上述解串器,进一步保证了上述adas控制电路的效率较高。

55.具体地,上述解串器的上述解串处理主要用于上述原始图像信号的接口转换,上述加串器的上述加串处理主要用于上述目标图像信号输出的接口转换。

56.为了进一步保证上述adas控制电路的效率较高,根据本技术的另一种具体实施例,上述第一控制单元包括第三控制模块以及第四控制模块,其中,上述第三控制模块用于

在满足上述第一预定条件的情况下,控制上述解串器对上述原始图像信号进行上述解串处理,得到上述预备图像信号;上述第四控制模块用于在上述加串器接收到上述预备图像信号的情况下,控制上述加串器对上述预备图像信号进行上述加串处理,得到上述目标图像信号。在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,上述第一控制器通过控制上述解串器对上述原始图像信号进行上述解串处理,保证了可以较快的得到上述预备图像信号,上述第一控制器再通过控制上述加串器对上述预备图像信号进行上述加串处理,保证了可以较快的得到上述目标图像信号,即在上述第二控制器未启动成功的情况下,上述第一控制器可以同时控制上述解串器以及上述加串器,进一步保证了上述adas控制电路的效率较高。

57.根据本技术的又一种具体实施例,上述装置还包括第三控制单元,上述第三控制单元用于控制上述加串器发出上述目标图像信号,使得关联设备接收到上述目标图像信号,上述关联设备与上述加串器连接。通过上述第一控制器控制上述加串器发出上述目标图像信号,保证了上述关联设备可以较快的接收到上述目标图像信号,进一步保证了上述adas控制电路的效率较高。

58.具体地,上述关联设备用于表征需要上述目标图像信号的设备,上述关联设备用于对上述目标图像信号进行相应的处理,更加方面后续的使用。

59.根据本技术的一种具体实施例,上述控制总线包括iic。述控制总线包括iic,即上述第一控制器通过iic配置上述第二控制器以及上述解串器。

60.根据本技术的另一种具体实施例,上述解串器与上述加串器通过第一通信方式进行连接,上述第一通信方式包括mipi。

61.具体地,上述解串器以及上述加串器通过mipi传输上述预备图像信号。

62.根据本技术的又一种具体实施例,上述解串器与上述第二控制器通过第二通信方式进行连接,上述第二通信方式包括mipi以及gpio中至少之一。

63.具体地,上述解串器还通过mipi传输上述预备图像信号至上述第二控制器,另外,上述解串器与上述第二控制器还通过控制总线iic进行连接。

64.一种具体的实施例中,上述第一控制器是通过iic配置上述第二控制器与上述解串器。

65.具体地,当域控制器刚上电时,上述第一控制器首先启动,上述解串器以及上述加串器上电,上述第一控制器通过iic通讯实现对上述加串器以及上述解串器的配置,上述解串器将上述预定设备发出的上述原始图像信号转换为mipi信号,即转换为上述预备图像信号传输给上述加串器,上述加串器实现对上述目标图像信号的快速输出,当上述第二控制器完成上电启动后,上述第一控制器将上述解串器与上述第二控制器相连的功能gpio配置为iic引脚,从而完成对上述解串器的iic控制的切换,后续由上述第二控制器完成对上述原始图像信号的采集处理。

66.根据本技术的一种具体实施例,上述第二控制器包括soc,第一控制器包括mcu。

67.具体地,上述第一控制器与上述加串器通过iic以及gpio连接。

68.现有技术中,上述第二控制器soc由于其自身多核结构及其复杂的电源系统设计,导致在上电初期,不能很快的启动成功,即不能很快的正常工作,会存在一定的延时,而上述第一控制器mcu启动较快,因此,本技术的上述adas控制电路的控制过程中,在上电启动

初期,通过上述第一控制器同时控制上述解串器以及上述加串器,并且在上述第二控制器上电且启动成功后,上述第一控制器通过对上述解串器以及上述第二控制器进行上述配置处理,使得上述第二控制器控制上述解串器,上述第一控制器控制上述加串器,保证了上述adas控制电路无论在启动初期还是之后,都可以较快的处理上述原始图像信号,保证了可以较快的得到上述目标图像信号,进一步保证了上述adas控制电路的效率较高。

69.一种具体的实施例中,上述adas控制电路的控制过程中,通过修改上述控制电路的上电逻辑控制,由启动更快的mcu先控制处理视频信号的上述加串器以及上述解串器,保证了在soc上电过程中即可实现图像的快速输出,并且等soc启动完成后,上述解串器的控制从mcu切换为soc,完成后续的视频信号融合算法处理,保证了通过修改上述adas控制电路的控制逻辑,可以效率较高的完成对原始信号的处理。

70.上述adas控制电路的控制装置包括处理器和存储器,上述第一控制单元以及上述第二控制单元等均作为程序单元存储在存储器中,由处理器执行存储在存储器中的上述程序单元来实现相应的功能。

71.处理器中包含内核,由内核去存储器中调取相应的程序单元。内核可以设置一个或以上,通过调整内核参数来解决现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题。

72.存储器可能包括计算机可读介质中的非永久性存储器,随机存取存储器(ram)和/或非易失性内存等形式,如只读存储器(rom)或闪存(flash ram),存储器包括至少一个存储芯片。

73.本发明实施例提供了一种计算机可读存储介质,其上存储有程序,该程序被处理器执行时实现上述adas控制电路的控制方法。

74.本发明实施例提供了一种处理器,上述处理器用于运行程序,其中,上述程序运行时执行上述adas控制电路的控制方法。

75.本发明实施例提供了一种设备,设备包括处理器、存储器及存储在存储器上并可在处理器上运行的程序,处理器执行程序时实现至少以下步骤:

76.步骤s101,在满足第一预定条件的情况下,控制上述解串器进行上述解串处理,且控制上述加串器进行加串处理,上述第一预定条件为:上述第一控制器启动成功且上述第二控制器未启动成功;

77.步骤s102,在满足第二预定条件的情况下,控制上述加串器进行上述加串处理,且对上述第二控制器以及上述解串器进行预定处理,使得上述第二控制器控制上述解串器进行上述解串处理,上述第二预定条件为:上述第二控制器以及上述第一控制器均启动成功,上述预定处理包括配置处理。

78.本文中的设备可以是服务器、pc、pad、手机等。

79.本技术还提供了一种计算机程序产品,当在数据处理设备上执行时,适于执行初始化有至少如下方法步骤的程序:

80.步骤s101,在满足第一预定条件的情况下,控制上述解串器进行上述解串处理,且控制上述加串器进行加串处理,上述第一预定条件为:上述第一控制器启动成功且上述第二控制器未启动成功;

81.步骤s102,在满足第二预定条件的情况下,控制上述加串器进行上述加串处理,且

对上述第二控制器以及上述解串器进行预定处理,使得上述第二控制器控制上述解串器进行上述解串处理,上述第二预定条件为:上述第二控制器以及上述第一控制器均启动成功,上述预定处理包括配置处理。

82.根据本技术的另一种典型的实施例,还提供了一种adas控制系统,如图3所示,上述adas控制系统包括adas控制电路以及第一控制器30,其中,上述adas控制电路包括解串器40、加串器50以及第二控制器60,其中,上述第二控制器60与上述解串器40连接,上述解串器40与上述加串器50连接,上述第二控制器60用于控制上述解串器40进行解串处理;上述第一控制器30分别与上述解串器40以及上述加串器50连接,上述第一控制器30用于执行任一种上述的方法。

83.上述的adas控制系统,包括adas控制电路以及第一控制器,其中,上述adas控制电路包括解串器、加串器以及第二控制器,其中,上述第二控制器与上述解串器连接,上述解串器与上述加串器连接,上述第二控制器用于控制上述解串器进行解串处理;上述第一控制器分别与上述解串器以及上述加串器连接,上述第一控制器用于执行任一种上述的方法。相比现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题,本技术的上述adas控制系统,在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,通过上述第一控制器控制上述解串器进行上述解串处理,且上述第一控制器控制上述加串器进行上述加串处理,使得在上述第二控制器未启动成功的情况下,上述第一控制器可以同时控制上述解串器以及上述加串器进行相应处理,再在上述第一控制器以及上述第二控制器均启动成功的情况下,上述第一控制器一方面控制上述加串器进行上述加串处理,另一方面,上述第一控制器对上述第二控制器以及上述解串器进行上述配置处理,使得上述第二控制器可以控制上述解串器,保证了可以通过两个控制器分别控制上述解串器以及上述加串器,解决了现有技术中由于soc上电后启动较慢导致不能及时处理图像的问题,使得上述adas控制电路可以计时且效率较高的处理信息,保证了上述adas控制电路的效率较高。

84.具体地,如图3所示,上述解串器40用于连接预定设备70,上述加串器50用于连接关联设备80。

85.一种具体的实施例中,上述预定设备包括相机等拍摄的设备。

86.在本发明的上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

87.在本技术所提供的几个实施例中,应该理解到,所揭露的技术内容,可通过其它的方式实现。其中,以上所描述的装置实施例仅仅是示意性的,例如上述单元的划分,可以为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,单元或模块的间接耦合或通信连接,可以是电性或其它的形式。

88.上述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

89.另外,在本发明各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单

元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

90.上述集成的单元如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可为个人计算机、服务器或者网络设备等)执行本发明各个实施例上述方法的全部或部分步骤。而前述的存储介质包括:u盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、移动硬盘、磁碟或者光盘等各种可以存储程序代码的介质。

91.从以上的描述中,可以看出,本技术上述的实施例实现了如下技术效果:

92.1)、本技术的上述adas控制电路的控制方法中,首先,在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,控制上述解串器进行上述解串处理,且控制上述加串器进行加串处理;然后,在上述第一控制器以及上述第二控制器均启动成功情况下,控制上述加串器进行上述加串处理,且对上述第二控制器以及上述解串器进行配置处理,使得上述第二控制器控制上述解串器进行上述解串处理。相比现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题,本技术的上述adas控制电路的控制方法,在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,通过上述第一控制器控制上述解串器进行上述解串处理,且上述第一控制器控制上述加串器进行上述加串处理,使得在上述第二控制器未启动成功的情况下,上述第一控制器可以同时控制上述解串器以及上述加串器进行相应处理,再在上述第一控制器以及上述第二控制器均启动成功的情况下,上述第一控制器一方面控制上述加串器进行上述加串处理,另一方面,上述第一控制器对上述第二控制器以及上述解串器进行上述配置处理,使得上述第二控制器可以控制上述解串器,保证了可以通过两个控制器分别控制上述解串器以及上述加串器,解决了现有技术中由于soc上电后启动较慢导致不能及时处理图像的问题,使得上述adas控制电路可以计时且效率较高的处理信息,保证了上述adas控制电路的效率较高。

93.2)、本技术的上述adas控制电路的控制装置中,通过上述第一控制单元在满足第一预定条件的情况下,控制上述解串器进行上述解串处理,且控制上述加串器进行加串处理,上述第一预定条件为:上述第一控制器启动成功且上述第二控制器未启动成功;通过上述第二控制单元在满足第二预定条件的情况下,控制上述加串器进行上述加串处理,且对上述第二控制器以及上述解串器进行预定处理,使得上述第二控制器控制上述解串器进行上述解串处理,上述第二预定条件为:上述第二控制器以及上述第一控制器均启动成功,上述预定处理包括配置处理。相比现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题,本技术的上述adas控制电路的控制装置,在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,通过上述第一控制器控制上述解串器进行上述解串处理,且上述第一控制器控制上述加串器进行上述加串处理,使得在上述第二控制器未启动成功的情况下,上述第一控制器可以同时控制上述解串器以及上述加串器进行相应处理,再在上述第一控制器以及上述第二控制器均启动成功的情况下,上述第一控制器一方面控制上述加串器进行上述加串处理,另一方面,上述第一控制器对上述第二控制器以及上述解串器进行上述配置处理,使得上述第二控制器可以控制上述解串器,保证了可以通过两

个控制器分别控制上述解串器以及上述加串器,解决了现有技术中由于soc上电后启动较慢导致不能及时处理图像的问题,使得上述adas控制电路可以计时且效率较高的处理信息,保证了上述adas控制电路的效率较高。

94.3)、本技术的上述的adas控制系统,包括adas控制电路以及第一控制器,其中,上述adas控制电路包括解串器、加串器以及第二控制器,其中,上述第二控制器与上述解串器连接,上述解串器与上述加串器连接,上述第二控制器用于控制上述解串器进行解串处理;上述第一控制器分别与上述解串器以及上述加串器连接,上述第一控制器用于执行任一种上述的方法。相比现有技术中的由于soc上电后启动较慢导致不能及时处理图像的问题,本技术的上述adas控制系统,在上述第一控制器启动成功且上述第二控制器未启动成功的情况下,通过上述第一控制器控制上述解串器进行上述解串处理,且上述第一控制器控制上述加串器进行上述加串处理,使得在上述第二控制器未启动成功的情况下,上述第一控制器可以同时控制上述解串器以及上述加串器进行相应处理,再在上述第一控制器以及上述第二控制器均启动成功的情况下,上述第一控制器一方面控制上述加串器进行上述加串处理,另一方面,上述第一控制器对上述第二控制器以及上述解串器进行上述配置处理,使得上述第二控制器可以控制上述解串器,保证了可以通过两个控制器分别控制上述解串器以及上述加串器,解决了现有技术中由于soc上电后启动较慢导致不能及时处理图像的问题,使得上述adas控制电路可以计时且效率较高的处理信息,保证了上述adas控制电路的效率较高。

95.以上所述仅为本技术的优选实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。