1.本公开实施例关于一种显示面板,特别是关于一种导线间具有不同距离的显示面板。

背景技术:

2.已知电子装置的显示面板会使用较多条信号线来驱动发光组件,以产生对应亮度(brightness)的光。然而,当电子装置使用较多条信号线时会占据较多的空间而造成显示面板的像素变大,因此,显示面板的分辨率将会产生降低等问题,如此可能会降低电子装置的显示质量。因此,需要一种新的显示面板,改变信号线的排列设置以改善显示面板的分辨率,改善前述的问题。

技术实现要素:

3.本公开实施例提供一种显示面板,包括基板与像素电路。像素电路设置于基板上,其中像素电路配置以驱动发光单元,且像素电路包括第一导线、相邻于第一导线设置的第二导线、第三导线与第四导线。第一导线与第二导线设置于第三导线与第四导线之间。第一导线、第二导线、第三导线与第四导线以相同方向延伸。第一导线和第二导线之间的第一距离y1与第三导线和第四导线之间的第二距离y2符合如下关系:0≦y1/y2≦0.25。

4.本公开实施例提供一种显示面板,包括基板、第一导线与第二导线。基板具有感测区与相邻于感测区的非感测区。第一导线与第二导线设置于基板上且以相同方向延伸。第二导线相邻于第一导线设置。在感测区内的第一导线和第二导线之间的第一距离与在非感测区内的第一导线与第二导线之间的第二距离不同。

附图说明

5.为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明,其中:

6.图1为依据本公开的一实施例的电子装置的示意图。

7.图2为依据本公开的一实施例的电子装置的像素的电路示意图。

8.图3为依据本公开的一实施例的电子装置的像素电路的导线的设置示意图。

9.图4为图3的a-a’线的剖面图。

10.图5为依据本公开的一实施例的导线的示意图。

11.图6为依据本公开的另一实施例的导线的示意图。

12.图7a为依据本公开的另一实施例的导线的示意图。

13.图7b为依据本公开的另一实施例的导线的示意图。

14.图8a为依据本公开的另一实施例的像素电路的导线的设置示意图。

15.图8b为依据本公开的另一实施例的像素电路的导线的设置示意图。

16.图9a为依据本公开的另一实施例的像素电路的导线的设置示意图。

17.图9b为依据本公开的另一实施例的像素电路的导线的设置示意图。

18.图10a为依据本公开的另一实施例的像素电路的导线的设置示意图。

19.图10b为依据本公开的另一实施例的像素电路的导线的设置示意图。

20.图11a为依据本公开的另一实施例的像素电路的导线的设置示意图。

21.图11b为依据本公开的另一实施例的像素电路的导线的设置示意图。

22.图12a为依据本公开的另一实施例的像素电路的导线的设置示意图。

23.图12b为依据本公开的另一实施例的像素电路的导线的设置示意图。

24.图13a为依据本公开的另一实施例的电子装置的示意图。

25.图13b为依据本公开的另一实施例的像素电路的导线的设置示意图。

26.图13c为依据本公开的另一实施例的像素电路的导线的设置示意图。

27.图14a为依据本公开的另一实施例的电子装置的示意图。

28.图14b为依据本公开的一实施例的显示面板的示意图。

29.图15a为依据本公开的一实施例的电子装置的示意图。

30.图15b为图15a的b-b’线的剖面图。

31.图16a为依据本公开的一实施例的显示面板的半导体层与导线的设置关系的俯视图。

32.图16b为图16a的c-c’线的剖面图。

33.图17a为依据本公开的一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。

34.图17b为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。

35.图17c为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。

36.图17d为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。

37.图17e为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。

38.图17f为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。

39.附图标记说明

40.100,1300,1400,1500:电子装置

41.110,1310,1510,1600,1700,1701,1702,1703,1704,1705,1706:显示面板

42.111,1311,1511,1650,1711:基板

43.112,1312,1313,1512,1513:像素

44.113,13121,13131:像素电路

45.114,1514:发光单元

46.120,120_1,120_2,130,130_1,130_2,140:驱动电路

47.vini1,vini2,sn11-1~sn11-5,sn12-1~sn12-2,em1~em2,sn21-1~sn21-5,sn22-1,ldata,lvdd,lvss,510,620,630,710,720,ldata1,ldata2,1630,1640,1732,1752:

导线

48.c1:电容

49.t1,t2,t3,t4,t5,t6,t7,t8,t9,t10,t11:晶体管

50.1:第一端

51.2:第二端

52.vdd,vss:参考电压

53.y1,y2,y1-1,y1-2:距离

54.511,621,631:非直线部分

55.5111:突出部

56.5112:内凹部

57.512,622,632:直线部分

58.623,633:虚拟延伸线。

59.1320,1520,1720:感测区

60.1330,1530,1710:非感测区

61.1516,1517:区域

62.1610,1620,1730,1740,1750,1760:半导体层

63.1731,1751,1761,1770:遮光层

64.1780:连接组件

具体实施方式

65.为让本公开的目的、特征或优点能更明显易懂,下文特举出实施例,并配合所附附图,做详细的说明。为了使读者能容易了解及附图的简洁,本公开中的多张附图可能只绘出整个装置的一部分,且附图中的特定组件并非依照实际比例绘图。

66.本公开说明书提供不同的实施例来说明本公开不同实施方式的技术特征。其中,实施例中的各组件的配置、数量及尺寸是为说明的用,并非用以限制本公开。另外,若实施例与附图中组件标号出现重复,是为了简化说明,并非意指不同实施例之间的关联性。

67.再者,说明书与权利要求书中所使用的序数例如“第一”、“第二”等的用词,以修饰权利要求书的组件,其本身并不意含及代表该请求组件有任何之前的序数,也不代表某一请求组件与另一请求组件的顺序、或是制造方法上的顺序,该多个序数的使用仅用来使具有某命名的一请求组件得以和另一具有相同命名的请求组件能作出清楚区分。

68.在本公开中,各实施例间特征只要不违背发明精神或相冲突,均可任意混合搭配使用。

69.在通篇说明书及权利要求书当中所提及的“包括”为一开放式用语,故应解释成“包括但不限定于”。

70.再者,“连接”、“耦接”在此包括任何直接及间接的连接手段。因此,当组件或膜层被称为“连接”至另一个组件或膜层时,它可以直接连接到此另一组件或膜层,或者两者之间存在有插入的组件或膜层。当组件被称为“直接连接”至另一个组件或膜层时,两者之间不存在有插入的组件或膜层。若文中描述电路上的一第一装置耦接至一第二装置,则代表第一装置可直接电连接第二装置,当第一装置直接电连接第二装置时,第一装置与第二装

置之间只透过导线或被动组件(例如电阻、电容等)连接,没有其他电子组件连接于第一装置与第二装置之间。

71.本文中所提到的方向用语,例如:“上”、“下”、“前”、“后”、“左”、“右”等,仅是参考附图的方向。因此,使用的方向用语是用来说明,而并非用来限制本公开。在附图中,各附图示出的是特定实施例中所使用的方法、结构及/或材料的通常性特征。然而,该多个附图不应被解释为界定或限制由该多个实施例所涵盖的范围或性质。举例来说,为了清楚起见,各膜层、区域及/或结构的相对尺寸、厚度及位置可能缩小或放大。

72.应了解到,当组件或膜层被称为在另一个组件或膜层“上”,它可以直接在此另一组件或膜层上,或者两者之间存在有插入的组件或膜层(非直接情况)。相反地,当组件被称为“直接”在另一个组件或膜层“上”,两者之间不存在有插入的组件或膜层。关于接合、连接的用语亦可包含两个结构都可移动,或者两个结构都固定的情况。

73.在本公开中,厚度、长度与宽度的量测方式可以是采用光学显微镜(optical microscopy,om)量测而得,厚度或长度可以由扫描式电子显微镜(scanning electron microscope,sem)中的剖面影像量测而得,但不以此为限。另外,任两个用来比较的数值或方向,可存在着一定的误差。

74.应该理解,尽管术语第一、第二等可以在此用于描述各种组件、部件、区域、层或/及部分,该多个组件、部件、区域、层或/及部分不应受该多个术语的限制。该多个术语仅用于区分一个组件、部件、区域、层或/及部分与另一个组件、部件、区域、层或/及部分。因此,在不脱离本公开启示内容的情况下,下面讨论的第一组件、第一部件、第一区域、第一层或第一部分亦可以被称为第二组件、第二部件、第二区域、第二层或第二部分。

75.此外,「在第一数值和第二数值之间的范围内」或「在第一数值和第二数值之间的范围内」等短语表示该范围包括第一数值、第二数值以及它们之间的其他数值。

76.术语“大约”、“等于”、“相等”或“相同”、“实质上”或“大致上”通常代表落在给定数值或范围的20%范围内,或代表落在给定数值或范围的10%、5%、3%、2%、1%或0.5%范围内。

77.在一实施例中,电子装置可以包含液晶(liquid crystal,lc)、有机发光二极管(organic light emitting diode,oled)、无机发光二极管(light emitting diode,led)、量子点(quantum dot,qd)、荧光材料、磷光材料、其他适合的材料或上述材料的组合,但本公开不限于此。无机发光二极管可例如包括毫米/次毫米发光二极管(mini light emitting diode,mini led)、微发光二极管(micro light emitting diode,micro led)或量子点发光二极管(quantum dot light emitting diode,qled),但本公开不限于此。

78.在一些实施例中,电子装置可以是显示设备(display device)、感测装置(sensing device)、触控装置(touch device)、曲面装置(curved device)、拼接装置(titled device)或非矩形装置(free shape device),也可以是可弯折或可挠式拼接装置,但不以此为限。

79.需注意的是,电子装置可为前述的任意排列组合,但不以此为限。此外,电子装置的外型可为矩形、圆形、多边形、具有弯曲边缘的形状或其他适合的形状。电子装置可以具有驱动系统、控制系统、光源系统、层架系统等周边系统以支持显示设备。

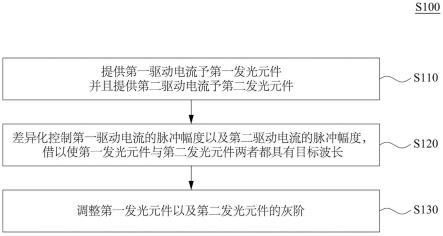

80.在一实施例中,电子装置可以是显示设备,但本公开不限于此。请合并参考图1、图

2、图3与图4,图1为依据本公开的一实施例的电子装置100的示意图。图2为依据本公开的一实施例的电子装置100的像素112的电路示意图。图3为依据本公开的一实施例的电子装置100的像素电路113的导线的设置示意图。图4为图3的a-a’线的剖面图。电子装置100可以包括显示面板110,显示面板110可以至少包括基板111、像素112、驱动电路120、驱动电路130与驱动电路140。

81.另外,在图1中,像素112的数量仅示出一个,但本公开不限于此。在一些实施例中,像素112的数量可以为多个,且以矩阵形式排列,并设置于基板111上。请参考图2,像素112包括像素电路113以及与像素电路113耦接的发光单元114。像素电路113可以设置于基板111上,且像素电路113配置以驱动发光单元114。

82.发光单元114的第一端可以耦接像素电路113,且发光单元114的第二端可以耦接导线lvss,以接收参考电压vss(例如接地电压)。在本实施例中,发光单元114可以是有机发光二极管、无机发光二极管、其他适合的材料或上述材料的组合,但本公开不限于此。发光单元114的第一端可以是阳极端(anode),而第二端可以是阴极端(cathode),但本公开不限于此。

83.像素电路113可以包括电容c1、晶体管t1、晶体管t2、晶体管t3、晶体管t4、晶体管t5、晶体管t6、晶体管t7、导线vini1、导线sn11-1、导线sn12-1、导线em1、导线sn21-1、导线sn22-1、导线ldata、导线lvdd,如图2所示,但本公开不限于此。

84.电容c1具有第一端与第二端。电容c1的第一端耦接导线lvdd,以接收参考电压vdd(例如工作电压)。

85.晶体管t1、晶体管t2、晶体管t3、晶体管t4、晶体管t5、晶体管t6、晶体管t7各自包括栅极(gate)、通道区(channel region)、源极区(source region)及漏极区(drain region)。通道区、源极区及漏极区可由半导体层(semiconductor layer)形成。通道区与栅极重叠。在一实施例中,可有导体层透过孔洞而耦接于源极区与漏极区以形成源极电极与漏极电极。半导体层可包括硅半导体(silicon semiconductor)、氧化物半导体(oxide semiconductor)、其他合适的材料或前述材料的组合,本公开不限于此。硅半导体可包括非晶硅(amorphous silicon)半导体、单晶硅(single crystalline silicon)半导体、多晶硅(poly-silicon)半导体或其他合适的材料,本公开不限于此。氧化物半导体可包括氧化铟镓锌(indium gallium zinc oxide,igzo)半导体或其他合适的材料,本公开不限于此。晶体管可以包括底栅极(bottom gate)晶体管、顶栅极(top gate)晶体管、双栅极(double gate)晶体管或前述晶体管的组合,本公开不限于此。此外,当晶体管包含不同的半导体层时,其源极区以及漏极区(或源极电极以及漏极电极)可以互换,本公开不限于此。

86.在一实施例中,像素电路113可以包含至少部分的导体层,导体层可包括导线并可耦接一晶体管的栅极,而导线上可有信号并透过栅极控制该晶体管。此外,若不同晶体管可共享半导体,意即一晶体管的漏极区耦接于另一晶体管的源极区,则以两通道区之间的一半区域属一晶体管的漏极区,另一半属另一晶体管的源极区。

87.晶体管t1具有栅极、第一端1与第二端2。晶体管t1的栅极耦接电容c1的第二端。在本实施例中,晶体管t1可以是低温多晶硅(low temperature poly-silicon,ltps)半导体p型薄膜晶体管,但本公开不限于此。此时晶体管t1的第一端1例如为漏极区,晶体管t1的第二端2例如为源极区,但亦可第一端1例如为源极区,晶体管t1的第二端2例如为漏极区,本

公开不限于此。在一些实施例中,晶体管t1也可以是低温多晶硅半导体n型薄膜晶体管,或是氧化物(例如氧化铟镓锌)半导体薄膜晶体管,本公开不限于此。

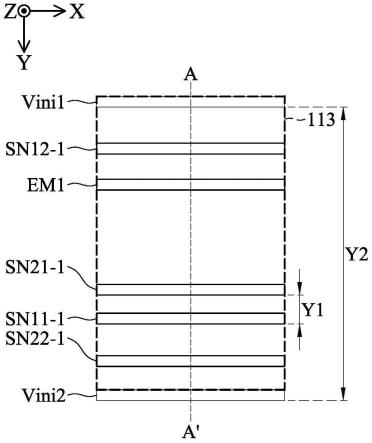

88.晶体管t2具有栅极、第一端1与第二端2。晶体管t2的栅极耦接导线sn11-1,以接收控制信号(例如扫描驱动信号)。晶体管t2的第一端1耦接导线ldata,以接收数据信号。晶体管t2的第二端2耦接晶体管t1的第一端1。在本实施例中,晶体管t2可以是低温多晶硅半导体p型薄膜晶体管,晶体管t2的第一端1例如为漏极区,晶体管t2的第二端2例如为源极区,或是第一端1为源极区,第二端2为漏极区,本公开不限于此。在一些实施例中,晶体管t2也可以是低温多晶硅半导体n型薄膜晶体管,或是氧化物(例如氧化铟镓锌)半导体薄膜晶体管,本公开不限于此。

89.晶体管t3具有栅极、第一端1与第二端2。晶体管t3的栅极耦接导线sn22-1,以接收控制信号(例如扫描驱动信号)。晶体管t3的第一端1耦接晶体管t1的栅极。晶体管t3的第二端2耦接导线vini,以接收参考信号(例如共同信号(common signal)),例如可用于对发光单元114进行重置的信号。在本实施例中,晶体管t3可以是氧化铟镓锌半导体p型薄膜晶体管,但本公开不限于此。晶体管t3的第一端1例如为源极区,晶体管t3的第二端2例如为漏极区,或是第一端1为漏极区,第二端2为源极区,本公开不限于此。在一些实施例中,晶体管t3也可以是氧化铟镓锌半导体n型薄膜晶体管,或是硅半导体(例如低温多晶硅半导体)薄膜晶体管,本公开不限于此。

90.晶体管t4具有栅极、第一端1与第二端2。晶体管t4的栅极耦接导线em1,以接收控制信号(例如发射信号(emission signal))。晶体管t4的第一端1耦接导线lvdd,以接收参考电压vdd(例如工作电压)。晶体管t4的第二端2耦接晶体管t2的第二端2。在本实施例中,晶体管t4可以是低温多晶硅半导体p型薄膜晶体管,晶体管t4的第一端1例如为漏极区,晶体管t4的第二端2例如为源极区,或是第一端1为源极区,第二端2为漏极区,本公开不限于此。在一些实施例中,晶体管t4也可以是低温多晶硅半导体n型薄膜晶体管,或是氧化物(例如氧化铟镓锌)半导体薄膜晶体管,本公开不限于此。

91.晶体管t5具有栅极、第一端1与第二端2。晶体管t5的栅极耦接晶体管t4的栅极以及导线em1。晶体管t5的第一端1耦接晶体管t1的第二端2。晶体管t5的第二端2耦接发光单元114的第一端。在本实施例中,晶体管t5可以是低温多晶硅半导体p型薄膜晶体管,晶体管t5的第一端1例如为漏极区,晶体管t5的第二端2例如为源极区,或是第一端1为源极区,第二端2为漏极区,本公开不限于此。在一些实施例中,晶体管t5也可以是低温多晶硅半导体n型薄膜晶体管,或是氧化物(例如氧化铟镓锌)半导体薄膜晶体管,本公开不限于此。

92.晶体管t6具有栅极、第一端1与第二端2。晶体管t6的栅极耦接导线sn21-1,以接收控制信号(例如扫描驱动信号)。晶体管t6的第一端1耦接晶体管t1的栅极。晶体管t6的第二端2耦接晶体管t1的第二端2。在本实施例中,晶体管t6可以是氧化铟镓锌半导体p型薄膜晶体管,晶体管t6的第一端1例如为漏极区,晶体管t6的第二端2例如为源极区,或是第一端1为源极区,第二端2为漏极区,本公开不限于此。在一些实施例中,晶体管t6也可以是氧化铟镓锌半导体n型薄膜晶体管,或是氧化物(例如氧化铟镓锌)半导体薄膜晶体管,本公开不限于此。

93.晶体管t7具有栅极、第一端1与第二端2。晶体管t7的栅极耦接导线sn12-1,以接收控制信号(例如扫描驱动信号)。晶体管t7的第一端1耦接导线vini1,以接收参考信号(例如

共同信号)。晶体管t7的第二端2耦接晶体管t5的第二端。在本实施例中,晶体管t7可以是低温多晶硅半导体p型薄膜晶体管,晶体管t7的第一端1例如为漏极区,晶体管t7的第二端2例如为源极区,或是第一端1为源极区,第二端2为漏极区,本公开不限于此。在一些实施例中,晶体管t7也可以是低温多晶硅半导体n型薄膜晶体管,或是氧化物(例如氧化铟镓锌)半导体薄膜晶体管,本公开不限于此。

94.导线sn11-1与导线sn12-1耦接驱动电路120,且驱动电路120配置以提供对应的控制信号(例如扫描驱动信号)。导线sn21-1与导线sn22-1耦接驱动电路130,且驱动电路130配置以提供对应的控制信号(例如扫描驱动信号)。导线ldata与导线lvdd耦接驱动电路140,且驱动电路140配置以提供数据信号与参考电压vdd(例如工作电压)。

95.在一些实施例中,导线sn11-1、导线sn12-1、导线em1、导线vini1、导线vini2、导线sn21-1与导线sn22-1可以设置于不同层而使用不同的金属层制作,如图4所示。举例来说,导线sn11-1、导线sn12-1与导线em1例如设置于第一层且使用第一金属层制作,导线vini1、导线vini2例如设置于第二层且使用第二金属层制作,导线sn21-1与导线sn22-1设置于例如设置于第三层且使用第三金属层制作,其中上述第一层、第二层与第三层为不同层,但本公开不限于此。在一些实施例中,当多个像素沿着y方向排列时,导线vini1及导线vini2可与邻近的像素共享,但依据导线的排列情况,可以是不同的导线与邻近的像素共享,本公开不限于此。

96.在一些实施例中,导线sn11-1、导线sn12-1、导线em1、导线vini1、导线sn21-1与导线sn22-1可以接收不同信号。在本实施例中,例如可以信号在电子装置100上所产生的结果(例如使晶体管开启或关闭;或使发光单元发光或不发光等)、用途(例如作为开关晶体管;或作为固定电压电位;或作为驱动电压信号;或作为数据信号等)、电压值大小或频率高低的不同来区分为不同信号,但本公开不限于此。

97.在一些实施例中,导线sn11-1、导线sn12-1、导线em1、导线vini1、导线vini2、导线sn21-1与导线sn22-1可以朝一相同方向延伸,例如x方向,但本公开不限于此。

98.在一些实施例中,导线sn11-1可以是第一导线,导线sn21-1可以是第二导线,导线vini1可以是第三导线,导线vini2可以是第四导线,但本公开不限于此。其中,导线sn11-1与导线sn21-1可以是相邻设置,且导线sn11-1与导线sn21-1例如设置于导线vini1与导线vini2之间。此处,导线sn11-1与导线sn21-1相邻设置,是指并无其他导线设置于两导线之间。另外,在y方向上,导线sn11-1可以与导线sn21-1之间的距离可以是距离y1(例如第一距离),导线vini1与导线vini2之间的距离可以是距离y2(例如第二距离)。举例来说,距离y1例如取导线sn11-1与导线sn21-1的同侧边在垂直于导线sn11-1与导线sn21-1的延伸方向(如x方向)之间的距离,意即取导线sn11-1与导线sn21-1的同侧边在y方向之间的距离,距离y2例如取导线vini1与导线vini2的同侧边在y方向之间的距离。进一步来说,距离y1例如取导线sn11-1与导线sn21-1靠近芯片接合(ic bonding)区的一侧边之间的距离,距离y2例如取导线vini1与导线vini2靠近芯片接合区的一侧边之间的距离,但本公开不限于此。

99.请参考图3,在俯视方向(基板111的法线方向,例如为z方向),导线sn11-1、导线sn12-1、导线em1、导线vini1、导线sn21-1与导线sn22-1可以是不同层的金属层所制作,因此可以缩短不同层的金属层在y方向上的距离,或可以重叠设置。

100.此外,距离y1与距离y2例如符合如下关系:0≦y1/y2≦0.25。进一步来说,距离y1

与距离y2例如符合如下关系:0≦y1/y2≦0.102。另外,距离y2例如为40微米(um)、50微米、70微米或98微米等,但本公开不限于此。如此一来,当缩短导线之间的距离时,可让显示面板在相同的尺寸下提高像素密度(pixels per inch,ppi);或可让显示面板增加未被导线遮蔽的区域。

101.在一些实施例中,导线sn11-1可以是第一导线,导线sn22-1可以是第二导线,导线vini1可以是第三导线,导线vini2可以是第四导线,但本公开不限于此。其中,导线sn11-1与导线sn22-1可以是相邻设置,且导线sn11-1与导线sn22-1例如设置于导线vini1与导线vini2之间。此处,导线sn11-1与导线sn22-1相邻设置,是指并无其他导线设置于两导线之间。另外,在y方向上,导线sn11-1可以与导线sn22-1之间的距离可以是距离y1(图未示),导线vini1与导线vini2之间的距离可以是距离y2。

102.在图3中,导线vini1、导线sn11-1、导线sn12-1、导线em1、导线sn21-1、导线sn22-1的侧边延伸方向大致平行导线的延伸方向,但本公开不限于此。在一些实施例中,可如图5所示的导线510或图6所示的导线620与导线630,其导线部分区域的侧边其边缘曲率有变化,故其部分区域的延伸方向与导线的延伸方向不平行。在图5中,可以看出导线510包含有非直线部分511及直线部分512,非直线部分511的边缘曲率有变化(例如有突出部5111或内凹部5112),因此在距离的量测上则以导线510的直线部分512作为依据。另外,如图6所示,两条导线620、630的直线部分622、632可不对应设置,例如导线620的直线部分622可对应到导线630的非直线部分631,导线620的非直线部分621可对应到导线630的直线部分632,因此,在距离的量测上可以取导线620的直线部分622的一侧边的延伸线623以及导线630的直线部分632的一侧边的延伸线633作为依据来量测距离。

103.另外,在一些实施例中,当导线710与导线720至少部分重叠时,表示导线710与导线720之间的距离为0,分别如图7a(完全重叠)或图7b(部分重叠)所示。

104.图8a为依据本公开的另一实施例的像素电路的导线的设置示意图。在图8a的像素电路113中,导线sn11-1与导线sn22-1在z方向上至少部分重叠。在本实施例中,距离y1可以是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0),或是由导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离。距离y2可以是导线vini1与导线vini2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

105.图8b为依据本公开的另一实施例的像素电路的导线的设置示意图。在图8b的像素电路113中,导线sn11-1与导线sn21-1在z方向上至少部分重叠。在本实施例中,距离y1可以是导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0),或是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离。距离y2可以是导线vini1与导线vini2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

106.图9a为依据本公开的另一实施例的像素电路的导线的设置示意图。在图9a的像素电路113中,导线vini2与导线sn12-2在z方向上至少部分重叠,以及导线sn11-1与导线sn21-1在z方向上至少部分重叠。在本实施例中,距离y1可以是导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0),或是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距

离,或是由线vini2与导线sn12-2(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0)。距离y2可以是导线em1与导线em2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

107.图9b为依据本公开的另一实施例的像素电路的导线的设置示意图。在图9b的像素电路113中,导线vini1与导线em1在z方向上至少部分重叠。在本实施例中,距离y1可以是导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离,或是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离,或是导线vini1与导线em1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0)。距离y2可以是导线sn12-1与导线sn12-2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

108.图10a为依据本公开的另一实施例的像素电路的导线的设置示意图。在图10a的像素电路113中,导线vini1与导线sn12-1在z方向上至少部分重叠,以及导线sn11-1与导线sn22-1在z方向上至少部分重叠。在本实施例中,距离y1可以是导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离,或是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0),或是导线vini1与导线sn12-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0)。距离y2可以是导线vini1与导线vini2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

109.图10b为依据本公开的另一实施例的像素电路的导线的设置示意图。在图10b的像素电路113中,导线vini1与导线em1在z方向上至少部分重叠,以及导线sn11-1与导线sn22-1在z方向上至少部分重叠。在本实施例中,距离y1可以是导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离,或是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0),或是导线vini1与导线em1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0)。距离y2可以是导线sn12-1与导线sn12-2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

110.图11a为依据本公开的另一实施例的像素电路的导线的设置示意图。在图11a的像素电路113中,导线vini1与导线sn12-1在z方向上至少部分重叠,以及导线sn11-1与导线sn21-1在z方向上至少部分重叠。在本实施例中,距离y1可以是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离,或是导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0),或是导线vini1与导线sn12-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0)。距离y2可以是导线vini1与导线vini2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

111.图11b为依据本公开的另一实施例的像素电路的导线的设置示意图。在图11b的像素电路113中,导线vini1与导线em1在z方向上至少部分重叠,以及导线sn11-1与导线sn21-1在z方向上至少部分重叠。在本实施例中,距离y1可以是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离,或是导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0),或

是导线vini1与导线em1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0)。距离y2可以是导线sn12-1与导线sn12-2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

112.图12a为依据本公开的另一实施例的像素电路的导线的设置示意图。在图12a的像素电路113中,像素电路113还包括导线sn23-1与导线sn24-1,可由设置于半导体层下方的导体层所形成。导线sn21-1与sn23-1在z方向上至少部分重叠,且导线sn21-1与sn23-1可为不同层并分别耦接像素电路113的晶体管t6的栅极,使得晶体管t6具有双栅极的功能,可降低晶体管t6的漏电流。导线sn22-1与导线sn24-1在z方向上至少部分重叠,且导线sn22-1与导线sn24-1可为不同层并分别耦接像素电路113的晶体管t3的栅极,使得晶体管t3具有双栅极的功能,可降低晶体管t3的漏电流。另外,在图12a中,还可以看出导线sn11-1与导线sn22-1及导线sn24-1在z方向上至少部分重叠。

113.在本实施例中,距离y1可以是导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离,或是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0)。距离y2可以是导线vini1与导线vini2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

114.图12b为依据本公开的另一实施例的像素电路的导线的设置示意图。图12b与图12a类似,其中导线sn21-1与sn23-1以及导线sn22-1与sn24-1的说明可参考图12a的实施例,故在此不再赘述。另外,在图12b中,还可以看出导线sn11-1与导线sn21-1及导线sn23-1在z方向上至少部分重叠。在本实施例中,距离y1可以是导线sn11-1与导线sn21-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离,或是导线sn11-1与导线sn22-1(例如接收不同信号或位于不同层的第一导线与第二导线)之间的距离(例如0)。距离y2可以是导线vini1与导线vini2(例如接收相同类型信号的第三导线与第四导线)之间的距离。

115.图13a为依据本公开的另一实施例的电子装置的示意图。图13b为依据本公开的另一实施例的像素电路的导线的设置示意图。图13c为依据本公开的另一实施例的像素电路的导线的设置示意图。图13a的电子装置1300与图1的电子装置100类似。请同步参考图13a、图13b及图13c,电子装置1300包括显示面板1310,显示面板1310可至少包括基板1311、像素1312与像素1313、驱动电路120、驱动电路130与驱动电路140。在本实施例中,驱动电路120、驱动电路130和驱动电路140与图1的驱动电路120、驱动电路130和驱动电路140相同或相似,可参考图1的实施例的说明,于此不再赘述。在本实施例中,像素1312与像素1313与图1的像素112相同或相似,可参考图1的实施例的说明,于此不再赘述。

116.请合并参考图13a与图13b,显示面板1310包括感测区1320与相邻于感测区1320的非感测区1330,而且感测区1320与非感测区1330均设置于基板1311上。于感测区1320下方可以设置感测组件(图未示),即感测区可与感测组件重叠。感测组件可以例如是红外线传感器、相机、光传感器等,但本公开不限于此。感测区1320可以拥有较高的透明度,提高通过显示面板并可被感测组件感测的光信号。另外,非感测区1330以及部分区域的感测区1320例如可为显示面板1310的显示区。

117.像素1312可以设置于显示面板1310的感测区1320内,像素1313可以设置于显示面板1310的非感测区1330内。像素1312可包括像素电路13121以及与像素电路13121耦接的发

光单元(图未示),像素1313可包括像素电路13131以及与像素电路13131耦接的发光单元(图未示),在本实施例中,像素电路13121与像素电路13131与图2的像素电路113相同或相似,可参考图2的实施例的说明,于此不再赘述。像素电路13121与像素电路13131可以分别至少包括导线vini1、导线sn12-1、导线em1、导线sn21-1、导线sn11-1与导线sn22-1。在本实施例中,导线vini1、导线sn12-1、导线em1、导线sn21-1、导线sn11-1和导线sn22-1与图2~图4的导线vini1、导线sn12-1、导线em1、导线sn21-1、导线sn11-1和导线sn22-1相同或相似,可参考图2~图4的实施例的说明,故在此不再赘述。类似地,导线sn11-1、导线sn12-1、导线em1、导线vini1、导线vini2(与下一个像素共享)、导线sn21-1与导线sn22-1可朝相同方向延伸,例如以x方向延伸,但本公开不限于此。

118.在一些实施例中,导线sn11-1可以是第一导线,导线sn21-1可以是第二导线,但本公开不限于此。另外,在y方向上,在感测区1320的像素电路13121的导线sn11-1与导线sn21-1之间的距离可以为距离y1-1(例如第一距离),在非感测区1330的像素电路13131的导线sn11-1与导线sn21-1之间的距离可以为距离y1-2(例如第二距离)。其中,距离y1-1与距离y1-2的量测方式,可以参考前述距离y1与距离y2的实施例,故在此不再赘述。

119.在本实施例中,距离y1-1与距离y1-2可以不同。进一步来说,在一些实施例中,距离y1-1可以小于距离y1-2,如图13b所示。另外,在一些实施例中,如图13c所示,距离y1-1也可以设置大于距离y1-2。如此一来,借由调整距离y1-1与距离y1-2的关系,可以调整不同的区域范围提供给感测组件(例如红外线传感器、相机、光传感器等)使用,改善感测组件的感测效能。

120.图14a为依据本公开的另一实施例的电子装置的示意图。图14b为依据本公开的一实施例的显示面板的示意图。图14a的电子装置1400与图13a的电子装置1300类似,于此不再赘述。电子装置1400包括显示面板1310,显示面板1310可至少包括基板1311、像素1312、驱动电路120_1、驱动电路120_2、驱动电路130_1、驱动电路130_2与驱动电路140。驱动电路120_1及驱动电路120_2与图13a的驱动电路120相同或相似、驱动电路130_1及驱动电路130_2与图13a的驱动电路130相同或相似,驱动电路140与图13a的驱动电路140相同或相似,可参考图13a的实施例的说明,故在此不再赘述

121.请合并参考图14a与图14b,显示面板1310包括感测区1320与非感测区1330。感测区1320可以设置感测组件,例如红外线传感器、相机、光传感器等,但本公开不限于此。另外,非感测区1330以及部分区域的感测区1320例如可为显示面板1310的显示区。

122.另外,导线sn11-1至导线sn11-7可以对应地耦接驱动电路120_1与驱动电路120_2,例如导线sn11-2可耦接驱动电路120_1,而导线sn11-6可耦接驱动电路120_2,但本公开不限于此。导线sn21-1至导线sn21-7可以对应地耦接驱动电路130_1与驱动电路130_2,例如导线sn21-2可耦接驱动电路130_1,而导线sn21-6可耦接驱动电路130_2,但本公开不限于此。导线ldat1、导线ldata2、导线lvdd可以对应地耦接驱动电路140。

123.图15a为依据本公开的一实施例的电子装置的示意图。图15b为图15a的b-b’线的剖面图。图15a的电子装置1500与图13a的电子装置1300类似,于此不再赘述。请合并参考图15a与图15b,电子装置1500包括显示面板1510,且显示面板1510可以至少包括基板1511、像素1512与像素1513。基板1511包括感测区1520与非感测区1530。感测区1520可以设置感测组件,例如红外线传感器、相机、光传感器等,并设置于基板1511下方,但本公开不限于此。

另外,非感测区1530例如为显示面板1510的显示区。

124.像素1512可以设置于感测区1520内,像素1513可以设置于非感测区1530内。像素1512可以至少包括晶体管t8、晶体管t9与发光单元1514,其中区域1516为发光单元1514的发光区域。发光单元1514例如可为有机发光二极管,包括上电极te、下电极be以及位于上电极te与下电极be之间的发光层el,但本公开不限于此。晶体管t8与晶体管t9可在z方向部分重叠设置,且位于发光单元1514的下方。如此一来,可降低感测区1520中不透光的区域,以提升光线的穿透度,而可让外界光l(如图15b的箭头所示)穿过感测区1520的可透光区域而可被感测组件所接收。另外,像素1513可以至少包括晶体管t10、晶体管t11与发光单元(未示出),其中区域1517为发光单元的发光区域。晶体管t10与晶体管t11可在z方向分别设置,晶体管t10与晶体管t11可在z方向未重叠设置,且晶体管t10与晶体管t11位于发光单元(未示出)的下方,但本公开不限于此。

125.在一些实施例中,晶体管t8与晶体管t10例如为氧化物半导体(例如氧化铟镓锌半导体)p型或n型薄膜晶体管,而晶体管t9与晶体管t11例如为硅半导体(例如低温多晶硅半导体)p型或n型薄膜晶体管,但本公开不限于此。

126.图16a为依据本公开的一实施例的显示面板的半导体层与导线的设置关系的俯视图。图16b为图16a的c-c’线的剖面图。请合并参考图16a与图16b,显示面板1600可以包括半导体层1610、半导体层1620、导线1630与导线1640。导线1630与导线1640可在z方向重叠设置。另外,在基板1650上,依序设置有半导体层1610、导线1630、半导体层1620与导线1640。在本实施例中,半导体层1610例如为硅半导体(例如低温多晶硅半导体层),导线1630例如为驱动硅半导体晶体管的扫描线,半导体层1620例如为氧化物(例如氧化铟镓锌)半导体层,导线1640例如为驱动氧化物(例如氧化铟镓锌)晶体管的扫描线,但本公开不限于此。由于导线1630与导线1640可在z方向部分重叠设置,可降低不透光区域的面积,以提升光线的穿透度。

127.图17a为依据本公开的一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。请参考图17a,基板1711包括感测区1720与相邻于感测区1720的非感测区1710。半导体层1730、半导体层1740与遮光层1731设置在非感测区1710。半导体层1750、半导体层1760、遮光层1751、遮光层1761设置在感测区1720。半导体层1730与半导体层1740可设置于不同层。遮光层1731可位于半导体层1730的下方。半导体层1750与半导体层1760可设置于不同层。遮光层1751可位于半导体层1750的下方。遮光层1761可位于半导体层1760的下方。

128.在本实施例中,半导体层1730与半导体层1750例如为氧化物半导体(例如氧化铟镓锌半导体)层,且设置于同一层。半导体层1740与半导体层1760例如为硅半导体(例如低温多晶硅半导体)层,且设置于同一层。遮光层1731与遮光层1751可设置于同一层,而遮光层1761与遮光层1731和遮光层1751可设置于不同层。遮光层1731、遮光层1751、遮光层1761可以是具遮旋光性的导体层(例如是金属材料)或是有机层(例如是黑矩阵,black matrix)或其他适合的材料或前述的组合,本公开不限于此。

129.图17b为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。图17b的显示面板1701与图17a的显示面板1700相似,相同的处可参考图17a的实施例的说明。在图17b中,遮光层1731、遮光层1751与遮光层1761可设置于同

一层。

130.图17c为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。图17c的显示面板1703与图17a的显示面板1700相似,相同的处可参考图17a的实施例的说明。在图17c中,遮光层1751与遮光层1761可设置于同一层,而遮光层1731与遮光层1751和遮光层1761可设置于不同层。

131.图17d为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。图17d的显示面板1704与图17c的显示面板1703相似,相同的处可参考图17c的实施例的说明。在图17d中,遮光层1770与遮光层1731可设置于不同层,且遮光层1770位于半导体层1750与半导体层1760的下方。如此一来,透过较大面积的遮光层1770可增加对组件的保护效果。

132.图17e为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。图17e的显示面板1705与图17d的显示面板1704相似,相同的处可参考图17d的实施例的说明。在图17e中,导线1732可以作为半导体层1730的上栅极,而当遮光层1731的材质为导电材料(例如金属)时,可以作为半导体层1730的下栅极,此外,导线1732可以透过连接组件1780与遮光层1731耦接。此外,导线1752可以作为半导体层1750的栅极。

133.图17f为依据本公开的另一实施例的显示面板的感测区与非感测区中的半导体层与遮光层设置的剖面图。图17f的显示面板1706与图17e的显示面板1705相似,相同的处可参考图17e的实施例的说明。在图17f中,导线1752可以作为半导体层1750的上栅极,而当遮光层1751的材质为导电材料(例如金属)时,可以作为半导体层1750的下栅极,此外,导线1752亦可以透过连接组件1780而与遮光层1751耦接。

134.在本公开的图17a至图17f的实施例中,可调整遮光层之间的距离,使显示面板增加未被遮光层遮蔽的区域,而可提供给感测组件(例如红外线传感器、相机、光传感器等)使用,但本公开不限于此。

135.综上所述,本公开实施例的显示面板,透过将像素电路的第一导线与第二导线相邻设置,并将第一导线与第二导线设置于第三导线与第四导线之间,且第一导线、第二导线、第三导线与第四导线以相同方向延伸,以及第一导线和第二导线之间的第一距离y1与第三导线和第四导线之间的第二距离y2符合如下关系:0≦y1/y2≦0.25。另外,本公开实施例还可以将显示面板具有感测区与相邻于感测区的非感测区,感测区与非感测区均设置于基板上且将第一导线与第二导线设置于基板上且以相同方向延伸,将第二导线设置相邻于第一导线,以及在感测区上的第一导线和第二导线之间的第一距离与在非感测区上的第一导线与第二导线之间的第二距离不同。如此一来,可以缩短导线之间的距离,而可提高像素密度,或可空出一些区域提供给感测组件(例如红外线传感器、相机、光传感器等)使用。

136.本公开虽以实施例公开如上,然其并非用以限定本公开的范围,任何本领域的技术人员,在不脱离本公开的精神和范围内,可将数个不同实施例中的特征进行替换、重组、混合或可做些许的调整、组合、更动与润饰以完成其他实施例,因此本公开的保护范围当视后附的申请专利范围所界定者为准。

137.虽然本发明已以较佳实施例揭示如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的修改和完善,因此本发明的保护范

围当以权利要求书所界定的为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。