1.本发明涉及微控制器通信外设结构领域,尤其是多功能通信外设。

2.背景

3.在目前微处理器通信外设,一般一个外设只负责一种通信形式,对于多种类似通信功能由多种外设分别实现,本发明将类似通信外设整合为一个多功能外设,共享缓存,并通过指针访问,提高了效率和利用率。

技术实现要素:

4.一个多功能通信接口,集成多种通信协议,包括但不限制为通用异步收发传输器(uart)、串行外设接口(spi)、通用串行总线(usb)、控制器域网(can)。这些协议虽然不同,但是可以利用一个统一的通信端口兼容这些协议,并使用同一个存储作为数据的缓存。通过指针而非队列方式的缓存,拥有更多灵活性。

附图说明

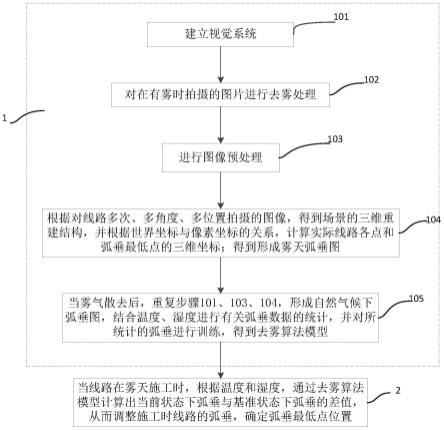

5.图1是多功能通信接口基本结构图

具体实施方式

6.通常情况下,所公开的实施例在下面的说明中,给出了具体的细节,以便于透彻理解这些实施例。但是,本领域技术人员应当理解的是,这些实施例也可以不用这些具体细节来实现。尤其是关于指针具体数字和缓存器地址具体数字以及各个功能性部件,实施例中的方法只是为了说明意图而选用的特例技术,这些实施例可以选择其他公知方法。

7.第一实施例

8.图1说明多功能通信接口基本结构图,包含:

9.输入输出管脚阵列部件101;

10.输入控制器部件102;

11.输出控制器部件103;

12.输入缓存部件104;

13.输出缓存部件105;

14.读写接口控制器部件106;

15.该通信接口外设,在对外部的功能引脚例如串口uart的发送管脚txd,接收管脚rxd,或者spi总线的时钟管脚sclk,输入输出管脚somi simo片选信号cs等全部进入输入输出管脚阵列部件101,在该部件,可以通过配置其寄存器的方式来选择每个管脚的具体功能,例如该部件有4个输入输出管脚分别为io1、io2、io3、io4,则这四个管脚可以配置为,io1为txd,io2为rxd,也可以配置为io3为txd,io4为rxd,或者配置为io1为sclk,io2为mosi,io3为miso,io4为cs,还可以配置为io1为cs,io2为mosi,io3为miso,io4为cslk。以上只是举例,还有更多情况和协议不再枚举。通过输入输出管脚阵列部件101的选择后,输入

控制器部件102可以获得总线相应功能信号的情况,并按照具体协议情况将数据存储到输入缓存部件104。同时,输出控制器部件103也可以根据输出缓存部件105的存储情况,将相应功能信号通过输入输出管脚阵列部件101发送至总线。对于有些协议,例如can总线,输入控制器部件102也需要通过输入输出管脚阵列部件101发送相应信号到总线,输出控制器部件103也需要通过输入输出管脚阵列部件101了解总线相应信号的情况。读写接口控制器部件106是给类似于中央处理器(cpu)等外设使用者的访问通道。中央处理器通过这个通道可以读写输入缓存部件104和输出缓存部件105以及各个部件的配置寄存器和状态寄存器以及各种读写指针。

16.该通信接口外设在同一时间内只实现一个通信协议,输入缓存部件104和输出缓存部件105的存储空间都是被不同通信协议分时共享的。例如在某一时间段该接口作为串口uart使用时,这些缓存就是串口uart的输入输出缓存,当另一个时间段,该接口作为spi使用时,这些缓存就是spi的输入输出缓存,不同协议分时共享缓存单元,而不是每种协议都使用独立缓存,可以节省缓存容量。

17.此外,不同于一般接口外设的先入先出队列(fifo)形式的缓存,该接口外设的缓存访问形式是按照地址访问,对应不同地址,访问不同缓存单元,但是同一个缓存单元不一定只有一个地址可以访问,同一个缓存单元可以被分配多个不同地址。例如地址0的低位可以访问缓存单元0,地址1的低位可以访问缓存单元1,地址2的低位可以访问缓存单元2,地址3的低位可以访问缓存单元3,但是地址4的低位也可以访问缓存单元0,地址4的高位也可以访问缓存单元1,这样对于地址4,只要要一次访问就可以同时访问缓存单元0和缓存单元1。而对于地址0则可以只访问缓存单元0而不影响其他缓存单元数据。这样通过不同地址的访问,可以兼具效率与灵活性。

18.对于输出控制器部件103,其内部有2个缓存指针,一个对应于外设使用者写入的缓存单元位置的写指针,一个对应已经发送的单元位置的读指针,通过对比这两个指针,输出控制器部件103可以知道其是否有数据需要发送,这两个指针的数值都可以被外设使用者读取或更新,读指针的更新或者自增减一般根据具体通信协议按照发送进度更新,也可以由外设使用者直接指定。写指针则可根据写入的数据量或者写入地址自动更新,也可以由外设使用者直接指定。

19.对于输入控制器部件102,其内部有1个对应已经接收的数据的缓存单元位置的写指针,该写指针的更新或者自增减一般根据具体通信协议按照接收进度更新但也可以被外设使用者直接指定。外设使用者自己维护读指针,这个读指针可以在输入控制器部件102内部也可以在输入控制器部件102外部,甚至整个外设的外部,通过对比这两个指针,外设使用者可以知道哪里有数据需要读取,并按需读取数据,由于是按地址读取,不是先入先出(fifo)读取,所以同一个缓存数据可以多次读取。

20.对于某些通信协议,例如usb或者can总线,总线数据需要有校验值(例如crc校验)。该通信接口外设可以内建校验值计算单元,自动计算发送数据的校验值并自动填充到发送数据流的合适位置,以降低外设使用者的工作量。但是外设使用者也可以自己计算校验值并命令输出控制器部件103直接原样发送。同理对于接收数据流,输入控制器部件102可以自动计算校验值并自动比较接收的校验值是否相同然后供外设使用者直接读取比较结果,也可以将自动计算的校验值和接收的校验值直接提供给外设使用者读取。外设也可

以直接把收到的原始数据流原样存入缓存,供外设使用者直接读取。

21.针对第一实施例,举例说明串口usart工作方式如下:

22.处理器通过读写接口控制器部件106,写入控制字,将该通信接口外设设置为uart模式,还通过写入控制字配置输入输出管脚阵列部件101使uart信号线txd为io1、rxd为io2。处理器通过读写接口控制器部件106,使用地址0写入发送数据到发送缓存单元0,输出控制器部件103内部的发送写指针加1,通过地址1写入发送数据到发送缓存单元1,输出控制器部件103内部的发送写指针再加1,同时输出控制器部件103内部的发送读指针与发送写指针的差距被输出控制器部件103发现,输出控制器部件103内部开始将缓存数据按照uart格式发送至输入输出管脚阵列部件101,输入输出管脚阵列部件101将数据发送至io1,输出控制器部件103更新发送写指针,直至发送读写指针相同。同时,输入输出管脚阵列部件101将io2上的rxd信号送给输入控制器部件102,输入控制器部件102按照uart格式写入接收数据到接收缓存0,处理器通过读写接口控制器部件106,读取输入控制器部件102的写指针,通过对比接收写指针和处理器自身保存的接收读指针,处理器发现有数据需要读取,根据读指针指示,处理器读取地址0获得接收缓存0的数据,然后更新自身保存的接收读指针。

23.针对第一实施例,举例说明spi工作方式如下:

24.处理器通过读写接口控制器部件106,写入控制字,将该通信接口外设设置为spi模式,还通过写入控制字配置输入输出管脚阵列部件101使spi信号线cs的管脚为io3,sclk的管脚为io1,miso的管脚为io2,mosi的管脚为io4。处理器通过读写接口控制器部件106,使用地址4写入发送数据到发送缓存单元0和缓存单元1,输出控制器部件103内部的发送写指针自行加2,同时输出控制器部件103内部的发送读指针与发送写指针的差距被输出控制器部件103发现,输出控制器部件103内部开始将缓存数据按照spi格式发送至输入输出管脚阵列部件101,然后更新发送写指针,直至发送读写指针相同。同时,输入输出管脚阵列部件101将io2管脚上的miso信号送给输入控制器部件102,输入控制器部件102按照spi格式写入接收数据到接收缓存0和接收缓存1,处理器通过读写接口控制器部件106,读取输入控制器部件102的写指针,通过对比接收写指针和处理器自身保存的接收读指针,处理器发现有数据需要读取,根据读指针指示,处理器读取地址4获得接收缓存0和接收缓存1的数据,然后更新自身保存的接收读指针。

25.针对第一实施例,举例说明can工作方式如下:

26.处理器通过读写接口控制器部件106,写入控制字,将该通信接口外设设置为can模式,还通过写入控制字配置输入输出管脚阵列部件101使can信号线txd为io3,rxd为io4。处理器通过读写接口控制器部件106,使用地址6写入发送数据到发送缓存单元0至缓存单元3,输出控制器部件103内部的发送写指针不自动更新,处理器通过读写接口控制器部件106,写入输出控制器部件103内部的发送读指针为0,写入输出控制器部件103内部的发送写指针为4,写入输入控制器部件102内部的接收写指针为0,写入输入控制器部件102内部的接收读指针为0。同时输出控制器部件103内部的发送读指针与发送写指针的差距被输出控制器部件103发现,输出控制器部件103内部开始将缓存数据按照can格式发送至输入输出管脚阵列部件101,然后更新发送写指针,注意,输出控制器部件103不自动计算crc校验值,只发送缓存的数据,因为数据已经包含crc在内全部报文数据,直至发送读写指针相同。

输入输出管脚阵列部件101将数据发送至配置好的具体管脚上。处理器可以实时读取输出控制器部件103内部的发送写指针,了解发送缓存使用状态从而继续写入发送数据而不造成发送缓存溢出或读空。同时,输入输出管脚阵列部件101将io4上的rxd信号送给输入控制器部件102,输入控制器部件102按照can格式写入接收数据到接收缓存0和接收缓存1,处理器通过读写接口控制器部件106,读取输入控制器部件102的写指针和读指针,通过对比接收写指针和读指针,处理器发现有数据需要读取,根据读指针指示,处理器读取地址4获得接收缓存0和接收缓存1的数据,然后更新接收读指针。最后处理器通过读写接口控制器部件106,读取接收数据的crc校验值与输入控制器部件102内部计算的crc校验值,或者直接读取接收的crc校验值与输入控制器部件102内部计算的crc校验值是否相同的标志位值。如果在接收数据过程中,输入控制器部件102发现接收数据不符合can格式,也可以通过输入输出管脚阵列部件101发送错误帧打断can通信,这个过程可以无需处理干预自动完成,也可以在处理器指示下完成。输出控制器部件103在发送数据时也需要观察接收的数据以便随时停止或发送错误帧等协议要求的行为。

27.针对第一实施例,举例说明usb工作方式如下:

28.处理器通过读写接口控制器部件106,写入控制字,将该通信接口外设设置为usb模式,还通过写入控制字配置输入输出管脚阵列部件101使usb信号线dp为io1,dn为io3。处理器通过读写接口控制器部件106,使用地址6写入发送数据到发送缓存单元0至缓存单元3,输出控制器部件103内部的发送写指针不自动更新,处理器通过读写接口控制器部件106,写入输出控制器部件103内部的发送读指针为0,写入输出控制器部件103内部的发送写指针为4,写入输入控制器部件102内部的接收写指针为0。同时输出控制器部件103内部的发送读指针与发送写指针的差距被输出控制器部件103发现,输出控制器部件103内部开始将缓存数据按照usb格式发送至输入输出管脚阵列部件101,然后更新发送写指针,同时输出控制器部件103会自动计算并填充crc校验值。输入输出管脚阵列部件101将数据发送至配置好的具体管脚上。同时,输入输出管脚阵列部件101将接收信号送给输入控制器部件102,输入控制器部件102按照usb格式写入接收数据到接收缓存0和接收缓存1,处理器通过读写接口控制器部件106,读取输入控制器部件102的写指针,通过对比接收写指针和处理器自身保存的接收读指针,处理器发现有数据需要读取,根据读指针指示,处理器读取地址4获得接收缓存0和接收缓存1的数据,然后更新接收读指针。最后处理器通过读写接口控制器部件106,读取接收数据的crc校验值与输入控制器部件102内部计算的crc校验值,或者直接读取接收的crc校验值与输入控制器部件102内部计算的crc校验值是否相同的标志位值,判断数据是否正确。

29.对所公开实施方式的先前的说明以使得任何所属技术领域的专业人员可以实施或者使用本发明。对本领域的技术人员而言可以很容易的对这些实施方式进行各种修改,并且在不脱离本发明的精神上、或者范围的情况下可以将在此定义的通用原理应用于其他实施方式。因此,并非意在将本发明限于在此显示的实施方式,而是应当同符合在此公开的原理和非常规设计的最宽范围相一致。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。