技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:提供半导体衬底,所述半导体衬底包括第一区域,所述第一区域的半导体衬底表面形成有若干依次堆叠的牺牲层和沟道层,所述若干依次堆叠的牺牲层和沟道层表面形成有伪栅极结构,其中,所述牺牲层侧壁形成有第二侧墙;在所述第一区域上形成第一掩膜层;刻蚀所述第一掩膜层暴露所述第二侧墙和沟道层第一侧的半导体衬底以及侧壁;在所述第二侧墙和沟道层第一侧的半导体衬底以及侧壁外延生长形成源极;在所述第一区域上形成第二掩膜层;刻蚀所述第二掩膜层和所述第一掩膜层暴露所述第二侧墙和沟道层第二侧的半导体衬底以及侧壁;在所述第二侧墙和沟道层第二侧的半导体衬底以及侧壁外延生长形成漏极,其中,所述源极和所述漏极具有相反的掺杂类型。2.如权利要求1所述半导体结构的形成方法,其特征在于,所述半导体衬底还包括第二区域,所述第二区域的半导体衬底表面形成有若干依次堆叠的牺牲层和沟道层,所述若干依次堆叠的牺牲层和沟道层表面形成有伪栅极结构,其中,所述牺牲层侧壁形成有第二侧墙。3.如权利要求2所述半导体结构的形成方法,其特征在于,在所述第一区域上形成第一掩膜层以及在所述第一区域上形成第二掩膜层时,在所述第二区域上也分别形成第一掩膜层以及第二掩膜层。4.如权利要求1所述半导体结构的形成方法,其特征在于,所述牺牲层的材料包括硅锗,所述沟道层的材料包括硅。5.如权利要求1所述半导体结构的形成方法,其特征在于,形成所述若干依次堆叠的牺牲层和沟道层的方法包括外延生长工艺。6.如权利要求1所述半导体结构的形成方法,其特征在于,所述伪栅极结构包括伪栅极和位于所述伪栅极侧壁的第一侧墙。7.一种半导体结构,其特征在于,包括:半导体衬底,所述半导体衬底包括第一区域,所述第一区域的半导体衬底表面形成有若干依次堆叠的牺牲层和沟道层,所述若干依次堆叠的牺牲层和沟道层表面形成有伪栅极结构,其中,所述牺牲层侧壁形成有第二侧墙;源极和漏极,分别位于所述第二侧墙和沟道层侧壁,其中,所述源极和所述漏极具有相反的掺杂类型。8.如权利要求7所述的半导体结构,其特征在于,所述半导体衬底还包括第二区域,所述第二区域的半导体衬底表面形成有若干依次堆叠的牺牲层和沟道层,所述若干依次堆叠的牺牲层和沟道层表面形成有伪栅极结构,其中,所述牺牲层侧壁形成有第二侧墙。9.如权利要求8所述的半导体结构,其特征在于,所述第二区域的半导体衬底表面还形成有源极和漏极,分别位于所述第二侧墙和沟道层侧壁,其中,所述源极和所述漏极具有相同的掺杂类型。10.如权利要求7所述的半导体结构,其特征在于,所述牺牲层的材料包括硅锗,所述沟道层的材料包括硅。

11.如权利要求7所述的半导体结构,其特征在于,所述伪栅极结构包括伪栅极和位于所述伪栅极侧壁的第一侧墙。12.一种半导体结构的形成方法,其特征在于,包括:提供半导体衬底,所述半导体衬底包括第一区域,所述第一区域的半导体衬底表面形成有伪栅极结构;在所述第一区域上形成第一掩膜层;刻蚀所述第一掩膜层暴露所述伪栅极结构第一侧的半导体衬底以及侧壁;刻蚀所述伪栅极结构第一侧的半导体衬底形成第一开口;在所述第一开口中外延生长形成源极;在所述第一区域上形成第二掩膜层;刻蚀所述第二掩膜层和所述第一掩膜层暴露所述伪栅极结构第二侧的半导体衬底以及侧壁;刻蚀所述伪栅极结构第二侧的半导体衬底形成第二开口;在所述第二开口中外延生长形成漏极,其中,所述源极和所述漏极具有相反的掺杂类型。13.如权利要求12所述半导体结构的形成方法,其特征在于,所述半导体衬底还包括第二区域,所述第二区域的半导体衬底表面形成有伪栅极结构。14.如权利要求13所述半导体结构的形成方法,其特征在于,在所述第一区域上形成第一掩膜层以及在所述第一区域上形成第二掩膜层时,在所述第二区域上也分别形成第一掩膜层以及第二掩膜层。15.如权利要求13所述半导体结构的形成方法,其特征在于,所述半导体结构还包括隔离结构,位于所述第一区域和所述第二区域之间的半导体衬底中,隔离所述第一区域和所述第二区域。16.如权利要求12所述半导体结构的形成方法,其特征在于,所述伪栅极结构包括伪栅极和位于所述伪栅极侧壁的第一侧墙。

技术总结

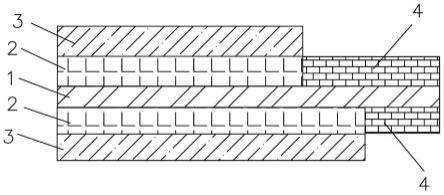

本申请提供半导体结构及其形成方法,所述半导体结构包括:半导体衬底,所述半导体衬底包括第一区域,所述第一区域的半导体衬底表面形成有若干依次堆叠的牺牲层和沟道层,所述若干依次堆叠的牺牲层和沟道层表面形成有伪栅极结构,其中,所述牺牲层侧壁形成有第二侧墙;源极和漏极,分别位于所述第二侧墙和沟道层侧壁,其中,所述源极和所述漏极具有相反的掺杂类型。本申请提供一种半导体结构及其形成方法,一方面将TFET器件结构特点与GAA结构特点结合,可以实现TFET器件尺寸的进一步缩小,降低静态功耗,另一方面将外延生长形成源漏极的方法用于平面CMOS器件中,可以解决TFET器件的多晶硅栅极形成高阻的问题。多晶硅栅极形成高阻的问题。多晶硅栅极形成高阻的问题。

技术研发人员:武咏琴 卜伟海

受保护的技术使用者:北方集成电路技术创新中心(北京)有限公司

技术研发日:2021.06.10

技术公布日:2022/12/12

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。