技术特征:

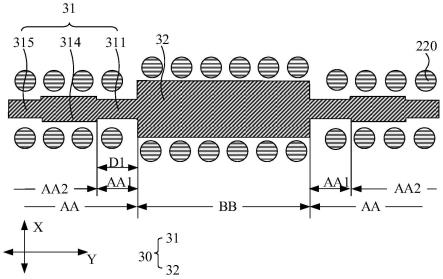

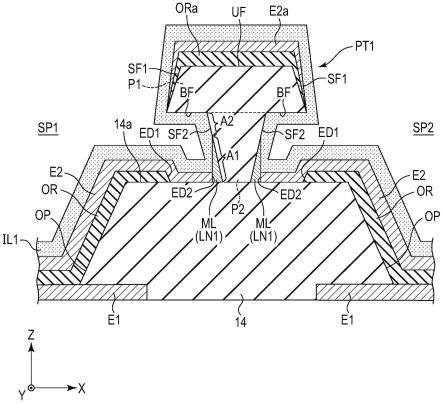

1.一种半导体结构,其特征在于,包括:堆叠结构,所述堆叠结构包括交替层叠设置的栅极层和介质层;所述堆叠结构包括第一区以及与所述第一区相邻接的第二区;栅线缝隙结构,由所述第一区延伸至所述第二区,且贯穿所述堆叠结构;所述栅线缝隙结构包括第一分隔结构和第二分隔结构;所述第一分隔结构位于所述第一区,所述第二分隔结构位于所述第二区;所述第一分隔结构包括第一部分,所述第一部分与所述第二分隔结构相连;所述第二分隔结构沿第一方向的宽度大于所述第一部分沿所述第一方向的宽度;所述第一方向与所述栅线缝隙结构的延伸方向垂直,且与所述栅极层平行。2.根据权利要求1所述的半导体结构,其特征在于,所述第二分隔结构包括第二部分;所述第二部分包括靠近所述第一部分的第一端和远离所述第一部分的第二端,所述第二端的沿第一方向的宽度大于所述第一端的沿所述第一方向的宽度,所述第一端的沿所述第一方向的宽度大于或等于所述第一部分的沿所述第一方向的宽度。3.根据权利要求2所述的半导体结构,其特征在于,由所述第一端指向所述第二端的方向为第二方向;所述第二部分的沿所述第一方向的宽度沿所述第二方向逐渐增大。4.根据权利要求2所述的半导体结构,其特征在于,由所述第一端指向所述第二端的方向为第二方向;所述第二部分的沿所述第二方向的长度的小于或者等于25nm;和/或,所述第二部分的沿所述第一方向的最大宽度的取值范围为:250nm-700nm。5.根据权利要求2所述的半导体结构,其特征在于,所述第二分隔结构还包括第三部分;所述第三部分与所述第二部分相连;所述第三部分的沿所述第一方向的宽度均大于或等于所述第二端的沿所述第一方向的宽度。6.根据权利要求2-4任一项所述的半导体结构,其特征在于,所述第一分隔结构还包括第四部分和第五部分;所述第四部分与所述第一部分相连;所述第四部分的沿所述第一方向的宽度大于所述第一部分的沿所述第一方向的宽度;所述第五部分与所述第四部分远离所述第一部分的一端相连;所述第五部分的沿所述第一方向的宽度小于所述第四部分的沿所述第一方向的宽度。7.根据权利要求2-4任一项所述的半导体结构,其特征在于,还包括:多个沟道结构,贯穿所述堆叠结构;所述多个沟道结构中包括沿所述栅线缝隙结构的边缘设置的第一沟道结构,所述第一沟道结构与所述栅线缝隙结构之间的距离的取值范围为50nm-200nm。8.一种半导体结构的制备方法,其特征在于,形成叠层结构,所述叠层结构包括交替层叠设置的牺牲层和介质层;所述叠层结构包括第一区以及与所述第一区相邻接的第二区;形成栅线隔槽,由所述第一区延伸至所述第二区,且贯穿所述叠层结构;经由所述栅线隔槽,将所述牺牲层替换为栅极层,以形成堆叠结构;

填充所述栅线隔槽,以形成栅线缝隙结构,所述栅线缝隙结构包括第一分隔结构和第二分隔结构;所述第一分隔结构位于所述第一区,所述第一分隔结构包括第一部分;所述第二分隔结构沿第一方向的宽度大于所述第一部分沿所述第一方向的宽度;所述第一方向与所述栅线缝隙结构的延伸方向垂直,且与所述栅极层平行。9.根据权利要求8所述的制备方法,其特征在于,所述栅线隔槽包括位于所述第一区的第一分隔槽和位于所述第二区的第二分隔槽;所述形成堆叠结构,包括:形成牺牲结构,所述牺牲结构位于所述第一分隔槽内;经由所述第二分隔槽,去除位于所述第二区的部分所述牺牲层,以形成第二间隙;形成阻隔结构,位于所述第二分隔槽和所述第二间隙内;去除所述牺牲结构;经由所述第一分隔槽,去除位于所述第一区的所述牺牲层,以形成第一间隙;去除所述阻隔结构;形成栅极层,所述栅极层位于所述第一间隙和所述第二间隙,所述栅极层和所述介质层共同构成所述堆叠结构。10.根据权利要求9所述的制备方法,其特征在于,所述第一分隔槽包括第一槽部和第二槽部,所述第二槽部相对于所述第一槽部远离槽底;所述形成牺牲结构,包括:形成第一牺牲部,所述第一牺牲部填充于所述第一槽部;形成阻挡层,所述阻挡层包括第一阻挡层和第二阻挡层;所述第一阻挡层覆盖所述第一牺牲部以及所述第二槽部的侧壁;所述第二阻挡层覆盖所述第一牺牲部中靠近所述第二分隔槽的侧面;形成第二牺牲部,所述第二牺牲部填充于所述第二槽部;其中,所述第一牺牲部、所述第一阻挡层以及所述第二牺牲部共同构成所述牺牲结构。11.根据权利要求10所述的制备方法,其特征在于,所述阻挡层还包括第三阻挡层,所述第三阻挡层覆盖所述第二分隔槽的侧壁。12.根据权利要求10所述的制备方法,其特征在于,所述形成第一牺牲部,包括:在所述第一分隔槽和所述第二分隔槽内填充第一介质材料;所述第一分隔槽包括第一槽段、第二槽段以及第三槽段,所述第二槽段位于所述第一槽段与所述第三槽段之间,所述第一槽段相对于所述第三槽段更靠近所述第二分隔槽;所述第一槽段和所述第三槽段中,至少所述第一槽段内的所述第一介质材料填充为实心结构;去除所述第二分隔槽的内壁上的所述第一介质材料以及所述第一分隔槽内的部分所述第一介质材料,保留位于所述第一槽部内的所述第一介质材料,以形成所述第一牺牲部。13.根据权利要求11所述的制备方法,其特征在于,所述经由所述第二分隔槽,去除位于所述第二区的部分所述牺牲层的同时,还包括:去除所述第三阻挡层。14.根据权利要求9-13任一项所述的制备方法,其特征在于,还包括:形成接触孔,所述接触孔位于所述第二区;所述形成栅极层的同时,还包括:在所述接触孔内形成栅导电层。15.一种三维存储器,其特征在于,包括:

半导体结构,所述半导体结构为如权利要求1-7任一项所述的半导体结构;外围器件,与所述半导体结构电连接。16.一种存储系统,其特征在于,包括:三维存储器,所述三维存储器为如权利要求15所述的三维存储器;控制器,耦合至所述三维存储器,以控制所述三维存储器存储数据。17.一种电子设备,其特征在于,包括如权利要求16所述的存储系统。

技术总结

本公开提供了一种半导体结构及其制备方法、三维存储器,涉及半导体芯片技术领域,旨在解决相关技术中三维存储器存储容量较小的问题。半导体结构包括堆叠结构和栅线缝隙结构,栅线缝隙结构包括第一分隔结构和第二分隔结构;第一分隔结构包括第一部分,第一部分与第二分隔结构相连;第二分隔结构沿第一方向的宽度大于第一部分沿第一方向的宽度。在去除第二分隔结构周围的牺牲层时,有利于减少由第二区流向第一区的刻蚀液,进而避免刻蚀到位于第一区的沟道结构处,减小过渡区的延伸长度,提高半导体结构的存储容量。上述半导体结构应用于三维存储器中,以实现数据的读取和写入操作。以实现数据的读取和写入操作。以实现数据的读取和写入操作。

技术研发人员:张坤 吴双双 吴林春 周文犀 张中 谢景涛 韩玉辉 王迪 顾妍

受保护的技术使用者:长江存储科技有限责任公司

技术研发日:2022.09.05

技术公布日:2022/12/5

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。