5g双载波基站

技术领域

1.本实用新型涉及通信基站技术领域,尤其涉及5g双载波基站。

背景技术:

2.目前5g lte基站主要是移动通信供应商为移动通信部署的基站,承载手机等各种智能设备进行通信。这种基站通常为制式基站,根据移动供应商的要求设计相应的频带,输出固定的功率。

3.为了满足更多用户的接入,通常设置大型基站,这种大型基站的体积大,通常遵循同一的标准,无法按照具体需求进行配置。随着用户数量和种类的增多,用户的需求也在不断的变化以及增加,比如需要基站小型化的同时实现双载波,这都是传统大型基站无法满足的。

技术实现要素:

4.本实用新型提供了一种5g双载波基站,以实现基站基站小型化的同时实现双载波。

5.本实用新型提供了一种5g双载波基站,其特征在于,包括:网络处理单元、基带处理单元、射频单元、电源管理单元及时钟管理单元;

6.所述电源管理单元分别与所述网络处理单元、所述基带处理单元、所述射频单元相连接,用于为所述网络处理单元、所述基带处理单元、所述射频单元提供工作电源;

7.所述网络处理单元与所述基带处理单元相连接,所述基带处理单元为双载波基带处理单元,用于根据网络处理单元的网络通信信息实现5g和lte的双频段基带信号处理;

8.所述基带处理单元与所述射频单元相连接,所述射频单元为双载波设置,用于匹配所述双频段基带信号进行射频信号的处理;

9.所述时钟管理单元分别与所述网络处理单元和所述基带处理单元相连接,用于为所述网络处理单元和所述基带处理单元提供时钟信号。

10.可选的,所述网络处理单元包括lx2080处理器,所述lx2080处理器设置有rgps接口、uart1接口、rgmii接口和serdes1接口;

11.其中,lx2080处理器通过所述rgps接口连接所述时钟管理单元、通过所述rgmii接口连接以太网phy芯片、通过所述serdes1接口连接所述基带处理单元;

12.所述uart1接口为串口调试接口。

13.可选的,所述网络处理单元与所述基带处理单元之间采用两组pcie3协议互联。

14.可选的,所述基带处理单元包括fsm200系列处理器。

15.可选的,所述fsm200系列处理器与所述射频单元之间采用qlink1总线互联。

16.可选的,所述电源管理单元至少设置有第一电源芯片和第二电源芯片;

17.所述第一电源芯片用于为所述网络处理单元提供工作电源;所述第二电源芯片用于为所述射频单元提供工作单元。

18.可选的,所述第一电源芯片为pmf1010h电源芯片;

19.所述pmf1010h电源芯片为pmx65、pmk65和pm8005芯片提供电源,所述pmx65、pmk65和pm8005芯片为所述网络处理单元提供工作电源。

20.可选的,所述第二电源芯片为pmf1010h电源芯片;

21.所述pmf1010h电源芯片为pmf2000芯片提供电源,所述pmf2000芯片为所述射频单元提供工作单元。

22.可选的,所述射频单元包括射频芯片和射频收发单元;

23.所述射频芯片为qtr145,用于实现对所述射频收发单元的射频信号收发控制。

24.可选的,所述射频单元的射频收发单元外接功放模块;所述功放模块用于实现多个预设等级功率的输出。

25.本实用新型实施例的技术方案,通过设置网络处理单元、基带处理单元、射频单元、电源管理单元及时钟管理单元这些必要的器件,实现对基站的体积进行减小,且将基带处理单元设置为双载波基带处理单元,为射频单元进行双载波设置,实现了双载波,取得了实现基站小型化的同时实现双载波的有益效果。

26.应当理解,本部分所描述的内容并非旨在标识本实用新型的实施例的关键或重要特征,也不用于限制本实用新型的范围。本实用新型的其它特征将通过以下的说明书而变得容易理解。

附图说明

27.为了更清楚地说明本实用新型实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

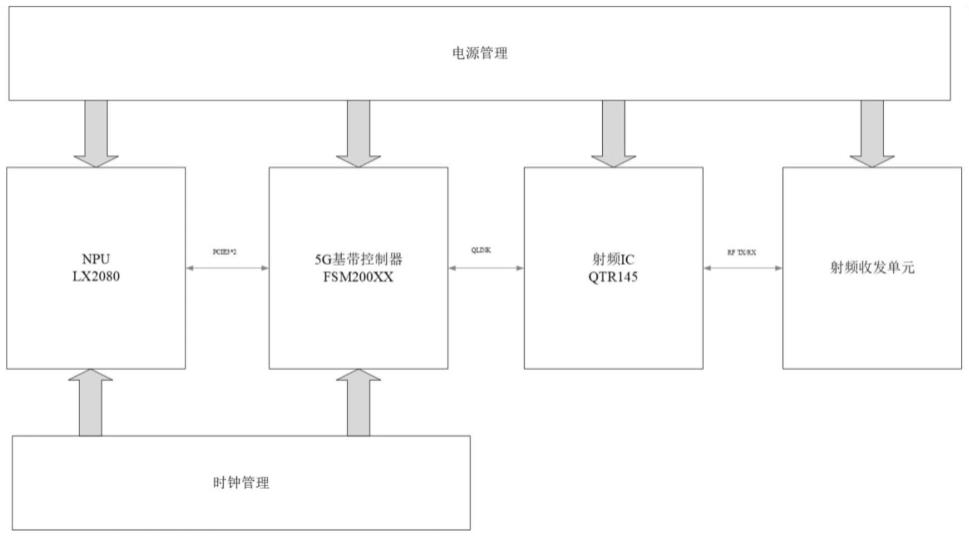

28.图1为本技术提供的5g双载波基站系统架构示意图;

29.图2为网络处理单元的lx2080处理器接线示意图;

30.图3为本技术的基带处理单元中fsm200系列处理器的接线示意图;

31.图4为本技术的时钟管理单元的结构示意图;

32.图5为本技术的射频收发单元及功放模块的结构示意图。

具体实施方式

33.为了使本技术领域的人员更好地理解本实用新型方案,下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分的实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本实用新型保护的范围。

34.需要说明的是,本实用新型的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本实用新型的实施例能够以除了在这里图示或描述的那些以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意

图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

35.请参阅图1,图1为本技术提供的5g双载波基站系统架构示意图。如图1所示,本技术的任一实施例提供的5g双载波基站可以包括:网络处理单元101、基带处理单元102、射频单元103、电源管理单元104及时钟管理单元105;

36.所述电源管理单元分别与所述网络处理单元、所述基带处理单元、所述射频单元相连接,用于为所述网络处理单元、所述基带处理单元、所述射频单元提供工作电源;

37.所述网络处理单元与所述基带处理单元相连接,所述基带处理单元为双载波基带处理单元,用于根据网络处理单元的网络通信信息实现5g和lte的双频段基带信号处理;

38.所述基带处理单元与所述射频单元相连接,所述射频单元为双载波设置,用于匹配所述双频段基带信号进行射频信号的处理;

39.所述时钟管理单元分别与所述网络处理单元和所述基带处理单元相连接,用于为所述网络处理单元和所述基带处理单元提供时钟信号。

40.本实用新型实施例的技术方案,通过设置网络处理单元、基带处理单元、射频单元、电源管理单元及时钟管理单元这些必要的器件,实现对基站的体积进行减小,且将基带处理单元设置为双载波基带处理单元,为射频单元进行双载波设置,实现了双载波,取得了实现基站小型化的同时实现双载波的有益效果。

41.其中,所述网络处理单元包括lx2080处理器,具体可以参阅图2,图2为网络处理单元的lx2080处理器接线示意图,如图2所示,所述lx2080处理器设置有rgps接口、uart1接口、rgmii接口和serdes1接口;

42.lx2080处理器通过所述rgps接口连接所述时钟管理单元、通过所述rgmii接口连接以太网phy芯片、通过所述serdes1接口连接所述基带处理单元;所述uart1接口为串口调试接口。

43.该网络处理单元中,以lx2080处理器为核心,配置512mbit容量的spiflash存储,配置4gb emmc nand flash,配置4gb ddr4内存。

44.通过rgps接口,输入1pps时钟和tod信号。tod信号给lx2080的uart2接口。lx2080的uart1接口作为串口调试接口。rgmii接口连接phy芯片,可选的88e1518,输出1g网口,用户调试。serdes1接口的lande0口连接phy芯片,可选的88x3310,输出10g光口,用于数据回传。serdes1接口的lande4-5口配合为pcie接口,用于连接fsm200xx处理器。

45.需要说明的是,对于图2中lx2080处理器其他引脚的连接较为常规,可以参考lx2080处理器的使用说明,此处不再赘述。

46.另外,所述网络处理单元与所述基带处理单元之间采用两组pcie3协议互联。同时,可以配置相应的pcie接口有关的gpio,如复位中断信号等。

47.在一个具体的实施方式中,所述基带处理单元包括fsm200系列处理器,后续实施以fsm20056处理器为例进行说明。具体可以参阅图3,图3为本技术的基带处理单元中fsm200系列处理器的接线示意图。

48.如图3所示,所述fsm200系列处理器与所述射频单元之间采用qlink1总线互联。fsm200系列处理器配置1gb的lpddr4内存,用于提高处理速率同时fsm200系列处理器的

gfrc和rffe引脚控制qtr145相关功能。

49.进一步地,所述电源管理单元至少设置有第一电源芯片和第二电源芯片;

50.所述第一电源芯片用于为所述网络处理单元提供工作电源;所述第二电源芯片用于为所述射频单元提供工作单元。

51.具体的,所述第一电源芯片为pmf1010h电源芯片;所述pmf1010h电源芯片为pmx65、pmk65和pm8005芯片提供电源,所述pmx65、pmk65和pm8005芯片为所述网络处理单元提供工作电源。

52.所述第二电源芯片为pmf1010h电源芯片;所述pmf1010h电源芯片为pmf2000芯片提供电源,所述pmf2000芯片为所述射频单元提供工作单元。

53.另外,时钟管理单元输入1pps信号和10mhz信号,输出:1)19.2mhz信号给fsm200xx,2)输出76.8mhz信号给pmx65、pmk65和pm8005单元。3)输出156.3mhz信号和pps信号给qtr145芯片。

54.需要说明的是,时钟管理单元可以参阅图4,图4为本技术的时钟管理单元的结构示意图,如图4所示,时钟管理单元中包括时钟芯片,时钟芯片可选的为si5348,该芯片输入25mhz和50mhz时钟频率,同时88x3310输出synce同步信号给si5348。

55.si5348输出125mhz、100mhz、156.25mhz时钟给lx2080,供该芯片各部分时钟运行。选用38.4mhz vctxco钟振,可选的vf901723,输出38.4mhz时钟给pmk8002和fpga。pmk8002输出19.2mhz、38.4mhz等时钟给pmx65和fsm200xx。si5348输出100mhz pcie时钟给fsm200系列处理器。

56.进一步地,所述射频单元包括射频芯片和射频收发单元;所述射频芯片为qtr145,用于实现对所述射频收发单元的射频信号收发控制。

57.为了提高输出能力,所述射频单元的射频收发单元外接功放模块;所述功放模块用于实现多个预设等级功率的输出。

58.具体可以参阅图5,图5为本技术的射频收发单元及功放模块的结构示意图。如图5所示,其设置有载波1和载波2的收发单元,另外,虚线框选的部分为功放模块。

59.上述具体实施方式,并不构成对本实用新型保护范围的限制。本领域技术人员应该明白的是,根据设计要求和其他因素,可以进行各种修改、组合、子组合和替代。任何在本实用新型的精神和原则之内所作的修改、等同替换和改进等,均应包含在本实用新型保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。