1.本发明涉及量子计算领域,特别是涉及一种正余弦信号发生器及量子计算机控制系统。

背景技术:

2.量子计算机控制系统主要作用是对量子计算机进行控制,更具体的,是对量子比特进行控制。对量子比特进行控制的本质是对量子比特施加各种控制信号,控制信号大多根据基础的正余弦信号生成。由于量子比特的频率比较高,因此控制信号需要有较高的频率,对应的正余弦信号也需要有较高的频率。

3.然而,正余弦信号一般采用nco(数控振荡器)产生,nco可在fpga等器件中实现。正余弦信号频率越高,需要的采样率更高,但是大部分fpga的最高工作频率有限,所以产生的正余弦信号的频率较低。为了提高正余弦信号的频率,现有的做法是通过多个fpga并行生成较低频率的正余弦信号,再将这些正余弦信号的频率进行综合。但这样做需要多个fpga,资源消耗和成本大幅增加。

技术实现要素:

4.本发明的目的是提供一种正余弦信号发生器、存储器及量子计算机控制系统,以解决现有技术中fpga内生成的正余弦信号频率较低的问题,能够在fpga内生成较高频率的正余弦信号。

5.为解决上述技术问题,本发明提供一种正余弦信号发生器,用于fpga,包括地址获取模块和存储有至少四分之一周期的三角函数值的存储器,一个周期的三角函数值的数量为第一数量,所述存储器的数量为第二数量;

6.所述地址获取模块用于在工作时钟作用下依次获取多路查表地址,并分别送入第二数量的存储器,同一时刻相邻两路的查表地址相差预设相位增量,同一路相邻两个查表地址相差预设相位增量的第二数量倍数;

7.所述存储器被配置为每送入一个查表地址时,输出当前正弦值和当前余弦值,分别形成预设频率的正弦信号和余弦信号;

8.其中,所述预设相位增量根据所述预设频率、所述第一数量、所述第二数量和所述工作时钟的频率确定。

9.优选的,所述存储器存储的三角函数值为至少四分之一周期的正弦值、至少四分之一周期的余弦值或者至少四分之一周期的正弦值和余弦值。

10.优选的,所述存储器被配置为每送入一个查表地址时,检查当前查表地址是否存储有对应的正弦值或余弦值,在存储有对应的正弦值或余弦值时,输出存储的当前正弦值和当前余弦值,分别形成预设频率的正弦信号和余弦信号,以及在没有存储有对应的正弦值或余弦值时,根据正弦值或余弦值的周期性计算出对应的正弦值或余弦值,输出计算的当前正弦值和当前余弦值,分别形成预设频率的正弦信号和余弦信号。

11.优选的,所述存储器提供查找表,所述查找表存储有四分之一周期的正弦值,所述查找表的查表地址位数为第一位数a,其中,2a与第一数量相等。

12.优选的,所述预设相位增量为:

[0013][0014]

其中,n表示所述第一数量,c表示所述第二数量,f

out

表示所述预设频率,fs表示所述工作时钟的频率,round()表示取整函数。

[0015]

优选的,所述正弦信号为:

[0016][0017]

所述余弦信号为:

[0018][0019]

其中,n*pinc表示送入存储器的查表地址的值,n的取值范围为[0,2a-1],a表示幅值,表示初相,b表示偏距。

[0020]

优选的,所述存储器输出的当前正弦值为:

[0021][0022]

所述存储器输出的当前余弦值为:

[0023][0024]

其中,m表示查找表的查表地址的值,取值范围为[0,2a-1]。

[0025]

优选的,所述正弦信号和所述余弦信号的幅值、初相和偏距相同。

[0026]

优选的,所述地址获取模块包括频率字单元和与第二数量的存储器一一对应的相位累加器;

[0027]

所述频率字单元用于获取多路频率字,并分别送入第二数量的相位累加器,所述频率字为预设相位增量的第二数量倍数;

[0028]

所述相位累加器用于在所述工作时钟作用下以所述频率字为步进不断累加得到查表地址,并送入对应的存储器,其中,同一时刻相邻两个相位累加器得到的查表地址相差预设相位增量。

[0029]

为解决上述技术问题,本发明还提供一种量子计算机控制系统,包括前述任一种所述的正余弦信号发生器。

[0030]

区别于现有技术的情况,本发明提供的正余弦信号发生器通过设置第二数量的存储器,每一存储器存储有至少四分之一周期的三角函数值,存储器被配置为每送入一个查表地址时,输出当前正弦值和当前余弦值,分别形成预设频率的正弦信号和余弦信号,而同一时刻相邻两路的查表地址相差预设相位增量,同一路相邻两个查表地址相差预设相位增量的第二数量倍数,由于工作时钟的频率与第二数量的乘积等效为采样频率,根据奈奎斯特采样定律,理论上预设频率可以达到采样频率的一半,从而能够在fpga内生成较高频率的正余弦信号,可以降低资源消耗和成本。

[0031]

本发明提供的量子计算机控制系统,与正余弦信号发生器属于同一发明构思,因此具有相同的有益效果,在此不再赘述。

附图说明

[0032]

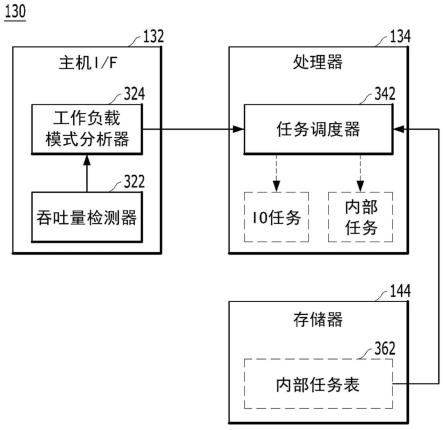

图1为本发明第一实施例提供的正余弦信号发生器的结构示意图。

[0033]

图2为第一实施例中正余弦信号发生器的存储器提供的查找表的数据结构示意图。

[0034]

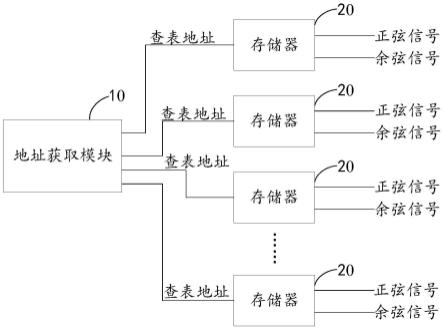

图3为本发明第二实施例提供的正余弦信号发生器的地址获取模块的结构示意图。

具体实施方式

[0035]

下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

[0036]

在本发明的描述中,需要理解的是,术语“中心”、“上”、“下”、“左”、“右”等指示的方位或者位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

[0037]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

[0038]

请参考图1,本发明第一实施例提供了一种正余弦信号发生器,该正余弦信号发生器用于fpga,能够在fpga内产生较高频率的正余弦信号。该正余弦信号发生器包括地址获取模块10和存储有至少四分之一周期的三角函数值的存储器20,一个周期的三角函数值的数量为第一数量,存储器20的数量为第二数量。

[0039]

地址获取模块10用于在工作时钟作用下依次获取多路查表地址,并分别送入第二数量的存储器20,同一时刻相邻两路的查表地址相差预设相位增量,同一路相邻两个查表地址相差预设相位增量的第二数量倍数。如果预设相位增量采用pinc表示,第二数量采用c表示,同一时刻相邻两路的查表地址相差pinc,第一次获取的查表地址中最小的优选为0,其他几路的查表地址则依次为1*pinc、2*pinc、3*pinc、4*pinc、

……

,同一路相邻两个查表地址相差c*pinc,例如第一路的查表地址依次为0、c*pinc、2c*pinc、3c*pinc、

……

。

[0040]

存储器20被配置为每送入一个查表地址时,输出当前正弦值和当前余弦值,分别形成预设频率的正弦信号和余弦信号。其中,预设相位增量根据预设频率、第一数量、第二数量和工作时钟的频率确定。

[0041]

其中,存储器20存储的每一个三角函数值对应的查表地址从0开始以pinc递增。对于某一个存储器20而言,例如第一路查表地址对应的存储器20,它收到的查表地址依次为0、c*pinc、2c*pinc、3c*pinc、

……

,那么最终输出的正弦信号和余弦信号的相位以c*pinc递增,相邻两个存储器20输出的正弦信号和余弦信号的相位相差pinc。

[0042]

预设频率、第一数量、第二数量和工作时钟的频率根据实际需要设置。第一数量是一个周期的三角函数值的总数,存储器20至少需要存储第一数量的三角函数值的前四分之

一部分。工作时钟的频率应当不超过fpga的最高工作频率。工作时钟的频率和第二数量的值与采样率有关,两者的乘积等效为采样率,例如采样率为1.6ghz时,工作时钟的频率设为200mhz,那么第二数量就为8,也就是需要8个存储器20。采样率是由量子比特的控制需求决定的。根据奈奎斯特采样定律,预设频率与采样频率之比最大为1:2,也就是说,预设频率理论上可以达到800mhz,从而在fpga内实现了较高频率的正余弦信号。

[0043]

由于三角函数具有周期性,因此,只要知道前四分之一周期的三角函数值,就可以根据周期性计算出后四分之三周期的三角函数值。在本实施例中,存储器20存储的三角函数值为至少四分之一周期的正弦值、至少四分之一周期的余弦值或者至少四分之一周期的正弦值和余弦值。

[0044]

进一步地,存储器20被配置为每送入一个查表地址时,检查当前查表地址是否存储有对应的正弦值或余弦值,在存储有对应的正弦值或余弦值时,输出存储的当前正弦值和当前余弦值,分别形成预设频率的正弦信号和余弦信号,以及在没有存储有对应的正弦值或余弦值时,根据正弦值或余弦值的周期性计算出对应的正弦值或余弦值,输出计算的当前正弦值和当前余弦值,分别形成预设频率的正弦信号和余弦信号。

[0045]

如果存储器20存储有一个周期的正弦值以及一个周期的余弦值,正弦值和余弦值的数量均为第一数量,那么每一个查表地址都存储有对应的正弦值或余弦值,可以直接输出存储的当前正弦值和当前余弦值。如果存储器20只存储有不足一个周期的正弦值和/或不足一个周期的余弦值,那么存在某些查表地址没有对应的正弦值或余弦值的情形,这时可以根据正弦值或余弦值的周期性结合已存储的正弦值和/或余弦值计算出这些查表地址对应的正弦值和余弦值。

[0046]

请参考图2,存储器20提供查找表lut,查找表lut存储有四分之一周期的正弦值,查找表lut的查表地址位数为第一位数a,其中,2a与第一数量相等。只有前2a/4的查表地址分别对应的数据位存储有正弦值,其余的查表地址对应的数据位为空。

[0047]

在本实施例中,预设相位增量为:

[0048][0049]

其中,n表示第一数量,c表示第二数量,f

out

表示预设频率,fs表示工作时钟的频率,round()表示取整函数。

[0050]

进一步地,正弦信号为:

[0051][0052]

余弦信号为:

[0053][0054]

其中,n*pinc表示查表地址的值,n的取值范围为[0,2a-1],a表示幅值,表示初相,b表示偏距。

[0055]

存储器20输出的当前正弦值为:

[0056][0057]

存储器20输出的当前余弦值为:

[0058]

[0059]

其中,m表示查找表的查表地址的值,取值范围为[0,2a-1]。

[0060]

为了方便进行信号处理,在本实施例中,正弦信号和余弦信号的幅值、初相和偏距相同。为了方便理解,a取1,和b取0。

[0061]

从图2中可以看出,查找表lut前2a/4个数据位存储的正弦值依次为、sin(0*2π/n)、sin(1*2π/n)、sin(2*2π/n)、sin(3*2π/n)、

……

、其余数据位存储的数据为null,表示为空。可以看出,查找表lut中每一个存储的正弦值与查找表的查表地址有关,查表地址为m,则正弦值为sin(m*2π/n)。

[0062]

那么通过正弦函数的周期性,可以计算出其余查找地址对应的正弦值依次为

……

、sin[(n-2)*2π/n]、sin[(n-1)*2π/n]。

[0063]

同样的,余弦值也可以根据正弦值的周期性计算得到。

[0064]

假设第二数量为8,产生正弦信号的过程如下:

[0065]

送入第1个存储器20的查表地址依次为0*pinc、8*pinc、16*pinc、

……

,查找表lut中与0*pinc、8*pinc、16*pinc、

……

相等的查表地址依次为0*pinc、8*pinc、16*pinc、

……

,则第1个存储器20输出的正弦信号为sin(0*2π*pinc/n)、sin(8*2π*pinc/n)、sin(16*2π*pinc/n)、

……

;

[0066]

送入第2个存储器20的查表地址依次为1*pinc、9*pinc、17*pinc、

……

,查找表lut中与1*pinc、9*pinc、17*pinc、

……

相等的查表地址依次为1*pinc、9*pinc、17*pinc、

……

,则第2个存储器20输出的正弦信号为sin(1*2π*pinc/n)、sin(9*2π*pinc/n)、sin(17*2π*pinc/n)、

……

;

[0067]

送入第3个存储器20的查表地址依次为2*pinc、10*pinc、18*pinc、

……

,查找表lut中与2*pinc、10*pinc、18*pinc、

……

相等的查表地址依次为2*pinc、10*pinc、18*pinc、

……

,则第3个存储器20输出的正弦信号为sin(2*2π*pinc/n)、sin(10*2π*pinc/n)、sin(18*2π*pinc/n)、

……

;

[0068]

以此类推,送入第8个存储器20的查表地址依次为7*pinc、15*pinc、23*pinc、

……

,查找表lut中与7*pinc、15*pinc、23*pinc、

……

相等的查表地址依次为7*pinc、15*pinc、23*pinc、

……

,则第8个存储器20输出的正弦信号为sin(7*2π*pinc/n)、sin(15*2π*pinc/n)、sin(23*2π*pinc/n)、

……

。

[0069]

可以看出,8个存储器20每次输出的正弦信号的相位以pinc递增,同一个存储器20输出的正弦信号的相位以8*pinc递增。

[0070]

需要说明的是,如果送入存储器20的查表地址超过了查找表的查表地址的最大值,则存储器20在查找表lut中寻址的查表地址是送入存储器20的查表地址与第一数量n的求余结果。

[0071]

同样的,8个存储器20按照上述过程输出余弦信号。第1个存储器20输出的余弦信号为cos(0*2π*pinc/n)、cos(8*2π*pinc/n)、cos(16*2π*pinc/n)、

……

;第2个存储器20输出的余弦信号为cos(1*2π*pinc/n)、cos(9*2π*pinc/n)、cos(17*2π*pinc/n)、

……

;第3个

存储器20输出的余弦信号为cos(2*2π*pinc/n)、cos(10*2π*pinc/n)、cos(18*2π*pinc/n)、

……

;

……

;第8个存储器20输出的余弦信号为cos(7*2π*pinc/n)、cos(15*2π*pinc/n)、cos(23*2π*pinc/n)、

……

。

[0072]

请参考图3,本发明第二实施例提供了一种正余弦信号发生器,本实施例的正余弦信号发生器包括第一实施例的全部技术特征,在第一实施例的基础上,地址获取模块10包括频率字单元11和与第二数量的存储器20一一对应的相位累加器12。

[0073]

频率字单元11用于获取多路频率字,并分别送入第二数量的相位累加器12,频率字为预设相位增量的第二数量倍数。其中,频率字可以由外部输入,也可以由频率字单元11预先存储或自动生成。

[0074]

相位累加器12用于在工作时钟作用下以频率字为步进不断累加得到查表地址,并送入对应的存储器20,其中,同一时刻相邻两个相位累加器12得到的查表地址相差预设相位增量。其中,假设预设相位增量为pinc,第二数量为8,以第一个相位累加器12为例,相位累加器12收到第一个频率字时,输出一个查表地址0*pinc,然后将0*pinc与频率字累加得到第二个查表地址8*pinc,继续将8*pinc与频率字累加得到第三个查表地址16*pinc。也就是说,每一次相位累加器12输出的查表地址都会与频率字进行累加作为下一次输出的查表地址。

[0075]

通过上述方式,本发明实施例的正余弦信号发生器通过设置第二数量的存储器,每一存储器存储有至少四分之一周期的三角函数值,存储器被配置为每送入一个查表地址时,输出当前正弦值和当前余弦值,分别形成预设频率的正弦信号和余弦信号,而同一时刻相邻两路的查表地址相差预设相位增量,同一路相邻两个查表地址相差预设相位增量的第二数量倍数,由于工作时钟的频率与第二数量的乘积等效为采样频率,根据奈奎斯特采样定律,理论上预设频率可以达到采样频率的一半,从而能够在fpga内生成较高频率的正余弦信号,可以降低资源消耗和成本。

[0076]

本发明实施例还提供一种量子计算机控制系统,该量子计算机控制系统包括第一实施例或第二实施例的正余弦信号发生器。

[0077]

需要说明的是,前述实施例提供的正余弦发生器除了应用于量子计算机控制系统,也同样适用于任何具有正余弦信号生成需求的其他应用场景中,本发明对此不作限定。

[0078]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”或“具体示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例中以合适的方式结合。此外,本领域的技术人员可以将本说明书中描述的不同实施例或示例进行接合和组合。

[0079]

上述仅为本发明的优选实施例而已,并不对本发明起到任何限制作用。任何所属技术领域的技术人员,在不脱离本发明的技术方案的范围内,对本发明揭露的技术方案和技术内容做任何形式的等同替换或修改等变动,均属未脱离本发明的技术方案的内容,仍属于本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。