技术特征:

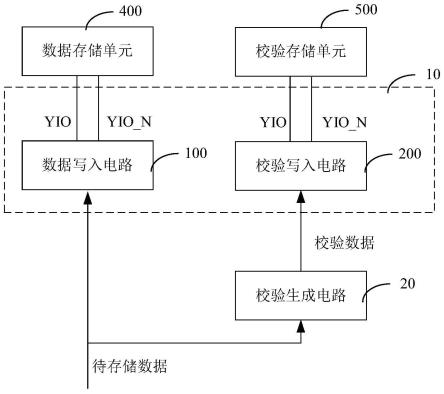

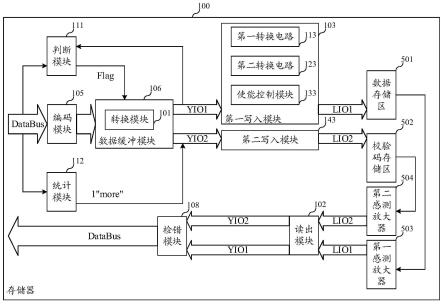

1.一种数据传输电路,其特征在于,包括:数据写入电路,用于传输待写入数据至全局数据线组,所述全局数据线组包括第一全局数据线和第二全局数据线,成对设置的所述第一全局数据线和所述第二全局数据线传输互为反相的数据,所述待存储数据通过所述全局数据线组传输至所述数据存储单元进行存储;校验写入电路,用于传输校验数据至校验存储单元连接的全局数据线组,以对所述校验数据进行存储,所述校验数据与所述待存储数据相对应;其中,所述数据写入电路和所述校验写入电路用于同步向对应的全局数据线组传输数据,且所述校验写入电路的驱动能力强于所述数据写入电路的驱动能力。2.根据权利要求1所述的数据传输电路,其特征在于,所述数据写入电路和所述校验写入电路的电路结构均为第一电路,但所述数据写入电路和校验写入电路中对应器件的电性参数不完全相同,以使所述校验写入电路的驱动能力强于所述数据写入电路的驱动能力。3.根据权利要求2所述的数据传输电路,其特征在于,所述第一电路包括:第一驱动模块,与所述第一全局数据线连接,用于响应于写使能信号,根据待写入数据信号生成并传输第一写入信号至所述第一全局数据线,所述第一写入信号的电平状态与所述待写入数据相同;第二驱动模块,与所述第二全局数据线连接,用于响应于写使能信号,根据待写入数据信号生成并传输第二写入信号至所述第二全局数据线,所述第二写入信号的电平状态与所述待写入数据相反;其中,所述校验写入电路的第一驱动模块的驱动能力强于所述数据写入电路的第一驱动模块的驱动能力,且所述校验写入电路的第二驱动模块的驱动能力强于所述数据写入电路的第二驱动模块的驱动能力。4.根据权利要求3所述的数据传输电路,其特征在于,所述第一驱动模块包括:第一上拉晶体管,所述第一上拉晶体管低电平导通,所述第一上拉晶体管的控制端用于接收反相的所述待写入数据信号,所述第一上拉晶体管的第一端与电源电压端连接;第一下拉晶体管,所述第一下拉晶体管高电平导通,所述第一下拉晶体管的控制端用于接收反相的所述待写入数据信号,所述第一下拉晶体管的第一端与接地端连接,所述第一下拉晶体管的第二端与所述第一上拉晶体管的第二端连接;其中,所述校验写入电路中第一上拉晶体管的沟道宽长比大于所述数据写入电路中第一上拉晶体管的沟道宽长比,且所述校验写入电路中第一下拉晶体管的沟道宽长比大于所述数据写入电路中第一下拉晶体管的沟道宽长比。5.根据权利要求4所述的数据传输电路,其特征在于,所述校验写入电路中第一上拉晶体管的阈值电压小于所述数据写入电路中第一上拉晶体管的阈值电压。6.根据权利要求4所述的数据传输电路,其特征在于,所述校验写入电路中第一下拉晶体管的阈值电压小于所述数据写入电路中第一下拉晶体管的阈值电压。7.根据权利要求4所述的数据传输电路,其特征在于,所述数据传输电路被配置有预充电阶段和数据写入阶段,所述第一驱动模块还包括:逻辑运算单元,分别与所述第一上拉晶体管和所述第一下拉晶体管连接,用于在所述数据写入阶段响应于写使能信号,生成反相的所述待写入数据信号;

第一非门,与所述逻辑运算单元连接,用于在所述预充电阶段控制所述逻辑运算单元输出低电平信号。8.根据权利要求7所述的数据传输电路,其特征在于,所述逻辑运算单元包括:第一与门,所述第一与门的两个输入端分别用于一一对应接收所述待写入数据信号、所述写使能信号;第一或非门,所述第一或非门的一个输入端与所述第一与门的输出端连接,所述第一或非门的另一个输入端用于接收反相的预充电信号,所述预充电信号用于切换所述数据传输电路至预充电阶段或数据写入阶段,所述第一或非门的输出端与所述第一上拉晶体管的控制端连接。9.根据权利要求8所述的数据传输电路,其特征在于,所述第一或非门的输出端还与所述第一下拉晶体管的控制端连接。10.根据权利要求8所述的数据传输电路,其特征在于,所述逻辑运算单元还包括:第一与非门,所述第一与非门的两个输入端分别用于一一对应接收所述预充电信号、所述写使能信号;第二或非门,所述第二或非门的一个输入端与所述第一与非门的输出端连接,所述第二或非门的另一个输入端用于接收所述待写入数据信号,所述第二或非门的输出端与所述第一下拉晶体管的控制端连接。11.根据权利要求3所述的数据传输电路,其特征在于,所述数据写入电路和所述校验写入电路响应于同一写使能信号,分别向对应的全局数据线组传输数据。12.根据权利要求3所述的数据传输电路,其特征在于,还包括:数据读取电路,用于从数据存储单元连接的全局数据线组获取待读取数据,以对待读取数据进行读取;校验读取电路,用于从校验存储单元连接的全局数据线组获取校验数据,以对存储的所述校验数据进行读取,存储的所述校验数据与所述待读取数据相对应;其中,所述校验读取电路的驱动能力等于所述数据读取电路的驱动能力。13.根据权利要求12所述的数据传输电路,其特征在于,所述数据读取电路和所述校验读取电路的电路结构均为第二电路,且所述数据读取电路和校验读取电路中对应器件的电性参数相同。14.根据权利要求13所述的数据传输电路,其特征在于,所述第一全局数据线还用于传输第一读取信号,所述第二全局数据线还用于传输第二读取信号,所述第一读取信号的电平状态与所述待读取数据相同,所述第二读取信号的电平状态与所述待读取数据相反,所述第二电路包括:信号处理模块,分别与所述第一全局数据线、所述第二全局数据线连接,用于响应于读使能信号,根据第一读取信号和第二读取信号生成读取驱动信号;读取驱动模块,与所述信号处理模块连接,用于根据所述读取驱动信号输出读取到的所述待读取数据。15.一种数据处理电路,其特征在于,包括:如权利要求1至14任一项所述的数据传输电路;校验生成电路,与所述校验写入电路连接,用于获取所述待存储数据,并根据所述待存

储数据生成对应的校验数据,并传输所述校验数据至所述校验写入电路。16.一种存储器,其特征在于,包括:数据存储单元、校验存储单元和如权利要求15所述的数据处理电路。

技术总结

本申请实施例涉及一种数据传输电路、数据处理电路和存储器,所述数据传输电路,包括:数据写入电路,用于传输待存储数据至全局数据线组,所述全局数据线组包括第一全局数据线和第二全局数据线,成对设置的所述第一全局数据线和所述第二全局数据线传输互为反相的数据,所述待存储数据通过所述全局数据线组传输至所述数据存储单元进行存储;校验写入电路,用于传输校验数据至校验存储单元连接的全局数据线组,以对所述校验数据进行存储,所述校验数据与所述待存储数据相对应;其中,所述数据写入电路和所述校验写入电路用于同步向对应的全局数据线组传输数据,且所述校验写入电路的驱动能力强于所述数据写入电路的驱动能力。驱动能力强于所述数据写入电路的驱动能力。驱动能力强于所述数据写入电路的驱动能力。

技术研发人员:尚为兵 李红文 冀康灵 何军 龚园媛 应战

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2021.06.01

技术公布日:2022/12/5

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。