多通道输出控制器及pcb板缺陷检测系统

技术领域

1.本发明涉及pcb板技术领域,具体涉及到一种多通道输出控制器及pcb板缺陷检测系统。

背景技术:

2.pcb板缺陷检测系统主要用于对pcb板中的短/断路、凸起/凹陷、刮伤、针孔、残铜、线宽/线距违规等缺陷进行检测。目前主要通过线性扫描或者3d扫描等扫描技术对pcb板进行扫描,从而检测pcb板是否存在上述缺陷。在通过扫描技术进行缺陷检测时,一般需要多通道输出控制器进行辅助,现有的多通道输出控制器无法对某一具体的通道进行控制,可控性较差,且降低了检测时的准确性,同时,现有的多通道输出控制器的通道数量不能扩展,扩展性较差,无法满足不同的pcb板的检测需求。

技术实现要素:

3.本发明提供一种多通道输出控制器及pcb板缺陷检测系统,旨在于解决现有的pcb板缺陷检测系统中的多通道控制器存在的可控性差和扩展性差的问题。

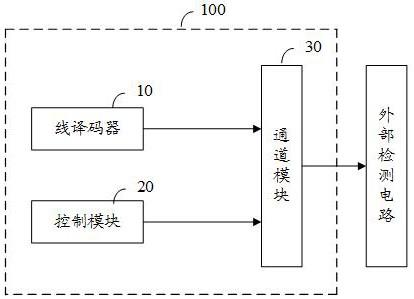

4.第一方面,本发明提供一种多通道输出控制器,所述多通道输出控制器包括线译码器、通道模块以及控制模块;所述线译码器包括n个输入端和m个输出端,所述线译码器的n个输入端用于接收外部通道确认信号,其中,m=2n;所述通道模块包括m个输出通道,每个所述输出通道的输入端对应与所述线译码器的一个输出端连接,且所有所述输出通道的输入端还用于接收外部数据信号;所述控制模块的输入端用于接收所述外部通道确认信号,所述控制模块的输出端与所述输出通道的输入端连接;其中,所述控制模块和所述线译码器根据所述外部通道确认信号在所述通道模块中确认目标通道,并发送控制信号至所述目标通道以使所述目标通道采集所述外部数据信号并输出信号至外部检测电路。

5.进一步地,所述输出通道包括第一两输入与门、第二两输入与门以及触发器;所述第一两输入与门的第一输入端与所述线译码器的一个输出端连接,所述第一两输入与门的第二输入端与所述控制模块的输出端连接,所述第一两输入与门的输出端与所述第二两输入与门的第一输入端连接,所述第二两输入与门的第二输入端用于接收外部采样信号,所述第二两输入与门的输出端与所述触发器的第二输入端连接,所述触发器的第一输入端用于接收所述外部数据信号。

6.进一步地,所述输出通道还包括选择器,所述选择器的第一输入端与所述触发器的第一输出端连接,所述选择器的第二输入端与所述触发器的第二输出端连接,所述选择器的第三输入端还用于接收外部输出选择控制信号。

7.进一步地,所述输出通道还包括输出驱动,所述输出驱动与所述选择器连接。

8.进一步地,还包括复位模块,所述复位模块与所有所述触发器连接。

9.进一步地,所述通道模块还包括一两输入非与门,所述两输入非与门的第一输入端用于接收外部复位信号,所述两输入非与门的第二输入端与所述复位模块的输出端连

接,用于接收所述复位模块输出的内部复位信号,所述两输入非与门的输出端与所有所述触发器的复位端连接。

10.进一步地,还包括施密特触发器模块,所述施密特触发器模块的输入端用于接收所述外部通道确认信号和所述外部数据信号,所述施密特触发器模块的输出端分别与所述线译码器、所述控制模块以及所有所述输出通道的输入端连接。

11.进一步地,还包括测试模块,所述测试模块包括一个多输入与非门、m个两输入与非门、以及一个开关管;所述两输入与非门的第一输入端与所述线译码器的一个输出端连接,所述两输入与非门的第二输入端与所述输出通道的输出端连接,所述两输入与非门的输出端与所述多输入与非门的一个输入端连接,所述多输入与非门的输出端与所述开关管的栅极连接,所述开关管的源极接地,所述开关管的漏极与所述外部检测电路连接。

12.进一步地,所述线译码器包括6个输入端和64个输出端,所述通道模块包括64个输出通道,每个所述输出通道对应与一个所述线译码器的输出端连接。

13.第二方面,本发明还提供一种pcb板缺陷检测系统,其包括上述任一项所述的多通道输出控制器。

14.本发明公开的多通道输出控制器及pcb板缺陷检测系统,可以通过线译码器和控制模块确认需要选通的输出通道,并将其设为目标通道,目标通道在选通后,对外部数据信号进行采集和存储,并输出信号至检测电路,不仅可以根据实际情况增加输出通道的数量,还可以精准控制某一输出通道的选通与否,在提高了扩展性的同时,提高了可控性。

附图说明

15.为了更清楚地说明本发明实施例技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

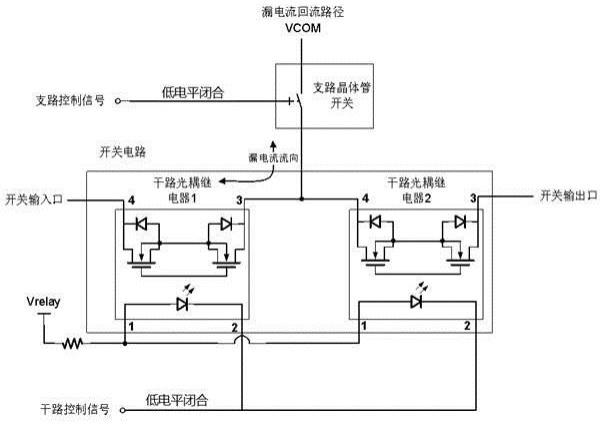

16.图1是本发明一实施例提供的多通道输出控制器的方框示意图;图2是本发明又一实施例提供的多通道输出控制器的方框示意图;图3是本发明一实施例提供的多通道输出控制器的输出通道的电路图;图4是本发明一实施例提供的多通道输出控制器的电路图;图5是本发明一实施例提供的多通道输出控制器的测试模块的电路图;图6是图4所示的多通道输出控制器的电路图中的主要信号的时序图。

具体实施方式

17.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

18.应当理解,当在本说明书和所附权利要求书中使用时,术语“包括”和

ꢀ“

包含”指示所描述特征、整体、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整体、操作、元素、组件和/或其集合的存在或添加。

19.还应当理解,在此本发明说明书中所使用的术语仅仅是出于描述特定实施例的目的而并不意在限制本发明。如在本发明说明书和所附权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一

”ꢀ“

一个”及“该”意在包括复数形式。还应当进一步理解,在本发明说明书和所附权利要求书中使用的术语“和/ 或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

20.另外,本发明所提到的方向用语,例如「上」、「下」、「前」、「后」、「左」、「右」、「内」、「外」、「侧面」等,仅是参考附加图式以及产品使用状态的方向。因此,使用的方向用语是用以说明及理解本发明,而非用以限制本发明。此外,在附图中,结构相似或相同的结构是以相同标号表示。

21.参见图1至图6,图1是本发明一实施例提供的多通道输出控制器100的方框示意图;图2是本发明又一实施例提供的多通道输出控制器100的方框示意图;图3是本发明一实施例提供的多通道输出控制器100的输出通道31的电路图;图4是本发明一实施例提供的多通道输出控制器100的电路图;图5是本发明一实施例提供的多通道输出控制器100的测试模块40的电路图;图6是图4所示的多通道输出控制器100的电路图中的主要信号的时序图。

22.如图1所示,所述多通道输出控制器100包括线译码器10、通道模块30以及控制模块20;所述线译码器10包括n个输入端和m个输出端,所述线译码器10的n个输入端用于接收外部通道确认信号,其中,m=2n;所述通道模块30包括m个输出通道31,每个所述输出通道31的输入端对应与所述线译码器10的一个输出端连接,且所有所述输出通道31的输入端还用于接收外部数据信号data;所述控制模块20的输入端用于接收所述外部通道确认信号,所述控制模块20的输出端与所述输出通道31的输入端连接;其中,所述控制模块20和所述线译码器10根据所述外部通道确认信号在所述通道模块30中确认目标通道,并发送控制信号至所述目标通道以使所述目标通道采集所述外部数据信号data并输出信号至外部检测电路。

23.其中,线译码器10用于对输入的二进制码进行译码,并确定需要选通的输出通道31,线译码器10可以包括n个输入端和m个输出端,其中,m=2n。例如,线译码器10可以包括4个输入端和16个输出端。通道模块30可以包括m个输出通道31,例如,16个输出通道31,则每个输出通道31对应与一个线译码器10的输出端连接,用于接收线译码器10发送的控制信号。控制模块20可以级联多个控制芯片,每个控制芯片都可以与同样数量的输出通道31连接,用于控制对应的输出通道31,当输出通道31增加后,可以同步增加控制芯片的数量,便于扩展输出通道31。控制模块20在接收到外部通道确认信号后,会使能相应的控制芯片,然后根据外部通道确认信号发送控制信号至对应的输出通道31,其中,外部通道确认信号可以包括外部通道地址信号和片选信号,线译码器和控制模块根据外部通道地址信号确认目标通道,控制模块还根据片选信号使能相应的控制芯片,从而控制相应的输出通道31选通。例如,若需要将线译码器10第二个输出端所连接的输出通道31选通,则将该通道作为目标通道,线译码器10通过第二输出端将控制信号输出至目标通道,同时,控制模块20同步将控制信号发送至目标通道,目标通道同时接收到线译码器10发送的控制信号和控制模块20发送的控制信号后导通,其中,控制信号可以是电平信号,可以将输出通道31设置为同时接收到高电平信号时导通。目标通道在导通后,外部数据信号data通过目标通道输出至后级电路,后级电路可以是检测电路,用于检测pcb板是否存在缺陷。需要注意的是,同一时间同时

选通的输出通道31可以是多个,在这里并不进行限定。

24.作为进一步的实施例,所述输出通道31包括第一两输入与门311、第二两输入与门312以及触发器313;所述第一两输入与门311的第一输入端与所述线译码器10的一个输出端连接,所述第一两输入与门311的第二输入端与所述控制模块20的输出端连接,所述第一两输入与门311的输出端与所述第二两输入与门312的第一输入端连接,所述第二两输入与门312的第二输入端用于接收外部采样信号clk,所述第二两输入与门312的输出端与所述触发器313的第二输入端连接,所述触发器313的第一输入端用于接收所述外部数据信号data。

25.其中,如图3所示,第一两输入与门311的第一输入端与线译码器10的一个输出端连接,用于接收对应的控制信号,其第二输入端与控制模块20连接,用于接收控制信号,例如,可以与控制模块20中的控制芯片的使能引脚连接。第二两输入与门312的第一输入端与第一两输入与门311的输出端连接,其第二输入端用于接收clk信号,即时序信号,其输出端与触发器313连接。触发器313可以是d触发器,用于对外部数据信号data进行采样存储,其第一输入端d用于接收外部数据信号data,其第二输入端clk与第二两输入与门312的输出端连接,其输出端用于输出外部数据信号data。当第一两输入与门311的第一输入端接收到线译码器10输出的控制信号,以及第二输入端接收到控制模块20输出的控制信号时,第一两输入与门311导通并输出信号至第二两输入与门312的第一输入端,若第二两输入与门312的第二输入端接收到外部采样信号clk,则第二两输入与门312导通,并输出信号至触发器313。外部数据信号data可以一直进行传输,但当触发器313接收到的第二两输入与门312输出的信号时才开始对外部数据信号data进行采集并将采集的外部数据信号data作为输出信号输出。

26.作为进一步的实施例,所述输出通道31还包括选择器314,所述选择器314的第一输入端与所述触发器313的第一输出端连接,所述选择器314的第二输入端与所述触发器313的第二输出端连接,所述选择器314的第三输入端还用于接收外部输出选择控制信号pol。

27.其中,如图3所示,选择器314可以是二选一多路选择器,用于根据输出选择控制信号pol选择输出信号是正逻辑电平输出还是反逻辑电平输出,便于满足不同需求的缺陷检测。

28.作为进一步的实施例,所述输出通道31还包括输出驱动315,所述输出驱动315与所述选择器314连接。

29.其中,如图3所示,输出驱动315主要用于提升输出信号的驱动能力。

30.作为进一步的实施例,还包括复位模块50,所述复位模块50与所有所述触发器313连接。

31.其中,如图3所示,触发器313还可以包括第三输入端nrst。触发器313的第三输入端nrst与复位模块50连接,可通过复位模块50对触发器313进行复位,便于进行下一次缺陷检测。

32.作为进一步的实施例,所述通道模块30还包括一两输入非与门32,所述两输入非与门32的第一输入端用于接收外部复位信号rst0,所述两输入非与门32的第二输入端与所述复位模块50的输出端连接,用于接收所述复位模块50输出的内部复位信号rst1,所述两

输入非与门32的输出端与所有所述触发器313连接。

33.其中,复位模块50可以通过一个两输入非与门32与触发器313的第三输入端连接,该两输入非与门32的第一输入端用于接收外部复位信号rst0,其第二输入端与复位模块50连接,用于接收内部复位信号rst1,当接收到任一复位信号时,输出信号至触发器313,触发器313进行复位,停止外部数据信号data的采集以及清除所存储的外部数据。另外,复位模块50也可以通过或非门与触发器313的第三输入端连接。

34.作为进一步的实施例,还包括施密特触发器模块60,所述施密特触发器模块60的输入端用于接收所述外部通道确认信号和所述外部数据信号data,所述施密特触发器模块60的输出端分别与所述线译码器10、所述控制模块20以及所有所述输出通道31的输入端连接。

35.其中,施密特触发器模块60可以包括多个施密特触发器61,用于抑制输入信号中的噪声,防止误触发。输入信号包括但不限于外部数据信号data,外部复位信号rst0,外部通道确认信号以及外部采样信号clk等信号。

36.作为进一步的实施例,还包括测试模块40,所述测试模块40包括一个多输入与非门42、m个两输入与非门41、以及一个开关管ts;所述两输入与非门41的第一输入端与所述线译码器10的一个输出端连接,所述两输入与非门41的第二输入端与所述输出通道31的输出端连接,所述两输入与非门41的输出端与所述多输入与非门42的一个输入端连接,所述多输入与非门42的输出端与所述开关管ts的栅极连接,所述开关管ts的源极接地,所述开关管ts的漏极与所述外部检测电路连接。

37.其中,如图2所示和图5所示,测试模块40用于判断通道模块30输出的输出信号的逻辑是否正确。测试模块40包括m个两输入与非门41,即该两输入与非门41的数量与输出通道31的数量相同,每个两输入与非门41的第一输入端均与一个输出通道31连接用于接收输出通道31输出的输出信号,每个两输入与非门41的第二输入端还与线译码器10连接,用于接收线译码器10输出的信号,当该两输入与非门41同时接收到线译码器10和输出通道31的输出信号时,才会输出信号至多输入与非门42。多输入与非门42用于实现多个输入信号之间的与非关系,输出信号经多输入与非门42输出至开关管ts,该开关管可以是nmos管,nmos管的漏极将输出信号输出。

38.作为进一步的实施例,所述线译码器10包括6个输入端和64个输出端,所述通道模块30包括64个输出通道31,每个所述输出通道31对应与一个所述线译码器10的输出端连接。

39.其中,如图4所示,线译码器10可以是6-64线译码器10,其包括6个输入端和64个输出端,对应的,通道模块30可以包括64个输出通道31,施密特触发器模块60可以包括11个施密特触发器61,其中,三个施密特触发器61分别用于接收外部输入信号din,外部采样信号clk以及外部复位信号rst0,余下九个施密特触发器61用于接收外部通道确认信号,在这九个施密特触发器61中,六个用于与线译码器10连接,两个用于与控制模块20连接。线译码器10的一个输出端对应与一个输出通道31连接,便于输出对应的信号至输出通道31,如图4所示,a1~a6信号为外部通道地址信号,a7~a8信号为外部通道地址信号和片选信号,b1~b6信号表示a1~a6信号经施密特触发器61处理过后输出的信号,s1~s64信号表示线译码器10输出的信号,对应于不同的输出通道31。输出通道31的第一两输入与门311的第二输入端均与

控制模块20连接。当线译码器10输出s2信号且控制模块20同时输出控制信号时,图4所示中的第二个输出通道31导通,当触发器313接收到第二两输入与门312发送的信号时,开始采集存储外部数据信号data,并最终将输出信号dout2输出。

40.如图6所示,图6是图4所示电路中主要信号工作的时序图,hi为高电平,lo为低电平,曲线连接的表示相关联的信号,a《6:1》为译码器的输入地址,用于确定选通的通道。从图6中可以看出,当din信号电平升高时,dout[n]信号为低电平,没有信号输出,当外部采样信号clk为高电平时,表明第n个输出通道31的触发器313开始采集外部数据,并输出信号,则dout[n]信号的电平为高,即第n个输出通道31会在外部采样信号clk的上升沿到来时,随着输入信号的变化而变化,需要注意的,其它未被选通的输出通道31,其输出信号维持上一时刻的波形不变,如图6中dout[n 1]信号所示。当第n个输出通道31再次接收到的外部采样信号clk时,触发器313停止对外部数据信号data的采样,则dout[n]的电平为低。同时,当第n个输出通道31开始对外部数据采样一段时间后,若第n 1个输出通道31也接收到了外部采样信号clk,则dout[n 1]的电平为高,第n 1个输出通道31开始采集外部数据信号data,并开始输出。从图6中可以看出,当dout[n 1]的电平为高时,dout[n]信号的电平保持不变,并不会影响第n个输出通道31的输出。当rst信号的电平为高时,表明所有的触发器313均进行了复位,停止数据的采集并清除已存储的数据,如图6所示,din信号和dout[n 1]信号的电平均为低电平。另外,tsn信号由测试模块40输出,用于辅助判断所选通的输出通道31输出信号的正确性。

[0041]

本发明还公开了一种pcb板缺陷检测系统,其包括上述任一项所述的多通道输出控制器100。

[0042]

本发明公开的多通道输出控制器及于pcb板缺陷检测系统,可以通过线译码器和控制模块确认需要选通的输出通道,并将其设为目标通道,目标通道在选通后,可以对外部数据信号进行采集并输出信号至检测电路,同时,可以根据实际情况增加输出通道的数量,提高了扩展性和可控性。

[0043]

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。