非易失性存储单元的制造方法

1.本技术是申请号为202080012917.7,申请日为2020年6月9日,发明名称为“非易失性存储单元、非易失性存储单元阵列及其制造方法”的专利申请的分案申请。

2.相关申请的交叉引用

3.本技术要求申请号为16/669391,申请日为2019年10月30日,名称为“非易失性存储单元、非易失性存储单元阵列及其制造方法”的美国申请以及申请号为62/862307,申请日为2019年6月17日,名称为“非易失性存储单元、非易失性存储单元阵列及其制造方法”的美国临时申请的优先权。申请号为16/669391的美国申请要求申请号为62/862307的美国临时申请的优先权及权益。此两申请的公开内容整体援引于此。

技术领域

4.本发明总体涉及存储单元的制造方法,尤其涉及非易失性存储单元的制造方法。

背景技术:

5.手机、计算机、汽车、显示器等许多电子设备均含有存储器件。存储器件用于存储用于各种目的数据。取决于断电后所存数据是被保留还是被擦除,存储器件一般包括两种存储类型。对于易失性存储器件,每当易失性存储器件的电源关断时,其内的数据均将被清除。然而,对于非易失性存储器件,即使在电源关断时,其内保存的数据仍会得到保留。

6.非易失性存储器件通常包括拥有数万个存储单元的存储阵列。图1为现有非易失性存储器件的存储单元100的示意图。存储单元100包括底电极102、顶电极104、置于底电极102和顶电极104之间的介质层106、以及与顶电极104连接的金属线路108。底电极102和顶电极104通常包括导电材料,而介质层106通常含有氧化物。该现有存储单元100具有若干缺点。例如,出于结构原因,金属线路108与介质层106之间,或金属线路108与底电极102之间,可能会发生短路。短路将对存储单元100造成损害,或使得其无法正常工作。此外,介质层106内的氧可能会逸出至存储单元100的其他部分,从而使得存储单元100功能下降。

7.图2为现有非易失性存储器件的存储单元200的示意图。存储单元200包括底电极202、顶电极204、设于底电极202和顶电极204之间的介质层206、与顶电极204连接的顶部金属线路208、与底电极202连接的底部金属线路210、以及设于底部金属线路210与介质层206之间的绝缘层212。绝缘层212将底电极202绝缘,从而减小顶部金属线路208与底电极202之间发生短路的可能性。然而,顶部金属线路208与介质层206之间仍旧存在发生短路的可能性。此外,介质层206内的氧仍有可能会逸出至存储单元200的其他部分,从而降低存储单元200的可靠性。

技术实现要素:

8.本发明涉及一种非易失性存储单元制造方法。在第一金属线路上形成第一介质层后,刻蚀该第一介质层,以形成直达所述第一金属线路的第一过孔。在所述第一过孔内形成底电极后,在所述底电极和所述第一介质层上形成电阻层,顶电极以及第二介质层。随后,

氧化所述电阻层和所述顶电极,以形成覆盖该顶电极和电阻层的侧面部分。形成覆盖所述第二介质层和所述侧面部分的侧墙层后,形成第二过孔,该第二过孔贯穿所述侧墙层和所述第二介质层,直达所述顶电极。之后,在所述第二过孔内形成接触导线,该接触导线的宽度小于所述侧面部分的外侧面间宽度。

9.当参考附图考察下文及下附权利要求时,本文公开的各装置、系统及方法的上述和其他特征以及操作方法和相关结构元件的功能将变得更加显而易见,所有附图均构成本说明书的一部分。然而,应该明确理解的是,附图仅出于说明和描述目的,并不旨在界定出本发明的限制范围。应该理解的是,无论是上文的概述内容,还是下文的详述内容,均仅为举例性和阐述性内容,并不对所要求保护的本发明有所限制。

附图说明

10.通过参考以下附图,可更加容易地理解本发明的非限制性实施方式。

11.图1为现有非易失性存储器件存储单元示意图。

12.图2为另一现有非易失性存储器件存储单元示意图。

13.图3a为根据一种例示实施方式的存储单元沿x方向截面示意图。

14.图3b为根据一种例示实施方式的图3a存储单元沿y方向截面示意图。

15.图4a为根据一种例示实施方式的另一存储单元沿x方向截面示意图。

16.图4b为根据一种例示实施方式的图4a存储单元沿y方向截面示意图。

17.图5a为根据一种例示实施方式的另一存储单元沿x方向截面示意图。

18.图5b为根据一种例示实施方式的图5a存储单元沿y方向截面示意图。

19.图6所示为根据一种例示实施方式含本发明存储单元的存储阵列的一部分。

20.图7为根据一种实施方式的存储单元制造方法流程图。

21.图8a至图8w为根据各种例示实施方式的存储单元制造方法流程示意图。

具体实施方式

22.以下,参考附图,描述本发明的非限制性实施方式。应该理解的是,本文公开的任何实施方式的具体特征和方面均可与本文公开的任何其他实施方式的具体特征和方面一起使用且/或相互结合。还应该理解的是,此类实施方式为举例,而且仅阐述了本发明范围内的一小部分实施方式。对于本发明所属技术领域的技术人员而言容易理解的各种变化和修饰均视为落于如下附权力进一步限定的本发明精神、范围及构思之内。

23.本文公开的技术提供能够克服现有存储单元缺点的存储单元。以下实施方式提供的方案能够简化制造流程,并且与逻辑电路工艺相兼容。采用本发明存储单元的存储器件具有稳定的存储性能,从而提高器件的可靠性。

24.以下,参考附图,对各实施方式进行描述。首先,参考图3a和图3b,其中,图3a为根据一种例示实施方式的存储单元300的沿x方向截面示意图,图3b为根据一种例示实施方式的存储单元300的沿y方向截面示意图。存储单元300包括底电极302、顶电极304、设于底电极302与顶电极304之间的介质层306、与顶电极304连接的顶部接触导线308、以及与底电极302连接的底部接触导线310。底电极302、顶电极304以及介质层306的侧面由侧面部分312覆盖。侧面部分312上设置绝缘层314。侧面部分312和绝缘层314的外表面上覆盖侧墙316。

底电极302下设置用于将底部接触导线310绝缘的底部绝缘层318。侧墙316上设置用于将顶部接触导线308绝缘的顶部绝缘层320。如图3b所示,由底电极302、顶电极304以及介质层306组成的两个相邻叠层结构在y方向上由侧墙316和顶部绝缘层320隔开。

25.在一些实施方式中,底电极302含有tin、tan、w或其他合适导电材料中的至少一种。在一些实施方式中,顶电极304含有tin、tan、ru、pt、ir、w以及其他合适导电材料中的至少一种。介质层306可以为含电阻材料的电阻层。介质层306可例如包括ta2o5、tao

x

、wo

x

、tio

x

、zro

x

等一种或多种电阻性金属氧化物。在一些实施方式中,电阻层306包括一层或多层薄膜。电阻层306可例如具有第一薄膜以及设于第一薄膜上的第二薄膜。第二薄膜与第一薄膜不同。在一些实施方式中,第一薄膜含有第一金属氧化物,第二薄膜含有第二金属氧化物。

26.顶部接触导线308和底部接触导线310可含有金属等导电材料。各接触导线例如含有cu、al、au、pt、w等。侧面部分312至少含有顶电极304内所含导电材料的氧化物。在一些实施方式中,侧面部分312可进一步含有电阻层306的氧化物。在一些实施方式中,侧面部分312可进一步含有底电极302的氧化物。

27.绝缘层314可含有sion、sin、sio

x

、csinh、csioh或其他绝缘材料。侧墙316可含有sio2、si3n4、teos、csinh等。侧墙316延伸至绝缘层314的顶面和底部绝缘层318的顶面上。顶部接触导线308的宽度d1小于侧面部分312的外侧面之间的宽度d2。顶部接触导线308的宽度d1大于顶电极304的宽度d3。顶部接触导线308的部分底面和顶部接触导线308的部分侧面与侧面部分312相接触。此外,顶部接触导线308的侧面与绝缘层314和侧墙316相接触。

28.在图示实施方式中,底电极302、顶电极304以及电阻层306的侧面由绝缘性的侧面部分312覆盖,从而显著减小顶部接触导线308与电阻层306之间以及顶部接触导线308与底电极302之间发生短路的可能性。此外,覆盖电阻层306侧面的侧面部分312有效阻止氧从电阻层306扩散至存储单元300的其他部分。此类结构可提高存储单元300的性能和可靠性,并且可尤其提高存储单元300的保持能力。

29.图4a为根据一种例示实施方式的存储单元400的沿x方向截面示意图,图4b为根据一种例示实施方式的存储单元400的沿y方向截面示意图。存储单元400包括底电极402、顶电极404、设于底电极402与顶电极404之间的介质层/电阻层406、与顶电极404连接的顶部接触导线408、以及与底电极402连接的底部接触导线410。顶电极404以及介质层406的侧面由侧面部分412覆盖。侧面部分412上设置绝缘层414。侧面部分412和绝缘层414的外表面上覆盖侧墙416。底部接触导线410上设置用于将底电极402绝缘的底部绝缘层418。侧墙416上设置用于将顶部接触导线408绝缘的顶部绝缘层420。如图4b所示,由底电极402、顶电极404以及介质层406组成的两个相邻叠层结构在y方向上由侧墙416和顶部绝缘层420隔开。

30.存储单元400与图3a和图3b所示存储单元300类似,其区别在于,底电极402设于底部绝缘层418内的过孔中,并与底部接触导线410连接。在存储单元400中,侧面部分412至少含有顶电极404所含导电材料的氧化物。在一些实施方式中,侧面部分412可进一步含有电阻层406的氧化物。在图示实施方式中,侧面部分412可不含底电极402的氧化物。

31.顶部接触导线408的宽度d4小于侧面部分412外侧面之间的宽度d5。顶部接触导线408的宽度d4大于顶电极404的宽度d6。底电极402的宽度d7小于顶电极404或电阻层406的宽度d6。

32.顶电极404以及电阻层406的侧面由绝缘性的侧面部分412覆盖,从而减小顶部接触导线408与电阻层406之间发生短路的可能性。此外,嵌于底部绝缘层418内过孔中的底电极402减小了顶部接触导线408与底电极402之间发生短路的可能性。此外,覆盖电阻层406侧面的侧面部分412有效阻止氧从电阻层406扩散至存储单元400的其他部分。此类结构可提高存储单元400的性能和可靠性。

33.图5a为根据一种例示实施方式的存储单元500的沿x方向截面示意图,图5b为根据一种例示实施方式的存储单元500的沿y方向截面示意图。存储单元500包括底电极502、顶电极504、设于底电极502与顶电极504之间的介质层/电阻层506、与顶电极504连接的顶部接触导线508、以及与底电极502连接的底部接触导线510。顶电极504以及介质层506的侧面由侧面部分512覆盖。侧面部分512上设置绝缘层514。侧面部分512和绝缘层514的外表面上覆盖侧墙516。底部接触导线510上设置用于将底电极502绝缘的底部绝缘层518。侧墙516上设置用于将顶部接触导线508绝缘的顶部绝缘层520。

34.如图5b所示,电阻层506和顶电极504形成为沿y方向连接多个存储单元500的线状结构。每一底电极502均由底部绝缘层518隔开。

35.与图4a和图4b所示存储单元400相似,在x方向上,顶部接触导线508的宽度d8小于侧面部分512外侧面之间的宽度d9。顶部接触导线508的宽度d8大于顶电极504的宽度d10。底电极502的宽度d11小于顶电极504或电阻层506的宽度d10。

36.顶电极504以及电阻层506的侧面由绝缘性的侧面部分512覆盖,从而减小顶部接触导线508与电阻层506之间发生短路的可能性。此外,嵌于底部绝缘层518内过孔中的底电极502减小了顶部接触导线508与底电极502之间发生短路的可能性。此外,覆盖电阻层506侧面的侧面部分512有效阻止氧从电阻层506扩散至存储单元500的其他部分。此类结构可提高存储单元500的性能和可靠性。

37.本文公开的存储单元可用于形成存储器件的存储阵列。图6所示为根据一种例示实施方式含本发明存储单元的存储阵列600的一部分。存储阵列600包括多个存储单元602。每一存储单元可包括电阻元件604和晶体管606。存储阵列600采用含字线610和位线620的交叉点结构。字线610和位线620的延伸方向彼此正交。字线610与位线620的每一交叉点上设置一个电阻式存储单元602。字线610与字线解码器615连接,字线解码器615用于选择与相应一行电阻式存储单元602连接的一条字线。位线620与位线解码器625连接,位线解码器625用于选择与相应一列电阻式存储单元602连接的一条位线。存储阵列600还包括与字线610平行延伸的多条源线630。在一些实施方式中,源线630也可与位线620平行延伸。

38.晶体管606的栅极与字线610连接。晶体管606的源极与源线630连接,晶体管606的漏极与电阻元件604的一端连接。电阻元件604的另一端与位线620连接。取决于经被选字线610和被选位线620施加在处于被选字线610和被选位线620交叉点上的电阻式存储单元602上的相应电压脉冲的持续时间、大小及极性,该电阻式存储单元102接受读取、复位或置位操作。

39.采用上述存储单元的存储阵列可应用于各种电子器件和系统。例如,该存储阵列可作为微控制单元、射频识别系统等的部件。

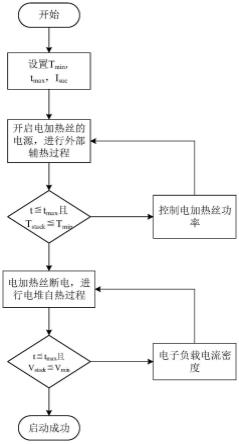

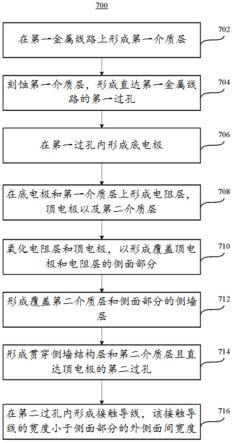

40.以下,参考图7,对上述实施方式存储单元的制造方法进行说明。图7为根据一种实施方式的存储单元制造方法700流程图。在702中,在第一金属线路上形成第一介质层。在

704中,通过刻蚀第一介质层形成直达第一金属线路的第一过孔。在706中,在第一过孔内形成底电极。在708中,在底电极和第一介质层上形成电阻层,顶电极以及第二介质层。在710中,通过氧化电阻层和顶电极,形成覆盖顶电极和电阻层侧面的侧面部分。在712中,形成覆盖第二介质层和侧面部分的侧墙层。在714中,形成贯穿侧墙层和第二介质层且直达顶电极的第二过孔。在716中,在第二过孔中形成接触导线,以使得该接触导线的宽度小于侧面部分外侧面之间的宽度。

41.以下,参考图8a至图8w,对上述实施方式存储单元的另一制造方法进行说明。图8a至图8w为根据各种例示实施方式的存储单元制造方法流程示意图。首先,参考图8a,在衬底800上形成包括金属线路802a和802b的多条底部金属线路802。虽然图8a中未示出,但衬底800可包括用于控制存储单元的其他电路。随后,在底部金属线路802和衬底800上沉积第一介质层804。第一介质层804可含有氧化硅、氮化硅、氮氧化硅或其他绝缘材料。第一介质层804可通过物理气相沉积法或化学气相沉积法进行沉积。

42.参考图8b,在第一介质层804上沉积光刻胶806,并对光刻胶806执行光刻工艺,以在光刻胶806中形成暴露出第一介质层804表面的开孔810。参考图8c,经开孔810刻蚀第一介质层804,以直达底部金属线路802的表面,并去除第一介质层804顶面上的光刻胶806,以形成第一过孔810(图8d)。随后,在第一介质层804上以及第一过孔810内沉积导电层812(图8e),并利用化学机械研磨(cmp)法去除第一介质层804表面上的导电层812,并留下第一过孔810内的导电层812(图8f)。过孔内的导电层812构成非易失性存储单元的底电极814。

43.随后,参考图8g,在图8f所示结构上沉积含一种或多种金属氧化物(mo

x

)的电阻层816。在一些实施方式中,电阻层816可含有ta2o5、tao

x

等一种或多种电阻性金属氧化物。在一些实施方式中,电阻层816可包括一层或多层薄膜。电阻层816可例如具有第一薄膜以及设于第一薄膜上的第二薄膜。第二薄膜与第一薄膜不同。在一些实施方式中,第一薄膜含有第一金属氧化物,第二薄膜含有第二金属氧化物。例如,首先在底电极814和第一介质层804上沉积ta2o5第一薄膜,然后在第一薄膜上沉积tao

x

第二薄膜。随后,在电阻层816上沉积导电层818(图8h),然后在导电层818上沉积第二介质层820(图8i)。此后,在第二介质层820上涂敷光刻胶,然后通过将光刻胶图案化而形成光刻胶图案822(图8j)。在一些实施方式中,在光刻胶图案化工艺中,可将金属线路802a用作掩膜,以使得光刻胶图案822沿宽度方向与金属线路802a对齐。

44.在此之后,利用光刻胶图案822刻蚀第二介质层820,以形成残留第二介质层824(图8k)。随后,通过剥除光刻胶图案822而露出第二介质层824(图8l)。在一些实施方式中,光刻胶图案822通过光刻胶灰化法剥除。例如,可利用等离子体源产生氧或氟等活性物质。活性物质通过与光刻胶图案822反应而使其灰化,所形成的灰由真空泵去除。其后,以第二介质层824为掩膜,刻蚀导电层818,以形成存储单元的顶电极826(图8m)。之后,仍旧以第二介质层824为掩膜,刻蚀电阻层816,以形成残留电阻层828(图8n)。

45.参考图8o,对顶电极826和电阻层828执行氧化工艺,以形成覆盖顶电极830和电阻层828侧面的侧面部分830。侧面部分830至少含顶电极830导电材料的氧化物。在一些实施方式中,侧面部分830还可含有电阻层828的氧化物。

46.在氧化工艺之后,在衬底800上沉积覆盖第二介质层824、侧面部分830以及第一介质层804的侧墙层832(图8p)。在一些实施方式中,侧墙层832例如含氧化硅。侧墙层832可例

如通过四乙氧基硅烷(teos)形成。在一些实施方式中,随后在侧墙层832上沉积厚绝缘层834(图8q)。在一些实施方式中,可通过teos或其他合适的绝缘材料形成绝缘层834。其后,实施cmp工艺,将绝缘层834不平坦的表面平坦化(图8r)。

47.在此之后,在绝缘层834平坦化后的表面上涂敷光刻胶836,并通过光刻胶的图案化,在绝缘层834中形成与金属线路802b对应的开孔838(图8s)。随后,经光刻胶836中的开孔838,对绝缘层834、侧墙层832以及第一介质层804进行图案化,以形成暴露出金属线路802b表面的沟槽840,然后将残留光刻胶836剥除(图8t)。之后,继续在衬底800上涂敷光刻胶842,并对其进行图案化,以形成分别与顶电极826和沟槽840对应的两个开孔844和846(图8u)。

48.参考图8v,利用光刻胶842中的开孔844,形成第二过孔848,该第二过孔848贯穿绝缘层834、第二介质层824上的侧墙层932以及第二介质层824,直至顶电极826的表面。此外,利用光刻胶842中的开孔846,进一步形成第三过孔850。第三过孔850与沟槽840重叠,而且宽度大于沟槽840。之后,将衬底800上的光刻胶842剥除。参照图8w,在衬底800上沉积金属层,该金属层填充第二过孔848、第三过孔850以及沟槽840。其后,通过cmp工艺去除绝缘层834上的多余金属层,以形成存储单元854的顶部接触线路852,以及与金属线路802b接触的接触布线结构856。

49.如图8w所示,形成顶部接触线路852,顶部接触线路852的宽度d20小于侧面部分830外侧面之间的宽度d21。顶部接触线路852的宽度d20大于顶电极826的宽度d22。顶电极826以及电阻层828的侧面由绝缘性的侧面部分830覆盖,从而减小顶部接触导线852与电阻层828之间发生短路的可能性。此外,嵌于第一介质层804内第一过孔810中的底电极814减小了顶部接触线路852与底电极814之间发生短路的可能性。另外,覆盖电阻层828侧面的侧面部分830有效阻止氧从电阻层828扩散至存储单元854的其他部分。此类结构可提高存储单元854的性能和可靠性。

50.应该理解的是,图8a至图8w所示实施方式在于举例。本领域的普通技术人员可以理解的是,在不脱离本发明精神的情况下,上述方法、工艺及步骤可以进行不同程度的修改。

51.虽然本文中描述了本公开内容之原理的示例和特征,但是在不脱离本公开内容实施方式的精神和范围的情况下,还可进行修饰和更改,并且存在其他的实现形式。此外,“包括”、“具有”、“包含”、“内含”四词以及其他类似形式旨在在含义上等同,而且为开放性词语,也就是说,这些词当中的任一词后所跟的一个或多个物项并不旨在为这一或这些物项的穷举式罗列,也不旨在为仅限于所列出的一个或多个物项。必须注意的是,在本文和下附权利要求书中,除非上下文另外明确指出,否则未指明数目之物不但包含单数之意,还涵盖复数之意。

52.本文所给出的实施方式的描述详细程度足以令本领域技术人员能够实践所公开的技术方案。除此之外,还可使用其他实施方式,或者从中导出其他实施方式,因此在不脱离本发明范围的情况下,还可在结构上和逻辑上做出替代和变化。因此,该“具体实施方式”部分不应理解为具有限制性,而且各种实施方式的范围仅由所附权利要求以及这些权利要求所有等效物限定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。