1.本发明一般涉及集成电路技术领域,特别涉及一种多相位时钟信号产生电路。

背景技术:

2.随着通信技术的发展,单位时间内产生的数据量越来越来,所需要的通信速度也越来越快。因为高速模数转换器变得越来越重要。对于32gs/s或者64gs/s采样率来说,时钟交织是比较常规的架构。对于时钟交织电路,需要复杂的时钟产生电路来造就多个相位时钟的交织。对于时钟产生电路,功能上来说,相位的相对顺序是必要满足的。此外功耗和时钟抖动都是性能所必须的。然而对于很多传统的用分频器来产生多个相位的产生方式,有个必须要的模块就是时钟同步复位模块来保证时钟从源头就是同步的,没有任何毛刺的,相位关系是完全确定的。此外后面所有的分频器都要复位到特定状态来保证每个分频器起来的时序状态,这样会大大增加设计的复杂的。时钟同步复位还有一个问题是额外的功耗和额外的时钟抖动,而这两个性能指标是需要我们去优化的。更加严重的是,随着模数转换器的速率越来越快,时钟同步复位将不可能实现,或者多项输入时钟用别的电路去产生,同步时钟更无从说起。

技术实现要素:

3.本发明的目的在于提供一种多相位时钟信号产生电路,主要解决在高速时钟信号仅有0度和180度相位输出时,如何产生高精度的4相位甚至8相位时钟信号。

4.本技术公开了一种多相位时钟信号产生电路,包括依次串联连接的延迟单元、第一多相位滤波器、第一信号转换器、第二多相位滤波器、第三多相位滤波器和第二信号转换器;其中,

5.所述延迟单元接收两相位或四相位时钟信号并输出四相位或八相位时钟信号到所述第一多相位滤波器;

6.所述第一多相位滤波器、第二多相位滤波器和第三多相位滤波器各自将所述四相位或八相位时钟信号的相位误差转换为幅度误差;

7.所述第一信号转换器和第二信号转换器各自将所述四相位或八相位时钟信号的幅度误差放大到满摆幅从而消除所述幅度误差。

8.在一个优选例中,所述延迟单元接收相位为0

°

和180

°

的两相位时钟信号并输出相位为0

°

、90

°

、180

°

和270

°

的四相位时钟信号,所述第一多相位滤波器、第二多相位滤波器和第三多相位滤波器分别为四相位滤波器,所述四相位滤波器包括串联的四组rc滤波单元,每组rc滤波单元分别将所述0

°

、90

°

、180

°

和270

°

的四相位时钟信号中的一路时钟信号的相位误差转换为幅度误差。

9.在一个优选例中,每组所述rc滤波单元设置到极点频率相位移动90

°

,以将所述四相位时钟信号的相位误差转换为幅度误差。

10.在一个优选例中,所述延迟单元接收相位为0

°

、90

°

、180

°

和270

°

的四相位时钟信

号并输出相位为0

°

、45

°

、90

°

、135

°

、180

°

、225

°

、270

°

和315

°

的八相位时钟信号,所述第一多相位滤波器、第二多相位滤波器和第三多相位滤波器分别为八相位滤波器,所述八相位滤波器包括串联的八组rc滤波单元,每组rc滤波单元分别将所述0

°

、45

°

、90

°

、135

°

、180

°

、225

°

、270

°

和315

°

的八相位时钟信号中的一路时钟信号的相位误差转换为幅度误差。

11.在一个优选例中,每组所述rc滤波单元设置到极点频率相位移动45

°

,以将所述八相位时钟信号的相位误差转换为幅度误差。

12.在一个优选例中,所述延迟单元包括两路或四路延迟线,每路延迟线分别对一路时钟信号延迟90

°

相位。

13.在一个优选例中,所述第一信号转换器和第二信号转换器各自包括四个或八个转换单元,每个转换单元包括反相器、电阻器和电容器,所述电阻器的一端连接所述反相器的输入端,所述电阻器的另一端连接所述反相器的输出端,所述电容器的一端耦合到四相位或八相位时钟信号其中的一路信号,所述电容器的另一端连接所述反相器的输入端。

14.相对于现有技术,本发明具有以下有益效果:

15.本专利涉及一种新的多相位时钟信号产生电路。该电路具备从2相位时钟输入,产生准确的4相位甚至8相位时钟的能力。该新型电路主要由延迟单元、多级多相位滤波器以及ac信号转cmos信号的电路组成。其中相位的精度由多相位滤波器的级数决定,级数越高,精度越高,同时它的功耗也越大,噪声性能则同时下降。其中相位滤波器纠正了相位信息的同时,产生幅度误差,则由ac信号转cmos信号放大至满摆幅消除。

16.该多相位时钟信号产生电路有以下技术特点:1.宽频率范围;2.高精度,能够精确产生0度、90度、180度、270度相位;3.较为简单的电路结构。

17.本说明书中记载了大量的技术特征,分布在各个技术方案中,如果要罗列出本技术所有可能的技术特征的组合(即技术方案)的话,会使得说明书过于冗长。为了避免这个问题,本说明书上述发明内容中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均应该视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a b c,在另一个例子中公开了特征a b d e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a b c d的方案因技术不可行而应当不被视为已经记载,而a b c e的方案应当视为已经被记载。

附图说明

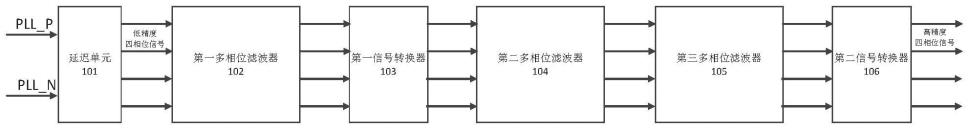

18.图1示出了本发明一个实施例中四相位产生电路的示意图。

19.图2示出了本发明一个实施例中延迟单元的示意图。

20.图3示出了本发明一个实施例中四相位滤波器的示意图。

21.图4示出了本发明一个实施例中信号转换器的示意图。

22.图5示出了本发明一个实施例中产生的四相位时钟信号的结果。

23.图6示出了本发明一个实施例中八相位产生电路的示意图。

24.图7示出了本发明一个实施例中八相位滤波器的示意图。

具体实施方式

25.现在将描述本技术的各个方面和示例。以下描述提供了用于彻底理解和实现这些示例的描述的具体细节。然而,本领域技术人员将理解,可以在没有许多这些细节的情况下实践本技术。

26.另外,可能未详细示出或描述一些众所周知的结构或功能,以便简明扼要并避免不必要地模糊相关描述。

27.在下面给出的描述中使用的术语旨在以其最广泛的合理方式解释,即使它与本技术的某些特定示例的详细描述一起使用。以下甚至可以强调某些术语,然而,任何旨在以任何受限制的方式解释的术语将在本详细描述部分中明确且具体地定义。

28.本技术公开了一种多相位时钟信号产生电路,图1示出了一个实施例中四相位时钟信号产生电路的示意图。该多相位时钟信号产生电路包括依次串联连接的延迟单元101、第一多相位滤波器102、第一信号转换器103、第二多相位滤波器104、第三多相位滤波器105和第二信号转换器106。

29.所述延迟单元101接收两相位时钟信号号并输出四相位时钟信号到所述第一多相位滤波器。所述第一多相位滤波器102、第二多相位滤波器104和第三多相位滤波器105各自将所述四相位时钟信号的相位误差转换为幅度误差。该电路主要由延迟单元、多级多相位滤波器以及ac信号转cmos信号的电路组成。其中相位的精度由多相位滤波器的级数决定,级数越高,精度越高,同时它的功耗也越大,噪声性能则同时下降。其中相位滤波器纠正了相位信息的同时,产生幅度误差,则由ac信号转cmos信号放大至满摆幅消除。

30.所述延迟单元101接收相位为0

°

和180

°

的两相位时钟信号pll_p、pll_n并输出相位为0

°

、90

°

、180

°

和270

°

的四相位时钟信号。图2示出了一个实施例中延迟单元的示意图,所述延迟单元101包括两路延迟线107、108,每路延迟线107、108分别对一路时钟信号延迟90

°

相位。例如,对于输入的0相位时钟信号p0in延迟90

°

相位,分别输出p0in、p90in,对于输入的180相位时钟信号p180in延迟90

°

相位,分别输出p180in、p270in。

31.所述第一多相位滤波器102、第二多相位滤波器104和第三多相位滤波器105分别为四相位滤波器,图3示出了一个实施例中四相位滤波器的示意图。所述四相位滤波器包括串联的四组rc滤波单元109,每组rc滤波单元分别将所述0

°

、90

°

、180

°

和270

°

的四相位时钟信号p0in、p90in、p180in、p270in中的一路时钟信号的相位误差转换为幅度误差。对于四相位输出,需将rc设置到极点频率相位移动90度附近(90度附近即可,不对频率敏感),以将所述四相位时钟信号的相位误差转换为幅度误差。

32.所述第一信号转换器103和第二信号转换器106各自包括四个转换单元,图4示出了本发明一个实施例中信号转换器的示意图,信号转换器由ac信号转cmos信号。每个转换单元包括反相器inv、电阻器r和电容器c,所述电阻器r的一端连接所述反相器inv的输入端,所述电阻器r的另一端连接所述反相器inv的输出端,所述电容器c的一端耦合到四相位时钟信号p0、p90、p180、p270其中的一路信号,所述电容器c的另一端连接所述反相器inv的输入端。所有信号都满摆幅,所有信号的幅度都一样。所以不存在幅度的差异,因此幅度误差消除。

33.图5示出了经过本技术一个实施例中28ghz输入产生的四相位时钟信号,相位误差在2.3ps。最终校准过后,误差降低到150fs,2.3ps/150fs~=15倍。

34.图6示出了一个实施例中八相位时钟信号产生电路的示意图。该八相位产生电路包括依次串联连接的第一多相位滤波器201、第一信号转换器202、第二多相位滤波器203、第三多相位滤波器204和第二信号转换器205。应当注意,八相位时钟信号产生电路还可以包括连接到第一多相位滤波器201的延迟单元(图中未示出),所述延迟单元接收相位为0

°

和180

°

的四相位时钟信号并输出相位为0

°

、90

°

、180

°

和270

°

的四相位时钟信号。延迟单元可以接收图1所示的四相位时钟信号产生电路输出的高精度四相位时钟信号。延迟单元的结构可以参考图2所示,所述延迟单元包括四路延迟线,每路延迟线分别对一路时钟信号延迟90

°

相位。

35.所述第一多相位滤波器201将所述四相位时钟信号的相位误差转换为幅度误差。第二多相位滤波器203和第三多相位滤波器204各自将所述八相位时钟信号的相位误差转换为幅度误差。所述第一多相位滤波器201为四相位滤波器。第二多相位滤波器203和第三多相位滤波器204分别为八相位滤波器,图7示出了一个实施例中八相位滤波器的示意图。所述八相位滤波器包括串联的八组rc滤波单元,每组rc滤波单元分别将所述0

°

、45

°

、90

°

、135

°

、180

°

、225

°

、270

°

和315

°

的八相位时钟信号中的一路时钟信号的相位误差转换为幅度误差。对于8相位输出,需将rc设置到极点频率相位移动45度(附近即可,不对频率敏感),以将所述八相位时钟信号的相位误差转换为幅度误差。

36.在一个实施例中,所述第一信号转换器202和第二信号转换器206各自包括八个转换单元,每个转换单元的结构可以参考图4所示,在此不做赘述。所述第一信号转换器202和第二信号转换器205各自将所述八相位时钟信号的幅度误差放大到满摆幅从而消除所述幅度误差。所有信号都满摆幅,所有信号的幅度都一样。所以不存在幅度的差异,因此幅度误差消除。

37.需要说明的是,在本专利的申请文件中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。本专利的申请文件中,如果提到根据某要素执行某行为,则是指至少根据该要素执行该行为的意思,其中包括了两种情况:仅根据该要素执行该行为、和根据该要素和其它要素执行该行为。多个、多次、多种等表达包括2个、2次、2种以及2个以上、2次以上、2种以上。

38.本说明书包括本文所描述的各种实施例的组合。对实施例的单独提及(例如“一个实施例”或“一些实施例”或“优选实施例”)不一定是指相同的实施例;然而,除非指示为是互斥的或者本领域技术人员很清楚是互斥的,否则这些实施例并不互斥。应当注意的是,除非上下文另外明确指示或者要求,否则在本说明书中以非排他性的意义使用“或者”一词。

39.在本说明书提及的所有文献都被认为是整体性地包括在本技术的公开内容中,以便在必要时可以作为修改的依据。此外应理解,以上所述仅为本说明书的较佳实施例而已,并非用于限定本说明书的保护范围。凡在本说明书一个或多个实施例的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本说明书一个或多个实施例的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。