1.本发明属于先进电子封装技术领域,涉及一种多芯片桥接集成结构及其组装方法。

背景技术:

2.现有的冯

·

诺依曼计算系统采用运算和存储分离的架构,计算单元要先从内存中读取数据,计算完成后,再将新数据存回内存。数据在存储单元和计算单元间的传输速度跟不上数据计算速度,且传输功耗远大于计算能耗,被称为是计算和存储之间的“存储墙”和“功耗墙”问题。随着图像处理、人工智能的发展,运算复杂度提高,需要运算的数据量急剧增加,大量数据需要在计算单元和存储单元间频繁移动,迫切需要合适的手段来提高数据移动效能,减小数据移动开销。采用先进的封装方式把存储和计算芯片封装在一起,使其极度邻近,极大的缩短两者间的连线长度,同时进一步增加连线数量,提升数量搬运速度,降低搬运能耗,可有效缓解和弱化“存储墙”和“功耗墙”问题。目前已经有将处理器芯片和存储器芯片封装在同一有机载板,或同一tsv硅转接基板上的2d和2.5d封装方案,将计算芯片和存储芯片距离拉近,来实现算存性能和能效的大幅提升。

3.随着处理器内核数增多,处理器芯片尺寸和需配置的存储器片数增大,现有的2.5d封装方案,不但要求2.5d tsv硅转接基板有更高的互连布线密度,还要求有更大的转接基板尺寸,将导致转接基板良率降低,成本增加,另外,随着多个处理器并行计算处理需求的增加,上述问题更加严重,需要一种更低成本,可扩展的封装集成解决方案。现有的封装集成结构如图6所示,所有芯片是全部键合在转接板上的,导致转接板的面积至少要大于所有其上芯片面积之和,转接板面积的扩大直接带来制备难度的提高,制备良率的下降,以及成本的上升;另外,现有封装集成结构,如果要阵列式扩展的话,转接板面积需要成倍的相应扩展,还可能超出转接板的工艺制备能力,完全不可实现,并且现有封装集成结构中,所有转接板上的芯片,无论是芯片间互连,还是芯片与封装基板间的互连,都需要通过转接板,互连信号的扇出和电源供电往往只能相互妥协。

技术实现要素:

4.本发明的目的在于解决现有技术中由于处理器芯片尺寸和需配置的存储器片数增大,要求转接板的面积至少要大于其上芯片面积之和,并且具有更高的布线密度和更大的尺寸,但是会使转接基板良率降低和成本增加,导致转接板工作可靠性不足的问题,提供一种多芯片桥接集成结构及其组装方法。

5.为达到上述目的,本发明采用以下技术方案予以实现:

6.一种多芯片桥接集成结构,包括若干电路单元,电路单元包括第一芯片、第二芯片、转接板、封装基板、第一微凸点、第二微凸点、焊球和焊柱;

7.所述第一芯片通过第一微凸点构成的第一微凸点阵列键合在转接板的上表面,所述第二芯片包括转接板连接部和封装基板连接部,第二芯片转接板连接部的外引脚通过第

二微凸点构成的第二微凸点阵列键合在转接板的上表面,第二芯片封装基板连接部的外引脚通过焊柱构成的焊柱阵列键合在封装基板上,转接板的下表面通过焊球构成的焊球阵列键合在封装基板上,所述第一芯片和第二芯片之间的电互连由第一微凸点、转接板上的金属布线和第二微凸点构成的通路实现,所述转接板上开设有若干导电通道。

8.本发明的进一步改进在于:

9.所述第二芯片转接板连接部位于第二芯片的一端,第二芯片的一端外引脚通过第二微凸点阵列键合在转接板的上表面;第二芯片封装基板连接部位于第二芯片的另一端,第二芯片的另一端外引脚通过焊柱阵列键合在封装基板上。

10.所述第二芯片转接板连接部位于第二芯片相对应的两端,第二芯片相对应的两端外引脚分别通过第二微凸点阵列键合在两个相邻的转接板上表面;第二芯片封装基板连接部位于第二芯片的中间部位,第二芯片的中间部位外引脚通过焊柱阵列键合在封装基板上。

11.所述转接板中设置有埋置芯片,埋置芯片的外引脚与第一芯片的外引脚相对设置,埋置芯片与第一芯片之间通过第一微凸点实现电互连,埋置芯片与第二芯片之间通过连接板上的金属布线和第二微凸点实现电互连。

12.所述转接板的厚度为50μm~200μm,第一微凸点和第二微凸点的直径为10μm~100μm,焊球的直径为100μm~300μm,焊柱的直径为100μm~300μm。

13.所述焊柱阵列的阵列间距大于第二微凸点阵列的阵列间距,所述第一微凸点阵列的阵列间距和第二微凸点阵列的阵列间距均小于焊球阵列的阵列间距。

14.所述转接板为无机转接基板或有机转接基板。

15.所述第一芯片为处理类芯片。

16.所述第二芯片为存储器芯片。

17.一种多芯片桥接集成结构的组装方法,包括以下步骤:

18.通过回流工艺或热压工艺将转接板微组装在封装基板上,通过焊球构成的焊球阵列实现转接板和封装基板之间的电互连;

19.通过回流工艺或热压工艺将第一芯片微组装在转接板的上表面;

20.通过回流工艺或热压工艺将第二芯片微组装在转接板和封装基板的上表面。

21.与现有技术相比,本发明具有以下有益效果:

22.本发明中的多芯片桥接集成结构,将第一芯片通过第一微凸点构成的第一微凸点阵列键合在转接板上,第二芯片的一部分通过第二微凸点阵列键合在转接板上,另一部分通过焊柱键合在封装基板上,第一芯片和第二芯片之间通过第一微凸点、转接板上的金属布线和第二微凸点构成的电互连通路实现,构成独立的电路单元。在芯片结构需要阵列式扩展时,电路单元能够沿横向和/或纵向扩展,转接板的面积不需要成倍的相应扩展就能实现芯片之间的通信,能够提高转接板在工作过程中的可靠性,保证转接板良率,并且降低成本。

23.进一步的,在转接板的内部埋入埋置芯片,埋置芯片的外引出管脚与第一芯片的外引出管脚相对设置,埋置芯片与第一芯片之间通过第一微凸点实现电互连,埋置芯片与第二芯片之间通过连接板上的金属布线和第二微凸点实现电互连,可以保证埋置芯片与第一芯片和第二芯片件的电互连有更短的互连路径、更小的互连延时和更高的互连带宽。

24.进一步的,多芯片桥接集成结构在能保证第一芯片和第二芯片之间短距离、高密度、高带宽互连的同时,减低了对封装基板上表面焊盘共面性要求,使得封装基板成本更低,键合工艺难度更小。

附图说明

25.为了更清楚的说明本发明实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

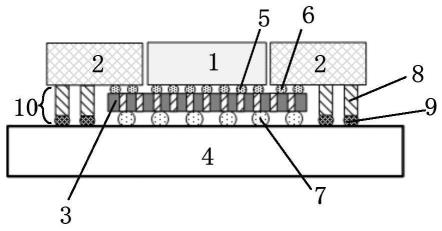

26.图1为本发明的多芯片桥接集成结构一实施例剖面示意图;

27.图2为本发明的多芯片桥接集成结构一实施例拓展结构示意图;

28.图3为本发明的包含埋置芯片的多芯片桥接集成结构剖面示意图;

29.图4为本发明的多芯片桥接集成结构另一实施例剖面示意图;

30.图5为本发明的多芯片桥接集成结构另一实施例拓展结构示意图;

31.图6为现有技术中的芯片集成结构。

32.其中:1-第一芯片,2-第二芯片,3-转接板,4-封装基板,5-第一微凸点,6-第二微凸点,7-焊球,8-金属柱,9-焊帽,10-焊柱,11-埋置芯片;12-导电通道。

具体实施方式

33.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。

34.因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

35.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

36.在本发明实施例的描述中,需要说明的是,若出现术语“上”、“下”、“水平”、“内”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该发明产品使用时惯常摆放的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

37.此外,若出现术语“水平”,并不表示要求部件绝对水平,而是可以稍微倾斜。如“水平”仅仅是指其方向相对“竖直”而言更加水平,并不是表示该结构一定要完全水平,而是可以稍微倾斜。

38.在本发明实施例的描述中,还需要说明的是,除非另有明确的规定和限定,若出现术语“设置”、“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆

卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

39.下面结合附图对本发明做进一步详细描述:

40.本发明中的一种多芯片桥接集成结构,包括第一芯片1、第二芯片2、转接板3、封装基板4、第一微凸点5、第二微凸点6、焊球7和焊柱10;所述第一芯片1通过第一微凸点5构成的第一微凸点阵列键合在转接板3的上表面,所述第二芯片2包括转接板连接部和封装基板连接部,第二芯片2转接板连接部的外引脚通过第二微凸点6构成的第二微凸点阵列键合在转接板3的上表面,第二芯片2封装基板连接部的外引脚通过焊柱10构成的焊柱阵列键合在封装基板4上,转接板3的下表面通过焊球7构成的焊球阵列键合在封装基板4上,所述第一芯片1和第二芯片2之间通过第一微凸点5、转接板3上的金属布线和第二微凸点6构成的电互连通路实现,所述转接板3上开设有若干导电通道12。

41.实施例1:

42.参见图1,为本发明的多芯片桥接集成结构一实施例剖面示意图,第一芯片1的所有外引脚通过第一微凸点5构成的第一微凸点阵列键合在转接板3的上表面上,第二芯片2一端的外引脚通过第二微凸点6构成的第二微凸点阵列键合在转接板3的上表面上,第一微凸点5和第二微凸点6的直径和高度相同或相近,第一微凸点5构成的第一微凸点阵列的阵列间距与第二微凸点6构成的第二微凸点阵列间距可以相同或相近,也可以不同;第二芯片2另一端的外引脚通过焊柱10构成的焊柱阵列键合在封装基板4的上表面上,焊柱10由金属柱8以及位于金属柱顶端的焊帽9构成,焊柱10的直径大于第二微凸点6的直径,焊柱10构成的焊柱阵列的阵列间距大于第二微凸点6构成的第二微凸点阵列的阵列间距,使得焊柱10构成的焊柱阵列在与封装基板4上表面相应焊盘阵列键合时,对封装基板4上表面相应焊盘的焊盘密度和焊盘共面性要求低于第二微凸点6构成的第二微凸点阵列对转接板3上表面相应引脚焊盘的焊盘密度和焊盘共面性要求。转接板3的下表面引脚通过焊球7构成的焊球阵列键合在封装基板4的上表面上,焊球7的直径和高度大于第一微凸点5和第二微凸点6的直径和高度,焊球7构成的焊球阵列的阵列间距大于第一微凸点5和第二微凸点6分别构成的第一微凸点阵列和第二微凸点阵列的阵列间距,使得焊球7构成的焊球阵列在与封装基板4上表面相应焊盘阵列键合时,对封装基板4上表面相应焊盘的焊盘密度和焊盘共面性要求低于第一微凸点5和第二微凸点6分别构成的第一微凸点阵列和第二微凸点阵列对转接板3上表面相应焊盘的焊盘密度和焊盘共面性要求。第一芯片1和第二芯片2之间的电信号互连通过第一微凸点5、转接板3上的金属布线以及第二微凸点6构成的电互连通路实现。

43.第一芯片1优选为处理类芯片,包括cpu、gpu、dpu、npu、dsp、fpga或asic芯片等处理类芯片,但不限于此;第二芯片2优选为存储类芯片,包括ddr和sdram等,但不限于此。

44.转接板3包括xy平面方向上的金属布线结构、z方向上的导电通道结构以及位于上表面的上表面引脚焊盘和位于下表面的下表面引脚焊盘,上表面引脚焊盘和下表面引脚焊盘通过金属布线结构和导电通道实现电互连。转接板3上表面引脚焊盘直径和间距小于下表面引脚焊盘直径和间距,所以转接板3起到了将微小尺寸、窄间距的微凸点阵列,即第一微凸点5和第二微凸点6分别构成的第一微凸点阵列和第二微凸点阵列,转换成较大尺寸、更宽间距的焊球阵列的作用,即焊球7构成的焊球阵列,以降低对封装基板4相应区域的焊

盘密度和焊盘共面性要求。转接板3可以是以无机材料为基础材料的无机转接板基板,包括硅转接板、玻璃转接板或陶瓷转接板,但不限于此;转接板3也可以是以有机材料为基础材料的有机转接基板,包括pi转接板、abf转接板、包封树脂转接板或液晶转接板,但不限于此。转接板3也可以是具备上下表面引脚焊盘电互连能力的有源功能芯片,转接板3可以集成无源器件和无源网络。

45.转接板3的优选材料为硅,由于硅材料具有优良的电、热以及力学性能,电互连密度高,硅晶圆生产供应链成熟度高,此时穿透转接板3的z方向导电通道12为tsv通孔(through-silicon-via)。封装基板4可以是有机封装基板,也可以是陶瓷封装基板,但不限于此。

46.转接板3的厚度优选为50μm~200μm,第一微凸点5和第二微凸点6的直径范围优选为10μm~100μm,焊球7的直径范围优选为100μm~300μm,焊柱10的直径范围优选为100μm~300μm。

47.参见图2,为实施例一种所示多芯片桥接结构构成的阵列结构俯视示意图,将图1中所示结构视为一个单元结构,该结构沿横向和纵向扩展,得到阵列结构,图2中为2*2的阵列结构。第一芯片1优选处理类芯片,第二芯片2优选存储类芯片。第一芯片1及其周围的第二芯片2以及其下方的转接板3构成了一组相对独立的单元结构,该单元结构在封装基板4上沿横向和纵向可以扩展成不同行数、列数的阵列结构,即该单元结构具有可复用性。转接板3不需要随着阵列行数和列数的扩展而扩展自身尺寸,即不需要随着行列数的变化而变化尺寸,减小了转接板3的设计、制造和测试成本。在每个单元结构中,处理类第一芯片1可配置8个存储类第二芯片2,第一芯片1和第二芯片2之间的数据读写通过该单元的转接板3上的互连线实现,在实现大存储容量的同时,可保证更短的互连路径,解决存储带宽问题。

48.第一芯片1的所有外引脚凸点键合在转接板3上表面,使得处理类芯片的所有对外引脚都通过转接板3上表面的第一微凸点5、导电通道12、以及下表面的焊球7与封装基板4电连接,第一微凸点5的尺寸小于焊球7的尺寸,第一微凸点5阵列的密度高于焊球7阵列密度,一方面更好的满足第一芯片1的高密度窄节距外引脚阵列发展需求,另一方面降低了对封装基板4上表面焊盘共面性的要求。第二芯片2有一部分位于转接板3上方,另一部分位于转接板3之外。第二芯片2通过其位于转接板3上方部分的焊盘通过第二微凸点6与转接板3形成电互连,第二芯片2通过其位于转接板3外部分的焊盘通过焊柱10与封装基板4形成电互连;焊柱10的直径和长度远大于第二微凸点6的直径和高度,第二芯片2与第一芯片1靠近,其间的电互连通过第二微凸点6、转接板3上走线、第一微凸点5的串联路径实现,可以保证第二芯片2与第一芯片1间的电互连有更短的互连路径,更小的互连延时,更高的互连带宽,提高第二芯片2与第一芯片1间的数据读写能效。第二微凸点6可对应存储类芯片2与第一芯片1间存在互连关系的引脚,特别是对互连速度和互连带宽有要求的引脚,包括数据引脚、地址引脚,时钟引脚等,但不限于此,焊柱10可对应第二芯片2中不与第一芯片1直接互连的其他引脚,包括电源引脚、地引脚、上下拉偏置引脚、控制引脚等,但不限于此,这样第二芯片2与第一芯片1从不同路径供电,还能避免两者电源供电网络间的干扰,减小电源完整性问题,同时较大直径的焊柱10可保证更大的供电电流、更小的电源阻抗,以提供更优的电源供电。

49.实施例2:

50.参见图3,为本发明中包含埋置芯片的多芯片桥接集成结构剖面示意图,转接板3可以局部埋入埋置芯片11,埋置芯片11可以是有源功能芯片,无源芯片,如电容芯片,集成无源网络芯片、传感芯片等,但不限于此。埋置芯片11的外引出管脚与第一芯片1的外引出管脚面对面相对,埋置芯片11与第一芯片1和第二芯片2间的电互连分别通过第一微凸点5和第二微凸点6实现,可以保证埋置芯片11与第一芯片1和第二芯片2间的电互连有更短的互连路径,更小的互连延时,更高的互连带宽。本实施例能够与实施例1或实施例3中的其他特征组合

51.实施例3:

52.参见图4,为本发明的多芯片桥接集成结构另一实施例剖面示意图,第一芯片1的所有外引脚通过第一微凸点5构成的第一微凸点阵列键合在转接板3上表面上,第二芯片2相对两端的外引脚通过第二微凸点6构成的第二微凸点阵列分别键合在相邻的转接板3上表面两端,第二芯片2中部的外引脚通过焊柱10构成的焊柱阵列键合在封装基板4上表面上,转接板3的下表面引脚通过焊球7构成的焊球阵列键合在封装基板4上表面上,第一芯片1和相邻第二芯片2间的电信号互连通过第一微凸点5、转接板3上的金属布线以及第二微凸点6构成的电互连通路实现。

53.参见图5,为另一实施例的多芯片桥接结构构成的阵列模块结构示意图。所示结构沿横向和纵向扩展,可得到如图5所示的阵列结构,为简明起见,图5仅画出局部的阵列结构。

54.第一芯片1优选处理类芯片,第二芯片2优选存储类芯片。相邻的两个第一芯片1共享其中间的第二芯片2,可以是分区共享,也可以是对相同存储区共享。相邻的两个第一芯片1间的信息交互可以通过其中间共享的第二芯片2来实现,该结构更能适用于算存一体结构、神经网络计算结构,以满足人工智能、无人驾驶等应用场景对大规模并行计算,高带宽大容量内存和极致算力的需求。

55.各实施例中所述结构的微组装流程包括以下步骤:

56.首先,在封装基板4上表面上微组装转接板3,通过焊球7构成的焊球阵列实现转接板3和封装基板4之间的电互连。微组装工艺可采用回流工艺,也可以采用热压工艺,但不限于此。

57.然后,可以同时完成第一芯片1在转接板3上表面,以及第二芯片2在转接板3上表面和封装基板4上表面上的微组装;也可以先完成第一芯片1在转接板3上表面的微组装,再完成第二芯片2在转接板3上表面和封装基板4上表面上的微组装。微组装工艺可采用回流工艺,也可采用热压工艺,但不限于此。

58.本发明中的多芯片桥接集成结构,将第一芯片1的所有外引脚通过第一微凸点5构成的第一微凸点阵列键合在转接板3上表面上,第二芯片2相对两端的外引脚通过第二微凸点6构成的第二微凸点阵列分别键合在相邻的转接板3上表面两端,第二芯片2中部的外引脚通过焊柱10构成的焊柱阵列键合在封装基板4上表面上,转接板3的下表面引脚通过焊球7构成的焊球阵列键合在封装基板4上表面上,第一芯片1和相邻第二芯片2间的电信号互连通过第一微凸点5、转接板3上的金属布线以及第二微凸点6构成的电互连通路实现。在芯片结构需要阵列式扩展时,电路单元能够沿横向和/或纵向扩展,转接板的面积不需要相应扩展就能实现芯片之间的通信,且相邻的两个第一芯片1共享其中间的第二芯片2,相邻的两

个第一芯片1间的信息交互可以通过其中间共享的第二芯片2来实现,该结构更能适用于算存一体结构、神经网络计算结构,以满足人工智能、无人驾驶等应用场景对大规模并行计算,高带宽大容量内存和极致算力的需求。

59.以上仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。