一种多段式vco在不同频率误差场景下的校准方法及电路

技术领域

1.本发明涉及射频微波技术领域,尤其涉及到一种多段式vco在不同频率误差场景下的校准方法及电路。

背景技术:

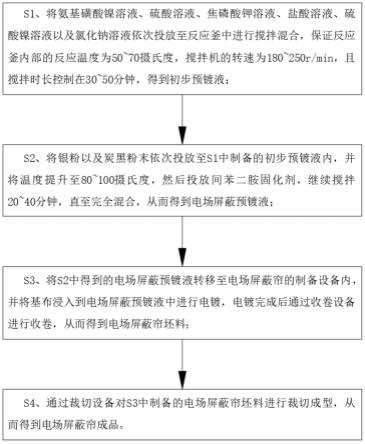

2.锁相环电路是一个闭环系统,该系统最关键的三个器件是:鉴相器、环路滤波器、vco。vco是该电路的重要组成部分,近年来有一种多段式vco开始应用于锁相环,如图1所示。

3.频率多段式vco与传统宽带vco相比,具有更低的相位噪声。频率多段式vco的最大特点是将频率分成若干段,因此选择合适的频段组合完全覆盖所有频段是电路设计的关键点。但是存在一个无法避免的缺点,由于材料、工艺等的限制,不同批次的产品的频段划分情况会有差异,因此需要针对其不同频段进行频率校准。

4.现有的基于多段式vco的锁相环频率校准电路原理框图如图2,现有的频率校准方法可以对多段式vco或常规宽带vco进完成频率校准,具体内容见专利:cn202110448664.4。对该专利的频率校准方法流程图进行整理,可得图3所示的现有基于多段式vco的锁相环频率校准方法简图。

5.对于多段式vco,如果加工制造的误差已经超过某一频段产品手册标称最高频率和标称最低频率之差,某一频段的实际最高频率和实际最低频率与产品手册该频段标称最高频率和标称最低频率的相对位置关系存在图4所示意的几种场景(可能存在其他场景未全部列举,但不影响阐述本发明专利的思想)。图4中多段式vco某一频段实际最低频率和实际最高频率分别用sd和sg表示,多段式vco某一频段标称最低频率和标称最高频率分别用用bd和bg表示。定义span[xx,xx]为区间[xx,xx]的长度,物理意义为xx和xx的频率带宽,xx可以为sd、sg、bd、bg的任意变量。

[0006]

图4场景a中,多段式vco的实际最低频率和实际最高频率包含于标称最低频率和标称最高频率之间,即并且实际最低频率和实际最高频率的频率带宽远小于标称最低频率和标称最高频率的频率带宽(小于两倍以上认为是远小于),即span[sd,sg]<2

×

span[bd,bg],这种场景下,采用现有校准方法,选择的比例因子如果太大,会一直执行图3中频段n最低频率校准子流程或频段n最高频率校准子流程,无法得出正确的频率校准值。

[0007]

图4场景b和场景c中,多段式vco的实际最低频率和实际最高频率的区间与标称最低频率和标称最高频率的区间没有交集,即这种场景下,无论比例因子如何选择,总会有一个频率值无法进行校准:场景b中的最低频率校准会一直执行图3的频段n最低频率校准子流程,场景c中的最高频率校准会一直执行图3的频段n最高频率校准子流程,如果不打断程序的,将一直执行下去。

[0008]

因此,需要提供一种多段式vco在不同频率误差场景下的校准方法,以消除已有多

段式vco的锁相环频率校准方法对于上述应用场景校准时存在的无法进行准确校准的情况。

技术实现要素:

[0009]

本发明的主要目的在于提供一种多段式vco在不同频率误差场景下的校准方法及电路,旨在解决已有多段式vco的锁相环频率校准方法对于特殊应用场景校准时存在的无法进行准确校准的技术问题。

[0010]

为实现上述目的,本发明提供一种多段式vco在不同频率误差场景下的校准方法,所述方法包括以下步骤:

[0011]

s101:赋值n=n 1,控制单元的控制器向多段式vco发送指令,控制多段式vco工作在频段n;

[0012]

s102:设置变量k,k为整数,初始值k=0;

[0013]

s103:赋值k=k 1;

[0014]

s104:控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为:f

max_nk

=f

max_n-(f

max_n-f

min_n

)

×a×

k;

[0015]

s105:鉴相器向控制单元上报锁相环是否锁定的状态;

[0016]

s106:控制单元的控制器判断锁相环是否锁定,若是,将已锁定的频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最高频率f

max_n

;若否,执行步骤s107;

[0017]

s107:判断f

max_nk

<f

min

是否成立,若是,执行步骤s108;若否,则执行步骤s103;

[0018]

s108:赋值k=-1;

[0019]

s109:赋值k=k 1;

[0020]

s110:控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_nk

=f

max_n

(f

max_n-f

min_n

)

×a×

k;

[0021]

s111:鉴相器向控制单元上报锁相环是否锁定的状态;

[0022]

s112:控制单元的控制器判断锁相环是否锁定,若是,执行步骤s115;若否,执行步骤s113;

[0023]

s113:判断f

min_nk

>f

max

是否成立,若是,执行步骤s114;若否,执行步骤s109;

[0024]

s114:按第一预设比例缩小a,执行步骤s103;

[0025]

s115:将已锁定的频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最低频率f

min_n

;

[0026]

s116:设置变量m,m为整数,初始值m=-1;

[0027]

s117:赋值m=m 1;

[0028]

s118:控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_nm

=f

min_n

(f

max_n-f

min_n

)

×b×

m;

[0029]

s119:鉴相器向控制单元上报锁相环是否锁定的状态;

[0030]

s120:控制单元的控制器判断锁相环是否锁定,若是,执行步骤s117;若否,执行步骤s121;

[0031]

s121:将距离未锁定最近的一次的已锁定频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最高频率f

max_n

;

[0032]

可选的,在步骤s121或步骤s1065之后,所述方法还包括:判断所有频段是否全部校准完成,若是,校准结束;若否,执行步骤s101。

[0033]

此外,为了实现上述目的,本技术还提供一种多段式vco在不同频率误差场景下的校准方法,所述方法包括以下步骤:

[0034]

s201:赋值n=n 1,控制单元的控制器向多段式vco发送指令,控制多段式vco工作在频段n;

[0035]

s202:设置变量k,k为整数,初始值k=0;

[0036]

s203:赋值k=k 1;

[0037]

s204:控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为:f

max_nk

=f

max_n-(f

max_n-f

min_n

)

×a×

k;

[0038]

s205:鉴相器向控制单元上报锁相环是否锁定的状态;

[0039]

s206:控制单元的控制器判断锁相环是否锁定,若是,将已锁定的频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最高频率f

max_n

;若否,执行步骤s203;

[0040]

s207:设置变量m,m为整数,初始值m=0;

[0041]

s208:m=m 1;

[0042]

s209:控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_nm

=f

min_n

(f

max_n-f

min_n

)

×b×

m;

[0043]

s210:鉴相器向控制单元上报锁相环是否锁定的状态,若是,执行步骤s211;若否,执行步骤s212;

[0044]

s211:将已锁定的频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最低频率f

min_n

;

[0045]

s212:判断f

min_nm

>f

max

是否成立,若是,执行步骤s213;若否,执行步骤s208;

[0046]

s213:赋值m=-1;

[0047]

s214:赋值m=m 1;

[0048]

s215:控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_nm

=f

min_n-(f

max_n-f

min_n

)

×b×

m;

[0049]

s216:控制单元的控制器判断锁相环是否锁定,若是,执行步骤s219;若否,执行步骤s217;

[0050]

s217:判断f

min_nm

<f

min

是否成立,若是,执行步骤s218;否则,执行步骤s214;

[0051]

s218:按一定比例缩小b,执行步骤s207;

[0052]

s219:赋值m=m 1;

[0053]

s220:控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_nm

=f

min_n-(f

max_n-f

min_n

)

×b×

m;

[0054]

s221:鉴相器向控制单元上报锁相环是否锁定的状态;

[0055]

s222:控制单元的控制器判断锁相环是否锁定,若是,执行步骤s223;若否,执行步骤s219;

[0056]

s223:将距离未锁定最近的一次的已锁定频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最低频率f

min_n

。

[0057]

可选的,所述步骤s211或步骤s223之后,所述方法还包括:判断所有频段是否全部

校准完成,若是,校准结束;若否,执行步骤s201。

[0058]

此外,为了实现上述目的,本技术还提供一种多段式vco在不同频率误差场景下的校准电路,所述电路包括鉴相器、环路滤波器、多段式vco和控制单元,所述控制单元包括控制器和存储器,所述电路在执行多段式vco在不同频率误差场景下的校准时,执行如上所述的多段式vco在不同频率误差场景下的校准方法。

[0059]

本发明具有以下有益效果:

[0060]

1、针对多段式vco由于材料、工艺等因素导致的分段频率偏移,本专利提出的校准方法可以解决“a批次选择的频段组合可以完全覆盖a批次,但无法完全覆盖b批次的产品。”的问题。

[0061]

2、针对多段式vco由于材料、工艺等因素导致的分段频率偏移,本专利提出的校准方法可以解决“同一批次的产品,在高温、低温、常温下的频段划分情况也会有漂移。”的问题。

[0062]

3、本专利提出的多段式vco频率校准方法,有益于多段式vco在工程应用广泛使用。

[0063]

4、本专利提出的多段式vco频率校准方法,有益于增加多段式vco频率校准的应用场景,可以解决多段式vco在特殊情况下频率无法校准的问题。

[0064]

5、本专利提出的多段式vco频率校准方法,可以不需提前获知多段式vco某一频段的标称最低频率和标称最高频率等信息。

附图说明

[0065]

图1是一种典型单环锁相环原理框图。

[0066]

图2是现有基于多段式vco的锁相环频率校准电路原理框图。

[0067]

图3是现有基于多段式vco的锁相环频率校准方法示意图。

[0068]

图4是多段式vco实际频率与标称频率的不同应用场景示意图。

[0069]

图5是本技术对频段n最高频率校准子流程的补充方法示意图。

[0070]

图6是本技术对频段n最低频率校准子流程的补充方法示意图。

[0071]

图7是具体实例中多段式vco频段3的频率分布情况示意图。

[0072]

本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

[0073]

应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

[0074]

目前,在相关技术领域,已有多段式vco的锁相环频率校准方法对于特殊应用场景校准时存在无法进行准确校准的问题。

[0075]

为了解决这一问题,提出本发明的多段式vco在不同频率误差场景下的校准方法的各个实施例。本发明提供的多段式vco在不同频率误差场景下的校准方法通过对频段n最高频率校准子流程的补充和对频段n最低频率校准子流程的补充,保证不同批次间多段式vco、全温(高温、低温、常温)状态下同批次多段式vco频率分段均能完全覆盖宽带频率范围,并且增加了多段式vco的锁相环频率校准方法的应用场景,校准方法对多段式vco的已知信息要求降低。

[0076]

本发明实施例提供了一种多段式vco在不同频率误差场景下的校准方法,参照图5和图6,图5和图6为本发明多段式vco在不同频率误差场景下的校准方法实施例的流程示意图。

[0077]

本实施例中,所述多段式vco在不同频率误差场景下的校准方法包括以下步骤:

[0078]

步骤s1:按图2所示电路逻辑关系连接电路,并按现有方法执行多段式vco频率n最高频率校准子流程;

[0079]

步骤s2:频段n最高频率校准子流程的补充方法的工作过程;

[0080]

步骤s3:按现有方法执行多段式vco频率n最低频率校准子流程;

[0081]

步骤s4:频段n最低频率校准子流程的补充方法的工作过程。

[0082]

在一些可能的实施方式中,需要进行步骤s2的校准过程,如图5所示,所述步骤s2具体包括以下步骤:

[0083]

步骤s201:判断f

max_nk

<f

min

是否成立:如果否,则进入步骤s1,继续按现有方法执行;如果是,则进入步骤s202。

[0084]

步骤s202:赋值k=-1。

[0085]

步骤s203:赋值k=k 1。

[0086]

步骤s204:控制单元的控制器向鉴相器发送指令,鉴相器输出频率通过公式3计算。

[0087]

步骤s205:鉴相器向控制单元上报锁相环是否锁定的状态。

[0088]

步骤s206:控制单元的控制器判断锁相环是否锁定。如果未锁定,进入步骤s207;如果锁定,进入步骤s209。

[0089]

步骤s207:判断f

min_nk

>f

max

是否成立:如果否,则进入步骤s203;如果是,则进入步骤s208。

[0090]

步骤s208:按一定比例缩小a,例如,a=a/10,然后进入步骤s1,继续按现有方法执行。

[0091]

步骤s209:将已锁定的频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最低频率f

min_n

。

[0092]

步骤s210:设置变量m,m为整数,初始值m=-1。

[0093]

步骤s211:赋值m=m 1。

[0094]

步骤s212:控制单元的控制器向鉴相器发送指令,鉴相器输出频率通过公式4计算。

[0095]

步骤s213:鉴相器向控制单元上报锁相环是否锁定的状态。

[0096]

步骤s214:控制单元的控制器判断锁相环是否锁定。如果未锁定,进入步骤s115;如果锁定,进入步骤s211。

[0097]

步骤s215:将距离未锁定最近的一次的已锁定频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最高频率f

max_n

。

[0098]

在一些可能的实施方式中,需要进行步骤s4的校准过程,如图6所示,所述步骤s4具体包括以下步骤:

[0099]

步骤s401:判断f

min_nm

>f

max

是否成立:如果否,则进入步骤s3,继续按现有方法执行;如果是,则进入步骤s402。

[0100]

步骤s402:赋值m=-1。

[0101]

步骤s403:赋值m=m 1。

[0102]

步骤s404:控制单元的控制器向鉴相器发送指令,鉴相器输出频率通过公式5计算。

[0103]

步骤s405:鉴相器向控制单元上报锁相环是否锁定的状态。

[0104]

步骤s406:控制单元的控制器判断锁相环是否锁定。如果未锁定,进入步骤s407;如果锁定,进入步骤s409。

[0105]

步骤s407:判断f

min_nm

<f

min

是否成立:如果否,则进入步骤s303;如果是,则进入步骤s408。

[0106]

步骤s408:按一定比例缩小b,例如,b=b/10,然后进入步骤s3,继续按现有方法执行。

[0107]

步骤s409:赋值m=m 1。

[0108]

步骤s410:控制单元的控制器向鉴相器发送指令,鉴相器输出频率通过公式5计算。

[0109]

步骤s411:鉴相器向控制单元上报锁相环是否锁定的状态。

[0110]

步骤s412:控制单元的控制器判断锁相环是否锁定。如果未锁定,进入步骤s413;如果锁定,进入步骤s409。

[0111]

步骤s413:将距离未锁定最近的一次的已锁定频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最低频率f

min_n

。

[0112]

针对以上过程需要说明的是:步骤s208和步骤s408对a和b缩小的程度可以根据实际情况进行选择,本文列举了“/10”这一种情况,也可以选择“/2”、“/4”、“/8”等,缩小或增大比例因子并不影响本技术的核心思想。

[0113]

需要说明的是,在本实施例中,公式字符具有如下含义:

[0114]

定义1:vco选段控制码:选择分段vco工作于某个频段的码值。

[0115]

定义2:f

min_n

:多段式vco频段n的产品手册标称的最低频率,该频率属于未校准的初始最低频率。例如频段3的产品手册标称的最低频率为f

min_3

。

[0116]

定义3:f

max_n

:多段式vco频段n的产品手册标称的最高频率,该频率属于未校准的初始最高频率。

[0117]

定义4:f

max_n

:多段式vco频段n的校准后的最高频率。

[0118]

定义5:f

min_n

:多段式vco频段n的校准后的最低频率。

[0119]

定义6:f

min

:多段式vco全频段标称最低频率。

[0120]

定义7:f

max

:多段式vco全频段标称最高频率。

[0121]

定义8:图5和图6中“n=n 1,k=k 1,m=m 1,a=a/10,b=b/10”中的“=”表示运算并且赋值,不代表该公式一定为等式。

[0122]

公式1:f

max_nk

=f

max_n-(f

max_n-f

min_n

)

×a×k[0123]

公式2:f

min_nm

=f

min_n

(f

max_n-f

min_n

)

×b×m[0124]

公式3:f

min_nk

=f

max_n

(f

max_n-f

min_n

)

×a×k[0125]

公式4:f

max_nm

=f

min_n

(f

max_n-f

min_n

)

×b×m[0126]

公式5:f

min_nm

=f

min_n-(f

max_n-f

min_n

)

×b×m[0127]

其中,f

max_nk

、f

min_nm

、f

min_nk

、f

max_nm

为校准过程的中间频率值;

[0128]

k和m为校准次数,属于校准过程的中间变量;

[0129]

a和b为比例因子,a∈[0,1],b∈[0,1],a或b越小,校准后的频率值越接近实际值,但此时校准次数k或m会增加,校准时间变长;例如对某款多段式vco,选择a或b的值为5%~10%(不限于该值),兼顾校准的准确度与校准时间。a和b的取值可以相同,也可以不同。

[0130]

需要说明的是,图5所示的方法是对频段n最高频率校准子流程的补充方法,如果某些场景下,程序进入到该方法中,且不会因为比例因子a太大而跳出该段方法,使用该方法先校准得到频段n的最低频率,然后再校准得到频段n的最高频率。

[0131]

图6所示的方法是对频段n最低频率校准子流程的补充方法,如果某些场景下,程序进入到该方法中,且不会因为比例因子b太大而跳出该段方法,此时校准后的频段n最高频率已经通过图6中的现有方法(频段n最高频率校准子流程)得到,只需要使用图6中本实施例提出的方法校准得到频段n的最低频率即可。

[0132]

图5所示的方法和图6所示的方法内核可以设计成基本相同,但为了节约资源,没有必要。导致它们之间差别的一个重要因素是:频段n最高频率和频段n最低频率的校准顺序。如果先校准频段n最低频率,那么图6方法的内核可以设计成和现在图5方法的内核一样,反之亦然。本实施例不再赘述,此种情况也属于本实施例保护的范围。

[0133]

本专利提出的一种解决多段式vco在特殊情况下频率无法校准的方法,出发点是为了解决图4中极端应用场景的多段式vco频率校准,但不仅限于此,在优选的实施例中,本实施例还可适用于以下两种情况。

[0134]

情况一:。如果不知道某一款vco的某一频段标称最低频率f

min_n

和标称最高频率f

max_n

,使用本技术提出的方法,可以完成多段式vco频率校准,只需要在多段式vco全频段标称最低频率f

min_n

和全频段标称最高频率f

max_n

之间任选两个初值作为某一频段标称最低频率f

min_n

和标称最高频率f

max_n

,即可使用本技术提出的方法完成多段式vco该频段的频率校准。

[0135]

情况二:甚至如果不知道某一款vco的全频段标称最低频率f

min_n

和全频段标称最高频率f

max_n

,根据目前的器件水平的常识判断,目前射频vco的频率不会低于0hz,不会超过40ghz,鉴相器可以正常工作的频率不超过30ghz,(仅作举例说明,随着器件水平的发展可能会变,但不影响本实施例核心思想的阐述),因此可以将全频段标称最低频率f

min_n

的初值设置为0hz,将全频段标称最高频率f

max_n

设置为30ghz,即可使用本技术提出的方法完成多段式vco该频段的频率校准。

[0136]

为了更清楚的解释本技术,提出一种多段式vco在不同频率误差场景下的校准方法的具体实例。

[0137]

按照本技术提出的一种解决多段式vco在特殊情况下频率无法校准的方法,针对以下场景进行频率校准实施实例说明,验证选取某一多段式vco其中一段,即可以说明本技术的核心思想。实施实例中分别使用现有方法和本技术提出的方法进行多段式vco频率校准,比较二者的不同。

[0138]

某一多段式vco的频段3的情况符合图4对应的场景b,其频率分布情况见图7所示,具体参数如下:频段3的实际最低频率12890mhz,实际最高频率12950mhz,标称最低频率为f

min_3

=13200mhz,标称最高频率f

max_3

=15200mhz,该多段式vco全频段标称最低频率f

min

=

10000mhz,多段式vco全频段标称最高频率f

max

=16000mhz。

[0139]

方法1:

[0140]

针对该场景使用现有方法进行校准,选取校准比例因子a=b=0.4。

[0141]

程序1开始:

[0142]

步骤s11:k=0,k=1,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_31

=15200-(15200-13200)

×

0.4

×

1=15120mhz,15120mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。赋值k=k 1=2,程序继续执行。

[0143]

步骤s12:k=2,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_32

=15200-(15200-13200)

×

0.4

×

2=15040mhz,15040mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。赋值k=k 1=3,程序继续执行。

[0144]

步骤s13:

……

,重复上述步骤s12。

[0145]

步骤s14:k=28,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_313

=15200-(15200-13200)

×

0.4

×

28=12960mhz,12960mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。赋值k=k 1=14,程序继续执行。

[0146]

步骤s15:k=29,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_314

=15200-(15200-13200)

×

0.4

×

29=12880mhz,12880mhz低于多段式vco频段3的实际最低频率12890mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。赋值k=k 1=30,程序继续执行。

[0147]

步骤s16:

……

,重复上述步骤s15,f

max_

3k会越来越小,锁相环永远无法锁定,程序将一致执行,直到运算资源耗尽前程序都不会结束。

[0148]

方法2:

[0149]

针对该场景使用本专利提出的方法进行校准,同样选取校准比例因子a=b=0.4。

[0150]

程序2开始:

[0151]

步骤s201:k=0,k=1,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_31

=15200-(15200-13200)

×

0.4

×

1=15120mhz,15120mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

max_31

>f

min

,赋值k=k 1=2,程序继续执行。

[0152]

步骤s202:k=2,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_32

=15200-(15200-13200)

×

0.4

×

2=15040mhz,15040mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

max_32

>f

min

,赋值k=k 1=3,程序继续执行。

[0153]

步骤s203:

……

,重复上述步骤步骤s202。

[0154]

步骤s204:k=65,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_365

=15200-(15200-13200)

×

0.4

×

65=10000mhz,10000mhz低于多段式vco频段3的实际最低频率12890mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

max_

365<f

min

,赋值k=-1,k=k 1=0,程序继续执行。

[0155]

步骤s205:k=0,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为fmin_

30

=15200-(15200-13200)

×

0.4

×

0=15200mhz,15200mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

mi

n_

30

<f

max

,赋值k=k 1=1,程序继续执行。

[0156]

步骤s206:

……

,重复上述步骤步骤s205。

[0157]

步骤s207:k=10,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

mi

n_

310

=15200-(15200-13200)

×

0.4

×

10=16000mhz,16000mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

mi

n_

310

>f

max

,赋值a=a/10=0.04,程序继续执行。

[0158]

步骤s208:k=0,k=1,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_31

=15200-(15200-13200)

×

0.04

×

1=15192mhz,15192mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

max_31

>f

min

,赋值k=k 1=2,程序继续执行。

[0159]

步骤s209:

……

,重复上述步骤步骤s208。

[0160]

步骤s210:k=282,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

max_3281

=15200-(15200-13200)

×

0.04

×

282=12944mhz,12944mhz在多段式vco频段3的实际最低频率12890mhz与实际最高频率12950mhz之间,因此锁相环锁定,鉴相器向控制单元上报锁定。判断k>1,将已锁定的频率值记录在控制单元的存储器中,该频率值为校准后的频段n的最高频率f

max_n

=12944mhz。程序继续执行。

[0161]

步骤s211:m=0,m=1,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_31

=13200 (15200-13200)

×

0.4

×

1=13280mhz,13280mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

min_31

<f

max

,赋值m=m 1=2,程序继续执行。

[0162]

步骤s212:

……

,重复上述步骤步骤s211。

[0163]

步骤s213:m=35,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_335

=13200 (15200-13200)

×

0.4

×

35=16000mhz,16000mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

min_335

>f

max

,赋值m=-1,m=m 1=0,程序继续执行。

[0164]

步骤s214:m=0,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_30

=13200-(15200-13200)

×

0.4

×

0=13200mhz,13200mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

min_30

>f

min

,赋值m=m 1=1,程序继续执行。

[0165]

步骤s215:

……

,重复上述步骤步骤s214。

[0166]

步骤s216:m=3,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_33

=13200-(15200-13200)

×

0.4

×

3=12960mhz,12960mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

min_33

>f

min

,赋值m=m 1=4,程序继续执行。

[0167]

步骤s217:m=4,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_34

=13200-(15200-13200)

×

0.4

×

4=12880mhz,12880mhz低于多段式vco频段3的实际

最低频率12890mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

min_34

>f

min

,赋值m=m 1=5,程序继续执行。

[0168]

步骤s218:

……

,重复上述步骤步骤s217。

[0169]

步骤s219:m=40,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_340

=13200-(15200-13200)

×

0.4

×

40=10000mhz,10000mhz低于多段式vco频段3的实际最低频率12890mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

min_340

<f

min

,赋值b=b/10=0.04,程序继续执行。

[0170]

步骤s220:m=0,m=1,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_31

=13200 (15200-13200)

×

0.04

×

1=13192mhz,13192mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

min_31

<f

max

,赋值m=m 1=2,程序继续执行。

[0171]

步骤s221:

……

,重复上述步骤步骤s220。

[0172]

步骤s222:m=350,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_350

=13200 (15200-13200)

×

0.04

×

350=16000mhz,16000mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

min_31

>f

max

,赋值m=-1,m=m 1=0,程序继续执行。

[0173]

步骤s223:m=0,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_30

=13200-(15200-13200)

×

0.04

×

0=13200mhz,13200mhz超出多段式vco频段3的实际最高频率12950mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。判断f

min_30

>f

min

,赋值m=m 1=1,程序继续执行。

[0174]

步骤s224:

……

,重复上述步骤步骤s223。

[0175]

步骤s225:m=32,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_332

=13200-(15200-13200)

×

0.04

×

32=12944mhz,12944mhz在多段式vco频段3的实际最低频率12890mhz与实际最高频率12950mhz之间,因此锁相环锁定,鉴相器向控制单元上报锁定。赋值m=m 1=33,程序继续执行。

[0176]

步骤s226:

……

,重复上述步骤步骤s225。

[0177]

步骤s227:m=38,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_338

=13200-(15200-13200)

×

0.04

×

38=12896mhz,12896mhz在多段式vco频段3的实际最低频率12890mhz与实际最高频率12950mhz之间,因此锁相环锁定,鉴相器向控制单元上报锁定。赋值m=m 1=39,程序继续执行。

[0178]

步骤s228:m=39,控制单元的控制器向鉴相器发送指令,控制鉴相器输出频率为f

min_339

=13200-(15200-13200)

×

0.04

×

39=12888mhz,低于多段式vco频段3的实际最低频率12890mhz,因此锁相环无法锁定,鉴相器向控制单元上报没有锁定。将距离未锁定最近的一次(m=m-1=38)的已锁定频率值记录在控制单元的存储器中,该频率值为校准后的频段3的最低频率f

min_n

=f

min_338

=12896mhz。

[0179]

至此,多段式vco频段3的频率已校准完成,校准后的最低频率为12896mhz,校准后的最高频率为12944mhz,图7中阴影区域为校准后的最低频率和最高频率区间。

[0180]

通过上述实例验证表明:与现有方法对比,本专利提出的方法可以完成某些极端情况的多段式vco的频率校准。

[0181]

以上仅为发明的优选实施例,并非因此限制发明的专利范围,凡是利用发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在发明的专利保护范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。