1.本发明涉及计算机技术领域,尤其涉及一种基于对称电路的信号线缆延时检测系统。

背景技术:

2.在大规模硬件仿真器或原型验证平台中,会使用大量信号线缆来连接多个硬件主板,大规模硬件仿真器或原型验证平台可以基于fpga(field-programmable gate array)架构或soc(system on chip)架构来构建。根据硬件主板以及主板上连接器位置的不同,连接的信号线缆会有各种不同的长度,不同长度的信号线缆会有不同的延时。在编译过程中,编译器会利用延时等参数。为了检测大规模硬件仿真器或原型验证平台中已连接的信号线缆的延时,往往需要设计复杂的检测方法,例如设置专用的信号线缆延时检测电路,或者基于不同的平台建立不同的检测模型。但是,大规模硬件仿真器或原型验证平台中,信号线缆的连接可以有不同的拓扑结构,系统信号线缆连接的拓扑结构也可能随着dut(design under test)或其他因素做改动而变化,当连接方式改变后或更换不同平台后,需要重新设置检测电路或重新训练检测模型,检测效率低,可靠性差。

技术实现要素:

3.本发明目的在于,提供一种基于对称电路的信号线缆延时检测系统,支持系统任意连接信号线缆延时的检测,而不用修改延时检测电路,提高了信号线缆延时检测效率和可靠性。

4.本发明提供了一种基于对称电路的信号线缆延时检测系统,包括m个连接器{c1,c2,

…

,cm,

…

,cm},m个延时检测电路{d1,d2,

…

,dm,

…dm

}, cm为第m个连接器,dm为cm对应的延时检测电路, dm设置在cm中,m的取值范围为1到m,m为大于等于2的正整数;dm包括两个对称设置的延时检测单元d

m1

和d

m2

,d

m1

和cm对应的第一管脚p

m1

连接,d

m2

和cm对应的第二管脚p

m2

连接,d

m1

和d

m2

相连接;ci和cj之间通过信号线缆l

ij

相连接,di、d

j 对称设置,i和j的取值范围均为1到m,且i≠j, p

i1

和p

j1

之间通过l

ij

中的第一信号线s

ij1

相连, p

i2

和p

j2

之间通过l

ij

中的第二信号线s

ij2

相连,di、dj、s

ij1

、s

ij2

构成环形振荡回路;检测l

ij

延时过程中,延时检测单元d

i1

接收延时检测单元d

j1

通过s

ij1

传输的输入信号,且将输入信号反相后输出给延时检测单元d

i2

,d

i2

用于将反相后的输入信号通过s

ij2

传输给延时检测单元d

j2

,d

j2

将反相后的输入信号传输给d

j1

,d

j1

将反相后的输入信号作为新的输入信号通过s

ij1

传输给d

i1

,循环执行,基于环形振荡回路的环形振荡周期确定l

ij

的线缆延时t

ij

。

5.本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明提供的一种基于对称电路的信号线缆延时检测系统可达到相当的技术进步性及实用性,并具有产业上的广泛利用价值,其至少具有下列优点:

本发明的延时检测电路设计结构对称,支持系统任意连接线缆延时的检测,而不用修改延时检测电路,简单易行,提高了信号线缆延时检测效率和可靠性。

6.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

附图说明

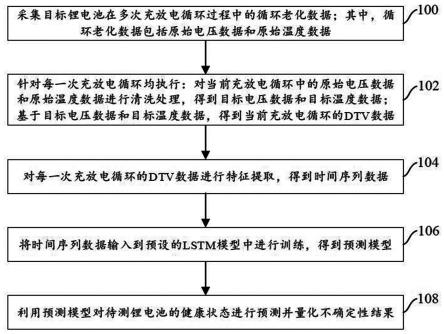

7.图1为本发明实施例中ci和cj之间建立的信号线缆延时检测电路示意图。

具体实施方式

8.为更进一步阐述本发明为达成预定发明目的所采取的技术手段及功效,以下结合附图及较佳实施例,对依据本发明提出的一种基于对称电路的信号线缆延时检测系统的具体实施方式及其功效,详细说明如后。

9.本发明实施例提供了一种基于对称电路的信号线缆延时检测系统,包括m个连接器{c1,c2,

…

,cm,

…

,cm},m个延时检测电路{d1,d2,

…

,dm,

…dm

},cm为第m个连接器,dm为cm对应的延时检测电路,dm设置在cm中,m的取值范围为1到m,m为大于等于2的正整数。

10.本发明实施例所述系统能够适用于大规模硬件仿真器或原型验证平台中,大规模硬件仿真器或原型验证平台中,大规模硬件仿真器或原型验证平台可以基于fpga(field-programmable gate array)架构或soc(system on chip)架构来构建。{c1,c2,

…

,cm,

…

,cm}分布在大规模硬件仿真器或原型验证平台一个或多个组成模块上,所述组成模块为fpga或soc。

11.dm包括两个对称设置的延时检测单元d

m1

和d

m2

,d

m1

和cm对应的第一管脚p

m1

连接,d

m2

和cm对应的第二管脚p

m2

连接,d

m1

和d

m2

相连接。可以理解的是,连接器用于连接信号线缆,信号线缆中包括多条信号线,对应多个管脚,每一管脚对应信号线缆中的一个信号线。第一管脚和第二管脚可以是信号线缆对应的任意两个管脚,所述系统中,连接器信号相同,信号线缆型号相同,所选择的第一管脚和第二管脚也相同,dm具体可以采用verilog等硬件描述语言设计实现。以组成模块为fpga为例,基于fpga中的开发工具可以将dm对应的硬件设计转换为比特流,下载到fgpa中。

12.任意两个连接器通过信号线缆连接后,均可建立起信号线缆延时检测电路。作为一种实施例,如图1所示,ci(对应图1中的100)和cj(对应图1中的200)之间通过信号线缆l

ij

相连接,di、d

j 对称设置,可以理解的是,ci为第i个连接器,cj为第j个连接器,di为ci对应的延时检测单元,dj为cj对应的延时检测单元,i和j的取值范围均为1到m,且i≠j。p

i1

(对应图1中的5)和p

j1

(对应图1中的7)之间通过l

ij

中的第一信号线s

ij1

相连, p

i2

(对应图1中的6)和p

j2

(对应图1中的8)之间通过l

ij

中的第二信号线s

ij2

相连,di、dj、s

ij1

、s

ij2

构成环形振荡回路。p

i1 、p

i2

分别为ci对应的第一管脚、第二管脚。p

j1 、p

j2

分别为cj对应的第一管脚、第二管脚。作为一种实施例,检测l

ij

延时过程中,d

i1

接收d

j1

通过s

ij1

传输的输入信号,且将输入信号反相后输出给d

i2

,d

i2

用于将反相后的输入信号通过s

ij2

传输给d

j2

,d

j2

将反相后的输入信号传输给d

j1

,d

j1

将反相后的输入信号作为新的输入信号通过s

ij1

传输给d

i1

,循环执行,基于环形振荡回路的环形振荡周期确定l

ij

的线缆延时t

ij

。其中,d

i1

和d

i2

为ci的延时检测单元,dj1

和d

j2

为cj的延时检测单元。

13.作为一种实施例,所述基于环形振荡回路的环形振荡周期确定l

ij

的线缆延时t

ij

,包括:获取环形振荡回路的环形振荡周期t0、以及执行一次环形振荡回路ci内部的延时ti和cj内部的延时tj。 需要说明的是,一个环形振荡周期中,环形振荡回路需要执行两圈,因此,环形振荡周期的时间t0=2*ti 2*tj 4*t

ij

,基于t0、ti、tj确定l

ij

的线缆延时t

ij

:t

ij

=[t

0-2(ti tj)]/4。

[0014]

其中,所述系统基于生成的内部时序分析报告,读取执行一次环形振荡回路ci内部的延时ti和cj内部的延时tj。需要说明的是,内部时序分析报告是基于现有技术直接生成的,可以读取出内部延时。以基于fpga架构为例,fpga的编译工具是可以生成时序分析报告,从fpga编译工具时序分析报告中可以读取出对应的内部延时,内部时序分析报告的生成过程在此不再赘述。

[0015]

作为一种实施例,所述系统还包括dm对应的振荡周期延时检测电路hm,与dm连接,用于检测dm对应的t0。可以理解的是,当环形振荡回路中的di、dj均存在对应的振荡周期延时检测电路,任意选择一个获取t0即可。具体的,hm用于记录dm在一个hm的时钟周期t

hm

内的时钟个数clk_num,基于t

hm

和clk_num确定dm的时钟周期t0:t0=t

hm

/clk_num,其中,t

hm

为外部输入的已知的hm的时钟周期。

[0016]

作为一种实施例,d

m1

包括io缓冲器e

m1

、反相器f

m1

、选择器g m1

,e

m1

包括第一通路ex

m11

和第二通路ex

m12

;d

m2

包括io缓冲器e

m2

、反相器f

m2

、选择器g

m2

、e

m2

包括第一通路ex

m21

和第二通路ex

m22

。 其中,ex

m11

的输出端与p

m1

连接,ex

m11

的输入端与g

m2

的输出端连接,ex

m12

的输入端与p

m1

连接,输出端分别与f

m1

的输入端以及g

m1

的输入端连接,g

m1

的输出端与ex

m21

的输入端连接,ex

m21

的输出端与p

m2

连接,ex

m22

的输入端与p

m2

连接,ex

m22

的输出端与f

m2

的输入端以及g

m2

的输入端相连。

[0017]em1

、e

m2

能够在两种通路之间切换,具体地,通过接收到的使能信号(en),选择通路,当e

m1

的使能信号配置为1时,接通ex

m11

,配置为0时,接通ex

m12

。当e

m2

的使能信号配置为1时,接通ex

m21

,配置为0时,接通ex

m22

。

[0018]

g m1

、g

m2

基于接收到的选择信号(sel)来确定选择对应的输入,具体地,当g

m1

的选择信号配置为0时,g

m1

选择输入f

m1

输出的信号,配置为1时,g m1

选择输入ex

m12

输出的信号。当g

m2

的选择信号配置为0时,g m2

选择输入f

m2

输出的信号,配置为1时,g

m2

选择输入ex

m22

输出的信号。

[0019]

作为一种实施例,在di、dj、s

ij1

、s

ij2

构成的环形振荡回路中,di中的io缓冲器e

i1

(对应图1中的11)与dj中的io缓冲器e

j1

(对应图1中的31)对称设置;di中的选择器g

i1

(对应图1中的13)与dj中的选择器g

j2

(对应图1中的33)对称设置;其中,其中,e

i1

与e

i2

(对应图1中的21)的使能信号相反,e

i1

与e

j1

的使能信号相反,e

i1

与e

j2

(对应图1中的41)的使能信号相同;g

i1

、g

i2

(对应图1中的23)、g

j1

、g

j2

(对应图1中的43)的选择信号仅有一个配置为0,其余全部配置为1。例如,e

i1

、e

i2

、e

j1

、e

j2

的使能信号en1、en2、en3、en4分别设置为0、1、1、0,g

i1

、g

i2

、g

j1

、g

j2

的选择信号sel1、sel2、sel3、sel4分别设置为0、1、1、1。再如,e

i1

、e

i2

、e

j1

、e

j2

的使能信号en1、en2、en3、en4分别设置为1、0、0、1,g

i1

、g

i2

、g

j1

、g

j2

的选择信号sel1、sel2、sel3、sel4分别设置为1、1、0、1。可以理解的是,以上仅是两种示例,其他设置,可以满足di、dj、s

ij1

、s

ij2

构成的环形振荡回路的设置均在本技术保护范围之内。图1中,12表示与e

i1

相连的

反相器,22表示与e

i2

相连的反相器,32表示与e

j1

相连的反相器,42表示与e

j2

相连的反相器。10表示di对应的振荡周期延时检测电路,20表示dj对应的振荡周期延时检测电路,14表示11的第一通路,15表示11的第二通路,24表示21的第一通路,25表示21的第二通路,34表示31的第一通路,35表示31的第二通路,44表示41的第一通路,45表示41的第二通路。

[0020]

作为一种实施例,当dm接收到复位信号(sys_rst)时,对应的使能信号、选择信号全部设置为0,然后再根据具体需求配置对应的使能信号和选择信号。

[0021]

作为一种实施例,确定l

ij

的线缆延时t

ij

之后,所述系统还用于基于t

ij

以及延时与线缆长度的关联系数,确定l

ij

的线缆长度。需要说明的是,每一线缆的延时与线缆长度的关联系数是已知的,或可直接基于现有技术测算出来的,因此,确定线缆延时后即可算出信号线缆的长度。

[0022]

本发明实施例所述系统的延时检测电路设计结构对称,支持系统任意连接线缆延时的检测,而不用修改延时检测电路,简单易行,提高了信号线缆延时检测效率和可靠性。基于线缆延时进一步确定线缆长度,进而提高了信号线缆长度的检测效率和可靠性。

[0023]

以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。