1.本发明涉及一种应用于空间光通信的高速基带信号产生与同步实现系统,属于高速数据传输范畴,广泛应用于空间光通信等领域,用于高速调制基带信号的产生及同步实现。

背景技术:

2.在空间光通信中,高速基带信号产生及相位同步是调制基带发射的关键技术之一。空间光通信系统中要求高速调制基带号i、q两路信号相位同步,光通信测距一体化系统还要求调制发射基带信号与外部参考时钟保持确定性相位。传统的高速基带信号产生采用fpga和高速dac来实现,由于现有dac的转换速率受限,对于高速i、q基带信号,单个高速dac转换速率难以满足要求,需要采用两片高速dac来实现,并且两片高速dac的同步实现较复杂。对于要求测距的高速基带信号不仅要求高速i、q基带信号同步,还要求高速i、q基带信号与参考时钟有确定性相位,硬件实现同步更加复杂,而且相位一致性精度难以满足要求。

技术实现要素:

3.本发明解决的技术问题是:克服现有技术的不足,提出了一种高速基带信号产生及同步实现的系统。该发明采用一种闭环动态控制的算法,实时动态控制fpga片内gth(gigabyte transceiver h)ip(intellectual property)核的相位插值模块实时调节高速基带发射时钟和外部参考时钟相位关系,保证发射基带信号与外部参考时钟的相位一致性及i、q信号同步性。

4.本发明的技术解决方案是:

5.一种应用于空间光通信的高速基带信号产生与同步系统,包括:数据源模块、编码模块、组帧模块、高速基带信号产生及同步控制模块、激光调制器;

6.数据源模块:产生并行时钟clk和并行数据data输出给编码模块;

7.编码模块:完成编码后产生编码后的并行数据cdata和同步时钟tx_clk;

8.组帧模块:利用同步时钟tx_clk完成编码后的并行数据cdata重新组帧和插空帧,并且将数据分为并行两路数据i_pdata、q_pdata,输出给高速基带信号产生及同步控制模块;

9.高速基带信号产生及同步控制模块:该模块包括相位控制单元和gth ip核;其中,相位控制单元完成高速发射基带信号与参考时钟ref_clk相位调节控制;gth ip核包括两个ip核gth core0和gth core1,两个ip核分别将并行两路数据i_pdata、q_pdata转换为高速串行信号i_sdata、q_sdata,输出给激光调制器;

10.激光调制器:完成高速串行信号i_sdata、q_sdata与激光载波信号的调制,输出高速光调制信号。

11.进一步的,所述高速基带信号产生及同步控制模块包括:存储单元fifo模块、相位插值模块、锁相环模块、分频器模块、并串转换模块;

12.其中,存储单元fifo模块、相位插值模块、锁相环模块、分频器模块、并串转换模块共同构成gth ip核;极性判断模块、相位积分模块、状态控制模块共同构成相位控制单元;

13.存储单元fifo模块:接收外部输入的基带数据和时钟,利用外部参考时钟ref_clk作为写时钟wr_clk进行数据缓存;读时钟rd_clk由相位调整后的高速位时钟bit_clk分频产生;

14.锁相环模块:接收外部输入参考时钟信号ref_clk,经倍频锁相后输出与基带发射同速率的高速时钟;

15.相位插值模块:接收锁相环模块输出的高速时钟信号,通过相位插值控制信号tx_pi_ctr来调节输出高速时钟信号bit_clk的相位;

16.分频器模块:接收相位调整后的高速时钟,完成整数倍分频后,作为fifo的读时钟rd_clk和并串转换的低速时钟ps_clk;

17.并串转换模块:接收相位调整后的高速时钟bit_clk、分频后的低速时钟ps_clk、fifo读出的并行数据rd_data,将并行数据转换为高速串行数据s_data。

18.进一步的,分频器模块将相位插值后的时钟进行分频后作为发射并行数据时钟,分频数div_n为:

[0019][0020]

其中,f

linerate

为发射高速基带信号速率,n

data

为并行数据位宽。

[0021]

进一步的,所述相位控制单元包括极性判断模块、相位积分模块、状态控制模块;

[0022]

极性判断模块接收gth ip核产生的发射存储器fifo内部存储状态的标志信号txbuf_status,然后将txbuf_status输出的值进行极性判断,是否调整相位插值,输出相位插值控制信号tx_pi_ctr;

[0023]

相位积分模块:将极性判断模块的txbuf_status输出值进行acc_n个周期的累加运算,将累加结果acc_dat的输出给状态控制模块;

[0024]

状态控制模块:根据相位积分模块输出的结果产生复位信号、相位增加信号或相位减少信号。

[0025]

进一步的,存储单元fifo模块根据缓存数据的状态,通过标志信号txbuf_status输出不同的状态值,其中txbuf_status为两位二进制数,其状态如下:

[0026]

(1)若txbuf_status大于“01”,则fifo溢出或全空;

[0027]

(2)若txbuf_status等于“01”,则fifo半满状态;

[0028]

(3)若txbuf_status小于“01”,则fifo少于半满状态。

[0029]

进一步的,若txbuf_status小于“01”,表示fifo状态处于少于半满状态,需要调节相位插值控制器,增加相位插值,产生负的相位信号即输出

“‑

1”,经积分模块后输出acc_dat小于0,状态控制模块输出相位增加信号,增加相位插值,使fifo达到接近半满状态;

[0030]

若txbuf_status等于“01”,表示fifo状态处于半满状态,需要调节相位插值控制器,使fifo达到接近半满状态。需要调节相位插值控制器,减少相位插值,产生正的相位信号即输出“1”,经积分模块后输出acc_dat大于0,状态控制模块输出相位减少信号,减少相位插值,使fifo达到接近半满状态;

[0031]

若txbuf_status大于“01”,表示fifo状态处于溢出或全空状态,需要调节相位插

值控制器,减少相位插值,产生正的相位信号即输出“1”,经积分模块后输出acc_dat大于0,状态控制模块输出相位减少信号,减少相位插值,使fifo达到接近半满状态。

[0032]

进一步的,累加结果acc_dat计算公式如下:

[0033][0034]

其中acc_n为整数,且acc_n大于512。

[0035]

进一步的,状态控制模块的状态控制结果如下:

[0036]

(1)若acc_dat》2,则产生复位信号,使fifo复位;

[0037]

(2)若acc_dat》0,则产生相位减少信号;

[0038]

(3)若acc_dat《0,则产生相位增加信号。

[0039]

进一步的,状态控制模块实现相位同步控制,按照如下步骤实现:

[0040]

第一步:开始st0状态,直接进入下一状态st1状态;

[0041]

第二步:状态判断st1状态,判断acc_dat值是否大于“2”,若小于“2”则进入st2状态,否则进入st4状态;

[0042]

第三步:状态判断st2状态,判断acc_dat值是否大于“0”,若大于“0”则进入st3状态,否则进入st5状态;

[0043]

第四步:相位控制st3状态,输出相位插值控制器减“1”信号后,进入st2状态,执行第三步;

[0044]

第五步:复位st4状态,复位后,进入st0状态;

[0045]

第六步:相位控制st5状态,输出相位插值控制器加“1”信号后,进入st6状态;

[0046]

第七步:状态判断st6状态,判断acc_dat值是否等大于“0”,若大于“0”,则进入st1状态,否则进入st5状态,执行第六步。

[0047]

本发明与现有技术相比的优点在于:

[0048]

(1)提出了一种空间光通信的高速基带信号产生及相位同步实现方法,解决了高速基带信号与参考时钟相位不确定性及i、q信号同步性问题。经硬件验证分析,采用该方法产生的高速基带信号相位一致性和同步性能优于2ps,满足空间光通信系统要求。

[0049]

(2)该方法简化了传统高速基带信号实现相位同步的方法,提出了一种相位同步闭环控制算法,将gth ip核内发送端fifo存储状态作为误差信号,设计了一种时钟相位状态控制的闭环控制环路,采用闭环控制的方式动态调整高速发送时钟相位,使发送的i、q高速基带信号相位与外部参考时钟相位保持确定性相位关系。

[0050]

(3)该发明硬件实现简单,相位同步控制算法复杂度低,软件实现占用资源少,易于工程化实现。

附图说明

[0051]

图1是高速基带信号产生及同步实现系统框图;

[0052]

图2是高速基带信号产生及同步控制模块框图;

[0053]

图3是相位同步控制算法实现框图;

[0054]

图4是硬件验证实现框图;

[0055]

图5是高速基带信号输出波形图;

[0056]

图6是高速基带信号输出眼图;

[0057]

图7是txbuf_status状态输出波形;

[0058]

图8相位同步控制算法软件实现框图。

具体实施方式

[0059]

空间光通信系统中要求i、q两路高速调制基带信号相位同步,光通信测距一体化系统还要求调制发射基带信号与外部参考时钟保持确定性相位。传统的高速基带信号产生采用fpga和高速dac来实现,由于现有dac的转换速率受限,对于高速i、q基带信号,单个高速dac转换速率难以满足要求,需要采用两片高速dac来实现,并且两片高速dac的同步实现较复杂。对于要求测距的高速基带信号不仅要求高速i、q基带信号同步,还要求高速i、q基带信号与参考时钟有确定性相位,硬件实现同步更加复杂,而且相位一致性精度难以满足要求。

[0060]

本发明提出了一种高速基带信号产生及同步实现的方法。该发明采用一种闭环动态控制的算法,实时动态控制fpga片内gth(gigabyte transceiver h)ip(intellectual property)核的相位插值模块实时调节高速基带发射时钟和外部参考时钟相位关系,保证发射基带信号与外部参考时钟的相位一致性及i、q信号同步性。

[0061]

硬件实现结果表明,该方法产生高速基带信号具有较好的一致性和同步性能,相位一致性及i、q同步精度小于2ps,满足空间光通信系统要求。此外,该方法硬件实现简单,相位同步控制算法复杂度低,软件实现占用资源少,易于工程化实现。

[0062]

以下结合说明书附图对本技术实施例所提供的一种应用于空间光通信的高速基带信号产生与同步实现方法做进一步详细的说明,具体实现方式可以包括:

[0063]

一、高速基带信号产生及同步实现

[0064]

图1是高速基带信号产生及同步实现系统框图。该图中示意了高速基带信号产生的整个信号处理流程。该系统一共包含五个模块,其中各个模块功能如下:

[0065]

数据源模块:产生并行时钟clk和并行数据data输出给编码模块。

[0066]

编码模块:完成编码后产生编码后的并行数据cdata和同步时钟tx_clk。

[0067]

组帧模块:利用同步控制产生的时钟tx_clk完成编码后的数据重新组帧和插空帧,并且将数据分为并行两路数据i_pdata、q_pdata输出给高速基带产生及同步控制模块。

[0068]

高速基带信号产生及同步控制模块:该模块包括相位控制单元和gth(gigabyte transceiver h)ip(intellectual property)核。其中,相位控制单元完成高速发射基带信号与参考时钟ref_clk相位调节控制。gth ip核包括两个ip核gth core0和gth core1,两个ip核分别将并行两路数据i_pdata、q_pdata转换为高速串行信号i_sdata、q_sdata输出给激光调制器。

[0069]

激光调制器:完成高速串行信号i_sdata、q_sdata与激光载波信号的调制,输出高速光调制信号。

[0070]

二、高速基带信号产生

[0071]

高速基带产生由相位插值控制(phase interplator ctr)和gth ip核(gth core)组成,通过phase interplator ctr单元动态调节高速发射时钟的相位实现高速基带发射位时钟(bit_clk)与外部参考时钟ref_clk相位保持一致。高速基带产生及同步控制模块框

图如下图2所示。

[0072]

该模块与外部接口有发射基带并行数据tx_data,并行数据时钟tx_clk,外部参考时钟ref_clk。

[0073]

相位插值控制(phase interplator ctr)接收gth core产生的发射存储器fifo内部存储状态的标志信号txbuf_status,然后进行判断是否调整相位插值,输出相位插值控制信号tx_pi_ctr。

[0074]

gth core主要由存储单元fifo(first in first out),锁相环pll(phase locked loop),发射相位插值tx-pi(transmitter phase interplator),分频模块div_n(division),并串转换piso(parallel in serial out)组成。各个单元的功能如下:

[0075]

存储单元fifo(first in first out):接收外部输入的基带数据和时钟,利用外部参考时钟ref_clk作为写时钟wr_clk进行数据缓存。读时钟rd_clk由相位调整后的高速位时钟bit_clk分频产生。

[0076]

锁相环pll(phase locked loop):接收外部输入参考时钟信号ref_clk,经倍频锁相后输出与基带发射同速率的高速时钟。

[0077]

发射相位插值tx-pi(transmitter phase interplator):接收pll输出的高速时钟信号,通过相位插值控制信号tx_pi_ctr调节输出高速时钟信号bit_clk的相位。

[0078]

分频模块div_n(division):接收相位调整后的高速时钟,完成整数倍分频后,作为fifo的读时钟rd_clk和并串转换的低速时钟ps_clk。

[0079]

并串转换piso(parallel in serial out):接收相位调整后的高速时钟bit_clk,分频后的低速时钟ps_clk,fifo读出的并行数据rd_data,将并行数据转换为高速串行数据s_data。

[0080]

三、相位同步控制

[0081]

相位同步控制,根据fifo(first in first out)存储状态,采用闭环控制的方式动态调整锁相环产生的高速发射时钟的相位,使得其分频后的时钟相位与外部参考时钟的相位保持确定性的相位关系。相位同步控制算法实现框图如图3所示,gth core主要包括存储单元fifo(first in first out),相位插值,锁相环和分频器,各个模块功能如下:

[0082]

存储单元fifo(first in first out):根据缓存数据的状态输出通过txbuf_status输出不同的状态值。其中txbuf_status为两位二进制数,其状态如下:

[0083]

(1)若txbuf_status大于“01”,则fifo溢出或全空;

[0084]

(2)若txbuf_status等于“01”,则fifo半满状态;

[0085]

(3)若txbuf_status小于“01”,则fifo少于半满状态。

[0086]

相位插值:根据状态控制器输出的增加或减少信号调节高速时钟相位。

[0087]

锁相环:将外部参考时钟进行倍频锁相后输出高速的发射时钟。

[0088]

分频器:将相位插值后的时钟进行分频后作为发射的并行时钟,分频数div_n为

[0089][0090]

其中,f

linerate

为发射高速基带信号速率,n

data

为并行数据位宽。

[0091]

相位同步控制器包括极性判断、相位积分和状态控制三个模块,各个模块的功能如下:

[0092]

极性判断:将txbuf_status输出的值进行极性判断,若txbuf_status小于“01”,输出

“‑

1”,否则,输出“1”。

[0093]

相位积分:将极性判断输出值进行acc_n(acc_n为整数,acc_n大于512)个周期的累加运算,将累加结果acc_dat的输出给状态控制模块。

[0094]

状态控制:根据相位积分输出的结果产生复位信号和相位增加或减少信号。状态控制结果如下:

[0095]

(1)若acc_dat》2,则产生复位信号,使fifo复位;

[0096]

(2)若acc_dat》0,则产生相位减少信号;

[0097]

(3)若acc_dat《0,则产生相位增加信号。

[0098]

相位同步控制算法实现步骤如下:

[0099]

第一步:开始st0状态,直接进入下一状态st1状态;

[0100]

第二步:状态判断st1状态,判断acc_dat值是否大于“2”,若小于“2”则进入st2状态,否则进入st4状态;

[0101]

第三步:状态判断st2状态,判断acc_dat值是否大于“0”,若大于“0”则进入st3状态,否则进入st5状态;

[0102]

第四步:相位控制st3状态,输出相位插值控制器减“1”信号后,进入st2状态,执行第三步;

[0103]

第五步:复位st4状态,复位后,进入st0状态;

[0104]

第六步:相位控制st5状态,输出相位插值控制器加“1”信号后,进入st6状态;

[0105]

第七步:状态判断st6状态,判断acc_dat值是否等大于“0”,若大于“0”,则进入st1状态,否则进入st5状态,执行第六步。

[0106]

实施例1:

[0107]

采用xilinx virtex7系列xc7vx690t fpga试验板的硬件平台,实现码速率为10gbps qpsk基带信号。采用两个gth ip核分别实现两路线速率为5gbps的i、q基带信号,即f

linerate

为5gbps,并行数据位宽n

data

选择32路,pll时钟速率f

pllclk

为5ghz,外部参考时钟ref_clk频率为156.25mhz。相位插值控制积分器的累加点数acc_n选择1024点,硬件验证实现框图如图4所示。由信号源产生156.25mhz外部参考时钟分为两路,一路输出给fpga试验板作为基带发射参考时钟,另一路给示波器作为相位测试参考信号。fpga试验板经gth接口输出两路5gbps高速基带数据i_data,q_data输出给示波器,高速基带信号输出波形图如图5所示,高速基带信号输出眼图如图6所示。两路信号相位同步后的txbuf_status状态输出波形如图7所示。

[0108]

由图5可以看出,c2为参考时钟信号,c1,c3通道为输出的i、q高速基带信号。经多次反复开关机测试,i、q高速基带信号与参考时钟信号相位固定,且i、q高速基带信号同步性能小于2ps。

[0109]

由图7可以看出,相位同步后txbuf_status状态输出为“0”与“1”交替跳变状态,即相位同步后fifo存储状态处于半满与少于半满的动态平衡状态。

[0110]

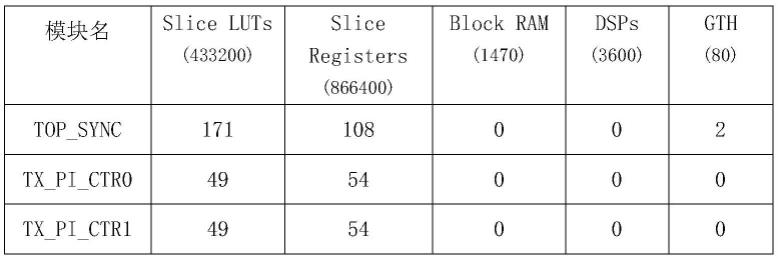

相位同步控制算法在xilinx xc7vx690t-ffg1927 fpga硬件平台上通过vhdl代码实现。该算法软件模块主要包括两个gth ip核和两个相位控制器模块。两个相位同步控制器模块分别接收两个gth ip核的tx_bufstatus的状态信息,输出两路相位控制信号tx_pi

给gth ip核的相位插值器。相位同步控制算法软件实现框图如下图8所示。

[0111]

相位同步控制算法软件实现资源如下表1所示。

[0112]

表1相位同步控制算法软件实现资源表

[0113][0114]

表1中,top_sync为相位同步控制模块顶层模块,tx_pi_ctr0、tx_pi_ctr1为两个相位同步控制器。由表1可以看出,高速基带信号产生及相位同步模块占用资源少,相位同步控制算法硬件实现简单,易于工程化实现。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。