1.本技术涉及电子信息技术领域,尤其涉及一种处理方法、处理装置、计算设备和存储介质。

背景技术:

2.目前,在设计印制电路板(printed circuit board,pcb)叠层时,需要先确定介质层半固化片(prepreg,pp)和芯板(core)的厚度,之后在顶层(top)和底层(bottom)中间,通过重复叠加半固化片层、芯板层、信号层(signal,sig)、电源层(power,pwr)和地层(ground,gnd)的厚度,进而叠加出最终pcb板叠层的厚度。

3.通过上述方法叠加出pcb板叠层的厚度,很难达到目标厚度,如此,还需要多次调整pp和core的厚度,使得pcb板叠层的厚度达到目标厚度。而且,一旦pcb板叠层的结构有所变动,则将导致pcb板叠层的层数或厚度发生变化,此时,需要对pcb板叠层中的各个单板进行重新叠加。

4.因此,pcb板叠层的设计方法存在设计重复性高、制作效率低的问题。

技术实现要素:

5.本技术提供了一种处理方法、处理装置、计算设备和存储介质,用于提高pcb板叠层的制作效率。

6.第一方面,本技术提供了处理方法,该处理方法由计算设备执行,其中,方法包括:计算设备获取pcb板叠层中的多个介质层的总层数和多个介质层的总厚度,其中,多个介质层包括一个或多个半固化片层,以及一个或多个芯板层,半固化片层和芯板层间隔排列,比如半固化片层的下一层是芯板层,芯板层的再下一层又是半固化片层。计算设备再根据多个介质层的总层数和多个介质层的总厚度,确定多个介质层的平均厚度。根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中的半固化片层的材料和芯板层的材料,其中,材料数据表包括多个材料和多个材料分别对应的厚度。

7.上述技术方案中,计算设备通过获取pcb板叠层中的多个介质层的总层数和多个介质层的厚度,确定多个介质层的平均厚度,再结合材料数据表,确定pcb板叠层中的多个介质层的材料,将确定出的多个介质层材料提供给工程师,工程师可以根据提供的多个介质层材料制作该pcb板叠层,有助于工程师快速高效地制作pcb板叠层,进而提高工作效率,降低人工成本。

8.一种可能的设计中,计算设备获取多个介质层的总层数和多个介质层的总厚度,具体是根据pcb板叠层包括的总层数,确定多个介质层的总层数;再根据pcb板叠层包括的总厚度,和pcb板叠层中多个已知层的总厚度,确定多个介质层的总厚度,其中,多个已知层包括如下中多项:顶层、底层、表层、次外层、信号层、电源层、地层。

9.上述技术方案中,计算设备确定pcb板叠层中多个介质层的总层数和多个介质层的总厚度,有助于提高pcb板叠层的制作效率。

10.一种可能的设计中,计算设备根据多个介质层的平均厚度、材料数据表和预设比值区间,确定pcb板叠层中半固化片层的材料和芯板层的材料,其中,半固化片层的厚度和芯板层的厚度的比值在预设比值区间。

11.一种可能的设计中,计算设备在根据多个介质层的平均厚度、材料数据表和预设比值区间,确定pcb板叠层中半固化片层的材料和芯板层的材料时,具体是,计算设备确定pcb板叠层为上下对称结构,且pcb板叠层中第一电源层所在层数为奇数时,则计算设备根据平均厚度、材料数据表和厚度阈值,确定半固化片层的材料,其中,确定出的半固化片层的材料大于厚度阈值。再根据半固化片层的材料、材料数据表和预设比值区间,确定芯板层的材料,其中,第一电源层是pcb板叠层的中间两层中的上一层。

12.上述技术方案中,计算设备若确定pcb板叠层中第一电源层所在层数为奇数时,则计算设备通过平均厚度、材料数据表、厚度阈值和预设比值区间,确定半固化片层的材料和芯板层的材料,使得半固化片层的材料厚度和芯板层的材料厚度在预设比值区间,从而有助于pcb板叠层达到损耗小的效果。

13.一种可能的设计中,计算设备根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中半固化片层的材料和芯板层的材料之后,根据pcb板叠层中半固化片层的材料和芯板层的材料,对pcb板叠层进行检查,检查至少包括如下中一项或多项:检查pcb板叠层的损耗是否在预设损耗范围内;检查pcb板叠层的信号完整性是否满足预设要求;检查pcb板叠层的线宽线距是否在预设范围内。在pcb板叠层未通过检查的情况下,根据多个介质层的平均厚度和材料数据表,调整pcb板叠层中半固化片层的材料和芯板层的材料。

14.上述技术方案中,计算设备通过对pcb板叠层进行检查,能够有效的避免pcb板叠层在后期制作及使用中发生故障。

15.一种可能的设计中,计算设备所要确定的pcb板叠层中半固化片层的材料和芯板层的材料具备如下特征中的一项或多项:厚度、介电常数(dielectric constant,dk)、损耗因子(dessipation factor,df)。

16.上述技术方案中,计算设备结合介质层材料的厚度、介电常数和损耗因子确定pcb板叠层中半固化片层的材料和芯板层的材料,有助于降低pcb板叠层的损耗,提高pcb板叠层的信号完整性。

17.第二方面,本技术提供了一种处理装置,该装置包括:

18.第一处理单元,用于获取pcb板叠层中的多个介质层的总层数和多个介质层的总厚度,其中,多个介质层包括一个或多个半固化片层,以及一个或多个芯板层,半固化片层和芯板层间隔排列;第一处理单元,还用于根据多个介质层的总层数和多个介质层的总厚度,确定多个介质层的平均厚度;

19.第二处理单元,用于根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中半固化片层的材料和芯板层的材料,其中,材料数据表包括多个材料分别对应的厚度。

20.一种可能的设计中,第一处理单元在获取多个介质层的总层数和多个介质层的总厚度时,具体用于:根据pcb板叠层包括的总层数,确定多个介质层的总层数;根据pcb板叠层包括的总厚度,和pcb板叠层中多个已知层的总厚度,确定多个介质层的总厚度,其中,多个已知层包括如下中多项:顶层、底层、表层、次外层、信号层、电源层、地层。

21.一种可能的设计中,第二处理单元在根据多个介质层的平均厚度和材料数据表,

确定pcb板叠层中半固化片层的材料和芯板层的材料时,具体用于:根据多个介质层的平均厚度、材料数据表和预设比值区间,确定pcb板叠层中半固化片层的材料和芯板层的材料,其中,半固化片层的厚度和芯板层的厚度的比值在预设比值区间。

22.一种可能的设计中,第二处理单元在根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中半固化片层的材料和芯板层的材料时,具体还用于:确定pcb板叠层为上下对称结构,且pcb板叠层中第一电源层所在层数为奇数时,则根据平均厚度、材料数据表和厚度阈值,确定半固化片层的材料,其中,确定出的半固化片层的材料大于厚度阈值。再根据半固化片层的材料、材料数据表和预设比值区间,确定芯板层的材料,其中,第一电源层是pcb板叠层的中间两层中的上一层。

23.一种可能的设计中,该装置还包括检查单元,在第二处理单元根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中半固化片层的材料和芯板层的材料之后,检查单元用于根据pcb板叠层中半固化片层的材料和芯板层的材料,对pcb板叠层进行检查,检查至少包括如下中一项或多项:检查pcb板叠层的损耗是否在预设损耗范围内;检查pcb板叠层的信号完整性是否满足预设要求;检查pcb板叠层的线宽线距是否在预设范围内。在pcb板叠层未通过检查的情况下,第二处理单元根据多个介质层的平均厚度和材料数据表,调整pcb板叠层中半固化片层的材料和芯板层的材料。

24.一种可能的设计中,该装置所要确定的pcb板叠层中半固化片层的材料和芯板层的材料,具备如下特征中的一项或多项:厚度、介电常数、损耗因子。

25.第三方面,本技术还提供一种计算设备,包括:

26.存储器,用于存储程序指令;

27.处理器,用于调用存储器中存储的程序指令,按照获得的程序执行上述处理方法。

28.第四方面,本技术还提供一种存储介质,包括计算机可读指令,当计算机读取并执行计算机可读指令时,使得计算机执行上述处理方法。

29.第五方面,本技术还提供一种包括指令的计算机程序产品,当其在计算机上运行时,使得计算机执行上述处理方法。

30.上述第二方面至第五方面中任一方面可以达到的技术效果可以参照上述第一方面中有益效果的描述,此处不再重复赘述。

附图说明

31.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简要介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

32.图1为本技术实施例提供的一种适用的计算设备架构图;

33.图2为本技术实施例提供的一种处理方法流程示意图;

34.图3为本技术实施例提供的一种pcb板叠层结构示意图;

35.图4为本技术实施例提供的一种处理方法完成流程示意图;

36.图5为本技术实施例提供的一种pcb板叠层示意图;

37.图6为本技术实施例提供的一种处理装置的结构示意图。

具体实施方式

38.为了使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术作进一步地详细描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本技术保护的范围。

39.图1示例性的示出本技术实施例提供的一种适用的计算设备架构图,如图1所示,该计算设备100可以包括通信接口110、处理器120和存储器130,其中存储器130用于存储程序指令和/或数据。通信接口110用于获取pcb板叠层的信息,示例性的,pcb板叠层的信息包括pcb板叠层的结构、pcb板叠层的总层数和总厚度、已知层的总层数和总厚度。比如计算设备是电脑,工程师通过键盘输入上述pcb板叠层的信息,使得计算设备100通过通信接口110获取到pcb板叠层的信息。

40.处理器120可能和存储器130协同操作。处理器120可能执行存储器130中存储的程序指令,存储器130中存储的指令或程序被执行时,该处理器120用于根据pcb板叠层的信息,获取pcb板叠层中多个介质层的平均厚度,以及确定pcb板叠层中多个介质层的材料,其中pcb板叠层中多个介质层的材料包括固化片层的材料和芯板层的材料。

41.存储器130和处理器120耦合。本技术实施例中的耦合是计算设备、单元或模块之间的间接耦合或通信连接,可以是电性,机械或其它的形式,用于计算设备、单元或模块之间的信息交互。存储器130中的至少一个可以包括于处理器120中。

42.可选的,计算设备100还包括显示器140,显示器140用于显示pcb板叠层中的半固化片层和芯板层的材料。工程师基于显示器140中显示的半固化片层和芯板层的材料,确定制作pcb板叠层所需要的半固化片层和芯板层的材料。

43.在本技术实施例中,通信接口110可以是收发器、电路、总线、模块或其它类型的通信接口。在本技术实施例中,通信接口为收发器时,收发器可以包括独立的接收器、独立的发射器;也可以集成收发功能的收发器、或者是通信接口。

44.计算设备100还可以包括通信线路150。其中,通信接口110、处理器120以及存储器130可以通过通信线路150相互连接;通信线路150可以是外设部件互连标准(peripheral component interconnect,pci)总线或扩展工业标准结构(extended industry standard architecture,eisa)总线等。通信线路150可以分为地址总线、数据总线、控制总线等。为便于表示,图1中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。

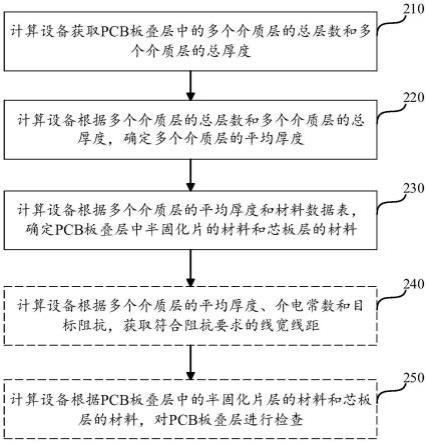

45.基于图1所示意的计算设备架构图,图2示例性的示出本技术实施例提供的一种处理方法示意图。

46.如图2所示,具体步骤包括:

47.步骤210,计算设备获取pcb板叠层中的多个介质层的总层数和多个介质层的总厚度,其中,多个介质层包括一个或多个半固化片层,以及一个或多个芯板层,半固化片层和芯板层间隔排列。

48.在上述步骤210中,计算设备根据pcb板叠层的总层数,确定多个介质层的总层数。

49.在一种可能实现中,计算设备根据pcb板叠层的总厚度,和pcb板叠层中多个已知层的总厚度,确定多个介质层的总厚度,其中,多个已知层包括如下中多项:顶层、底层、表层、次外层、信号层、电源层、地层。

50.图3示例性的示出一种pcb板叠层的结构示意图,根据图3所示,该pcb板叠层为对称结构,总层数为m层,该pcb板叠层中具有多个已知层,该多个已知层的层数和厚度均为已知,其中,多个已知层包括顶层、底层、表层、次外层、信号层、电源层、地层。

51.如图3所示,顶层和底层共有2层,表层共有2层,次外层共有2层,电源层共有x层,信号层和地层共有(m-x-6)层。介质层存在于pcb板叠层的第4层和第(m-3)层中间的每两个已知层的中间。例如,图3中的第4层的地层和第5层的信号层中间存在一个介质层、第5层的信号层和第6层的信号层中间存在一个介质层、还可以是地层和电源层中间存在一个介质层、电源层和电源层中间存在一个介质层。因此,m层的pcb板叠层中,多个介质层的总层数为(m-3-4)层,即:计算设备根据pcb板叠层的总层数m层,确定多个介质层的总层数为(m-7)层。

52.如图3所示,pcb板叠层的总厚度为hmil,顶层为1.8mil,底层的为1.8mil,表层为1.2mil,信号层和地层均为1.8mil,电源层为2.4mil,考虑到pcb板叠层的表层损耗较大,需要用更宽的走线来减小损耗,因此为了控制表层线宽线距,将次外层半固化片层设置为ymil厚的预设优选厚度,因此,已知层的总厚度为(2.4 3.6 2y 2.4x 1.2(m-x-6))mil,即:计算设备获取已知层的总厚度为(6 2y 2.4x 1.2(m-x-6))mil。

53.计算设备根据pcb板叠层的总厚度hmil和多个已知层的总厚度(6 2y 2.4x 1.2(m-x-6))mil,确定多个介质层的总厚度为(h-6-2y-2.4x-1.2(m-x-6))mil。

54.步骤220,计算设备根据多个介质层的总层数和多个介质层的总厚度,确定多个介质层的平均厚度。

55.可选的,计算设备将多个介质层的总厚度,与多个介质层的总层数的比值,作为多个介质层的平均厚度。

56.继续参照图3所示,计算设备根据多个介质层的总层数(m-7)层,和多个介质层的总厚度(h-6-2y-2.4x-1.2(m-x-6))mil,确定多个介质层的平均厚度b为

57.步骤230,计算设备根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中半固化片层的材料和芯板层的材料,其中,材料数据表包括多个材料和多个材料分别对应的厚度。

58.在上述步骤230中,计算设备根据多个介质层的平均厚度、材料数据表和预设比值区间,确定pcb板叠层中半固化片层的材料和芯板层的材料,其中,半固化片层的厚度和芯板层的厚度的比值在预设比值区间,如此能够使得当半固化片层和芯板层为同材料同频率时,pcb板叠层的损耗达到最小。其中,预设比值区间可以是根据各板厂回板测试经验设定的,比如预设比值区间为[3/4,6/4]。

[0059]

进一步地,计算设备在根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中半固化片层的材料和芯板层的材料时,还需确定pcb板叠层中第一电源层所在层数为奇数还是偶数,其中,pcb板叠层的中间两层具体可以是两个电源层,第一电源层是pcb板叠层的中间两个电源层中的上一层。

[0060]

一个示例中,14层的pcb板叠层的中间两个电源层分别位于第7层和第8层,因此该pcb板叠层的第一电源层所在层数为7,即该pcb板叠层的第一电源层所在层数为奇数。

[0061]

另一个示例中,12层的pcb板叠层的中间两个电源层分别位于第6层和第7层,因此该pcb板叠层的第一电源层所在层数为6,即该pcb板叠层的第一电源层所在层数为偶数。

[0062]

进一步地,计算设备确定pcb板叠层中半固化片层的材料和芯板层的材料时,具体情况为以下两种:

[0063]

情况1:若pcb板叠层为上下对称结构,且pcb板叠层中第一电源层所在层数为奇数,则两个电源层中间的介质层为半固化片层。计算设备根据多个介质层的平均厚度、材料数据表和厚度阈值,确定半固化片层的材料,其中,半固化片层的材料大于厚度阈值,其中,厚度阈值可以是根据安规要求设定的,预厚度阈值比如是4mil。这是由于半固化片层压合后会导致流胶厚度减小,电源层之间距离太近可能会引起短路,因此根据安规要求,两个电源层之间的半固化片层的厚度必须大于厚度阈值。进而计算设备根据半固化片层的材料厚度、材料数据表和预设比值区间,确定芯板层的材料。

[0064]

情况2:若pcb板叠层为上下对称结构,且pcb板叠层中第一电源层所在层数为偶数,则两个电源层中间的介质层为芯板层。由于在安规要求中,度芯板层的厚度没有最低要求,因此,若两个电源层的中间介质层为芯板层,则计算设备只需根据多个介质层的平均厚度、材料数据表和与预设比值区间确定半固化层和芯板层的材料。

[0065]

可选的,计算设备在确定pcb板叠层中半固化片层的材料和芯板层的材料之后,还包括步骤240:计算设备根据多个介质层的平均厚度、介电常数和目标阻抗,获取符合阻抗要求的线宽线距。

[0066]

在上述步骤240中,计算设备根据pcb板叠层中介质层厚度、介电常数和目标阻抗,获取最符合阻抗要求的线宽线距,其原理如下:

[0067]

微带线:

[0068]

带状线:

[0069]

其中,z0表示特性阻抗(单位为:ω),h表示信号线与平面之间的介质厚度(单位为:mil),w表示线宽(单位为:mil),b表示平面之间的距离(单位为:mil),t表示金属厚度(单位为:mil),εr表示介电常数。

[0070]

可选的,在计算设备根据多个介质层的平均厚度、介电常数和目标阻抗,获取符合阻抗要求的线宽线距之后,还包括步骤250:计算设备根据pcb板叠层中半固化片层的材料和芯板层的材料,对pcb板叠层进行检查,其中,检查包括如下中一项或多项:检查pcb板叠层的损耗是否在预设损耗范围内;检查pcb板叠层的信号完整性是否满足预设要求;检查pcb板叠层的线宽线距是否在预设范围内。

[0071]

示例性的,计算设备对pcb板叠层按照如下步骤a至c执行检查:

[0072]

步骤a,计算设备获取pcb板叠层在高速信号传输线在频率为8g/16g/12g时的损耗,对照损耗表,检查pcb板叠层的损耗是否在预设损耗范围内。

[0073]

步骤b,计算设备根据pcb板叠层检查表,检查pcb板叠层中的信号完整性是否满足预设要求。

[0074]

步骤c,计算设备检查pcb板叠层的线宽线距是否在预设范围内。

[0075]

其中,所述材料具备如下特征中的一项或多项:厚度、介电常数以及损耗因子。

[0076]

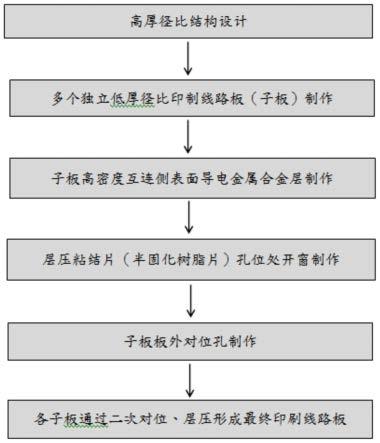

为了便于理解本方案,图4示例性的示出本技术实施例提供的一种处理方法完整流程示意图。

[0077]

如图4所示,具体步骤包括:

[0078]

步骤410,计算设备获取pcb板叠层的总厚度和总层数,以及pcb板叠层中已知层的总厚度和总层数。具体可参见步骤210中的描述。

[0079]

步骤420,计算设备获取pcb板叠层中多个介质层的总厚度和总层数。具体可参见步骤210中的描述。

[0080]

步骤430,计算设备获取pcb板叠层中多个介质层的平均厚度。具体可参见步骤220中的描述。

[0081]

步骤440,计算设备判断pcb板叠层中第一电源层所在层数是否为奇数,若pcb板叠层中第一电源层所在层数为奇数,则执行步骤450,若pcb板叠层中第一电源层所在层数不是奇数,即pcb板叠层中第一电源层所在层数为偶数,则执行步骤460。具体可参见步骤230中的描述。

[0082]

步骤450,计算设备确定pp层的材料厚度,进而确定core层的材料厚度。具体可参见步骤230中的描述。

[0083]

步骤460,计算设备确定pp层和core层的材料。具体可参见步骤230中的描述。

[0084]

步骤470,计算设备获取pcb板叠层的线宽线距。具体可参见步骤240中的描述。

[0085]

步骤480,计算设备检查pcb板叠层。具体可参见步骤250中的描述。

[0086]

下面举一个具体的例子介绍上述pcb板叠层的设计方法,图5示例性的示出一种pcb板叠层的示意图。

[0087]

如图5所示,计算设备获取到pcb板叠层的信息:该pcb板叠层为对称结构,共有18层,其中,表层共有2层,顶层和底层共有2层,次外层共有2层,电源层共有4层,信号层和地层共8层,该pcb板叠层的目标厚度为82.2mil,其中,表层的每层厚度为1.2mil,顶层厚度和底层厚度均为1.8mil,次外层的每层厚度为4mil,电源层的每层厚度为2.4mil,信号层和地层的每层厚度为1.2mil。

[0088]

计算设备根据获取到的pcb板叠层的信息,根据步骤210,进而获取到pcb板叠层的多个介质层的总层数为11层,多个介质层的总厚度为51.8mil。根据步骤220,获取到11个介质层的平均厚度约为4.7mil。即:若想达到目标厚度,则半固化片层和芯板层的每层厚度约为4.7mil。由于该pcb板叠层中的中间两层的电源层所在层数为9层和10层,即:该pcb板叠层中第一电源层所在层数为奇数层,则第9层的电源层和第10层的电源层的中间介质层为半固化片层。根据安规要求,半固化片层的厚度必须大于厚度阈值。在确定半固化片层和芯板层材料的同时,还需要使pcb板叠层满足损耗小,信号完整性质量高的要求,因此,需要保证半固化片层的材料厚度大于厚度阈值,且半固化片层厚度与芯板层厚度的比值在预设比值区间。本实施例中,厚度阈值为4mil,预设比值为5/4,因此,计算设备确定半固化片层的材料厚度大于4mil,且半固化片层厚度与芯板层厚度的比值为5/4的同时,对照材料数据表确定半固化片层和芯板层的材料。如表1所示,是一种常用的介质层材料数据表。

[0089]

表1

[0090]

prepreg it-180abs

[0091][0092]

core it-180atc

[0093][0094]

计算设备根据获取到的介质层的平均厚度,并结合安规要求,确定材料类型为2116、厚度为5.1mil的材料为该pcb板叠层中半固化片层所用材料,从而确定材料厚度为0.0040in的材料为该pcb板叠层中芯板层所用材料,即:所选用的芯板层的材料厚度为4mil。需要注意的是:同一厚度的介质类型也有多种类型,如表1所示,在芯板层材料中,厚度为0.0040in的材料有两种,在此情况下,优选dk、df更小,价格更优的型号。

[0095]

计算设备确定半固化片层和芯板层的材料之后,根据步骤240中所述的原理,获取最符合阻抗要求的线宽线距。最后计算设备对pcb板叠层进行步骤250中所述的检查。

[0096]

在上述计算设备对pcb板叠层进行步骤250中所述的一项或多项检查时,具体检查结果有以下两种:

[0097]

检查结果1:pcb板叠层通过检查,工程师可以根据计算设备提供的多个介质层材料制作pcb板叠层。

[0098]

检查结果2:pcb板叠层未通过检查,计算设备根据获取到的介质层的平均厚度,并结合安规要求,重新确定多个介质层的材料。例如:上述计算设备确定出pcb板叠层中半固化片层和芯板层的材料,但是pcb板叠层未通过步骤250中所述的一项或多项检查,因此,计算设备根据获取到的介质层的平均厚度,并结合安规要求,重新确定材料类型为2116、厚度为4.6mil的材料为该pcb板叠层中半固化片层所用材料,从而确定材料厚度为0.0035in的材料为该pcb板叠层中芯板层所用材料,即:所选用的芯板层的材料厚度为3.5mil。计算设

备重新确定半固化片层和芯板层的材料之后,再依次按照步骤240和步骤250所述,获取最符合阻抗要求的线宽线距,检查pcb板叠层是否满足要求。

[0099]

本技术提供了一种处理方法,该处理方法包括:计算设备获取pcb板叠层中的多个介质层的总层数和多个介质层的总厚度,其中,多个介质层包括一个或多个半固化片层,以及一个或多个芯板层,半固化片层和芯板层间隔排列。再根据多个介质层的总层数和多个介质层的总厚度,确定多个介质层的平均厚度。进而根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中半固化片层的材料和芯板层的材料,其中,材料数据表包括多个材料和多个材料分别对应的厚度。计算设备通过获取pcb板叠层中的多个介质层的总层数和多个介质层的厚度,确定多个介质层的平均厚度,再结合材料数据表,确定pcb板叠层中的多个介质层的材料,将确定出的多个介质层材料提供给工程师,工程师可以根据提供的多个介质层材料制作该pcb板叠层,有助于工程师快速高效地制作pcb板叠层,进而提高工作效率,降低人工成本。

[0100]

针对上述方法流程,本技术实施例还提供一种处理装置,该装置用于实现图2或图4示出的方法。

[0101]

图6示例性的示出了本技术实施例提供的一种处理装置的结构示意图。

[0102]

如图6所示,该装置具体包括:

[0103]

第一处理单元610,用于获取pcb板叠层中的多个介质层的总层数和多个介质层的总厚度,其中,多个介质层包括一个或多个半固化片层,以及一个或多个芯板层,半固化片层和芯板层间隔排列。

[0104]

所述第一处理单元610,还用于根据多个介质层的总层数和多个介质层的总厚度,确定多个介质层的平均厚度。

[0105]

第二处理单元620,用于根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中半固化片层的材料和芯板层的材料,其中,材料数据表包括多个材料分别对应的厚度。

[0106]

一种可选地实施方式中,第一处理单元610在获取多个介质层的总层数和多个介质层的总厚度时,具体用于:根据pcb板叠层包括的总层数,确定多个介质层的总层数;根据pcb板叠层包括的总厚度,和pcb板叠层中多个已知层的总厚度,确定多个介质层的总厚度,其中,多个已知层包括如下中多项:顶层、底层、表层、次外层、信号层、电源层、地层。

[0107]

一种可选地实施方式中,第二处理单元620在根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中半固化片层的材料和芯板层的材料时,具体用于:根据多个介质层的平均厚度、材料数据表和预设比值区间,确定多个介质层的材料,其中,半固化片层的厚度和芯板层的厚度的比值在预设比值区间。

[0108]

一种可选地实施方式中,第二处理单元620在根据多个介质层的平均厚度和材料数据表,确定所述pcb板叠层中所述半固化片层的材料和所述芯板层的材料时,具体还用于:在pcb板叠层为上下对称结构,且pcb板叠层中第一电源层所在层数为奇数时,根据平均厚度、材料数据表和厚度阈值,确定半固化片层的材料,半固化片层的材料大于厚度阈值。再根据半固化片层的材料、材料数据表和预设比值区间,确定芯板层的材料,其中,第一电源层是pcb板叠层的中间两层中的上一层。

[0109]

一种可选地实施方式中,在第二处理单元620根据多个介质层的平均厚度和材料数据表,确定pcb板叠层中所述半固化片层的材料和所述芯板层的材料之后,还包括检查单

元630。

[0110]

检查单元630,用于根据述pcb板叠层中所述半固化片层的材料和所述芯板层的材料,对pcb板叠层进行检查,检查至少包括如下中一项或多项:检查pcb板叠层的损耗是否在预设损耗范围内;检查pcb板叠层的信号完整性是否满足预设要求;检查pcb板叠层的线宽线距是否在预设范围内。

[0111]

若检查单元630所检查的pcb板叠层未通过检查,则第二处理单元620根据多个介质层的平均厚度和材料数据表,调整pcb板叠层中半固化片层的材料和芯板层的材料。

[0112]

一种可选地实施方式中,所要确定的多个介质层的材料特征包括如下中特征:厚度、介电常数、损耗因子。

[0113]

基于相同的技术构思,本技术实施例还提供了一种计算设备,包括:

[0114]

存储器,用于存储程序指令;

[0115]

处理器,用于调用存储器中存储的程序指令,按照获得的程序执行上述处理方法。

[0116]

基于相同的技术构思,本技术实施例还提供了一种存储介质,包括计算机可读指令,当计算机读取并执行计算机可读指令时,使得计算机执行上述处理方法。

[0117]

基于相同的技术构思,本技术实施例还提供了一种计算机程序产品,包括计算机可读指令,当计算机读取并执行计算机可读指令时,使得计算机执行上述处理方法。

[0118]

本领域内的技术人员应明白,本技术的实施例可提供为方法、系统、或计算机程序产品。因此,本技术可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本技术可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

[0119]

本技术是参照根据本技术的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

[0120]

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

[0121]

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0122]

显然,本领域的技术人员可以对本技术进行各种改动和变型而不脱离本技术的精神和范围。这样,倘若本技术的这些修改和变型属于本技术权利要求及其等同技术的范围之内,则本技术也意图包含这些改动和变型在内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。